MOSFETs and other switching devices may fail due to various factors. Accurately knowing device ratings and operating conditions is essential, and circuit-level factors that can cause failure must be considered. This article summarizes common MOSFET failure mechanisms.

What is SOA (Safety Operation Area)?

SOA stands for Safety Operation Area. To use a MOSFET safely, it must operate within its SOA; operating outside this area can cause damage. A failure caused by operating outside the SOA is called an SOA failure.

SOA Axes and Factors

The SOA is plotted with drain current ID on the vertical axis and drain-source voltage VDS on the horizontal axis. VDS, ID, their product (power dissipation PD), and the secondary breakdown region determine the safe operating range. The applied pulse width PW is also an important factor. The SOA is typically divided into regions (1) through (5) as shown in the figure.

Region (1): RDS(on)-limited region

This region is where ID is limited by the MOSFET on-resistance RDS(on), even if the applied VDS is below the absolute maximum rating. According to Ohm's law I = V / R, the current can only reach the red line position in the plot. Example is shown for VGS = 10 V.

Region (2): Peak pulsed current limit (IDP)

The green line for region (2) is the absolute maximum peak pulsed drain current IDP specified in the datasheet. This absolute maximum must not be exceeded; operating above it can cause damage because it is outside the guaranteed operating range.

Region (3): Thermal limit

This region is constrained by allowable power dissipation PD and is influenced by pulse width PW and transient thermal resistance. If operated within this region, junction temperature Tj normally will not exceed TjMAX. Note that this boundary depends on ambient temperature, mounting conditions, and heat-sinking. When using MOSFETs as switches, transient states with high voltage and high current must also be checked against this thermal limit.

Region (4): Secondary breakdown

Secondary breakdown occurs when local internal regions of the device conduct excessive current under high VDS, causing damage. The secondary breakdown boundary prevents this condition. Like the thermal limit, this region is affected by ambient temperature and other factors.

Region (5): VDSS-limited region

This region is limited by the MOSFET drain-source voltage absolute maximum rating VDSS. Exceeding this rating can cause avalanche breakdown and damage. Note that parasitic inductance and transient energy can cause instantaneous voltage spikes that exceed VDSS.

Avalanche Breakdown

Avalanche breakdown occurs when the applied VDS exceeds the absolute maximum BVDSS. Under a high electric field, free electrons gain sufficient energy to cause impact ionization and generate electron-hole pairs. This avalanche multiplication of carriers is called avalanche breakdown. During avalanche, the reverse current flowing through the MOSFET intrinsic diode is called the avalanche current IAS.

Avalanche Failure Modes

Short-circuit caused by avalanche

IAS flows through the MOSFET internal base resistor RB. This creates a base-emitter potential VBE across the parasitic bipolar transistor. If VBE becomes large enough, the parasitic bipolar transistor may turn on. Once that bipolar device conducts, excessive current can flow and the MOSFET may fail as a short.

Thermal damage caused by avalanche

In addition to short-circuit failure caused by parasitic bipolar conduction, thermal damage can occur due to conductive losses during avalanche. When the device is in breakdown, avalanche current flows while BVDSS is applied; the product of voltage and current is power dissipation. The energy absorbed during avalanche is called avalanche energy EAS.

Datasheets for MOSFETs with avalanche robustness specify absolute maximum values for IAS and EAS. In environments where avalanche current may occur, both IAS and EAS must be considered and operation kept within datasheet limits.

Examples of events that can trigger avalanche include flyback voltage when a MOSFET in a flyback converter turns off and surge voltages caused by parasitic inductance. Mitigations include designing to reduce flyback voltage or selecting MOSFETs with higher voltage rating, using packages with shorter leads to reduce parasitic inductance, or improving PCB layout to reduce parasitic inductance.

dV/dt-Induced Failure

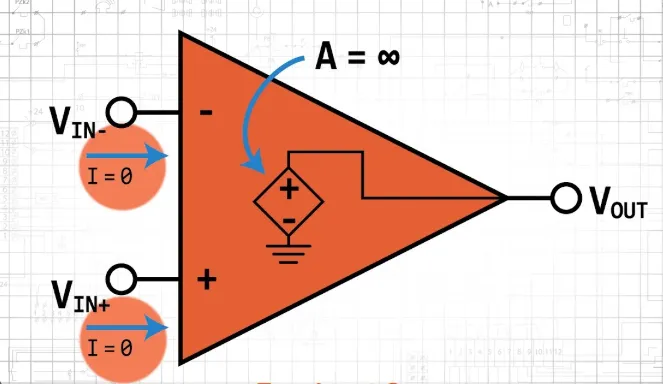

dV/dt failure occurs when the transient charging current of the MOSFET parasitic capacitance Cds during turn-off flows through the base resistor RB, generating a base-emitter potential VBE on the parasitic bipolar transistor and causing it to turn on. This leads to a short and failure. Generally, the larger (faster) the dV/dt, the larger the induced VBE and the greater the risk of parasitic bipolar conduction and failure.

dV/dt, Reverse Recovery, and Double-Pulse Testing

In inverter circuits and half-bridge/temporal-Pole PFC topologies, reverse recovery current Irr of diodes can flow through MOSFETs. The dV/dt driven by this reverse recovery can cause parasitic bipolar conduction. The relationship between dV/dt failure and reverse recovery characteristics is evaluated using a double-pulse test.

For details on the double-pulse test, refer to R-classroom basic knowledge: "Evaluating MOSFET reverse recovery with double-pulse test".

The following simulation compares dV/dt and reverse recovery. MOSFET1 to MOSFET3 are driven with identical gate resistor RG and supply VDD; only their reverse recovery characteristics differ. The plots show Q1 switching from freewheeling to reverse recovery, with drain-source voltage VDS and diode current ID recorded.

In general, a MOSFET with poorer reverse recovery (higher Irr and longer trr) produces a steeper dV/dt. The capacitive transient current is I = C × dV/dt, so a sharper dV/dt corresponds to a larger transient current. Even when di/dt of Irr is set the same, a steeper di/dt can increase dV/dt. Therefore, in bridge circuits, MOSFETs with poorer reverse recovery present a higher risk of dV/dt-induced failure.

Summary

This article covered MOSFET SOA failures, avalanche failures, and dV/dt-induced failures. To use MOSFETs safely, first never exceed absolute maximum ratings in the datasheet. In addition, understanding these failure mechanisms should inform circuit design and operating condition settings.