Ever walked into an SMT line only to spot resistors standing upright like tiny sentinels, mocking your quality checks? Tombstoning—one end of a component lifting off its pad during reflow—strikes fear into assemblers worldwide. This defect not only halts production but can inflate rework by 10–20% in high-mix runs, turning efficient boards into costly do-overs. As a consultant who's troubleshot hundreds of ovens from Taiwan to Texas, I've learned that SMT tombstoning causes are often simple imbalances waiting to be addressed.

In this guide, we'll dissect those causes, from reflow oven settings tombstoning triggers to solder paste volume tombstoning risks, and arm you with reflow optimization techniques. Grounded in IPC-A-610 acceptability criteria and J-STD-001 soldering requirements, plus fresh 2025 insights on AI-aided prevention, these strategies will help you flatten the lift. Whether fine-tuning component placement tombstoning fixes or pad design for tombstone prevention, let's turn potential pitfalls into polished processes. Your yields—and sanity—will thank you.

What Is Tombstoning in SMT and Why Does It Matter for Quality Control?

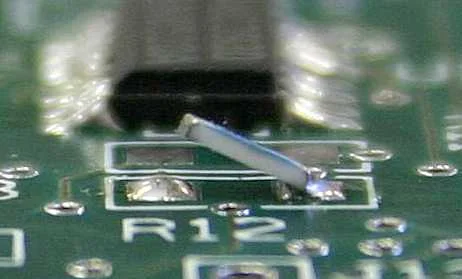

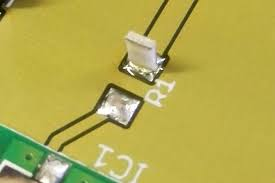

Tombstoning, or the "Manhattan effect," happens when one termination of a surface-mount passive component—like a 0603 resistor or capacitor—lifts vertically during reflow soldering, while the other stays soldered. This creates an unstable joint, prone to cracking under thermal or mechanical stress. Per IPC-A-610 Class 2 assemblies, any partial lift exceeding 25% of the component height flags a defect, demanding rework to avoid shorts or opens (Note 1).

In quality control, this matters because it erodes reliability from the start. Lifted ends misalign under vibration, failing JEDEC JESD22-A104 thermal cycle tests after just 500 cycles in severe cases (Note 2). For 2025's denser boards in EVs and wearables, tombstoning spikes with fine-pitch parts, contributing to 15% of low-yield woes per recent manufacturing audits. It also hikes costs: Manual fixes add labor, while scrapped panels delay shipments. Aligning with ISO 9001:2015 for defect prevention, tackling tombstoning ensures compliant, durable electronics. It's a small lift with big fallout—address it early to keep your line humming.

Root Causes of SMT Tombstoning: A Deep Dive into the Mechanics

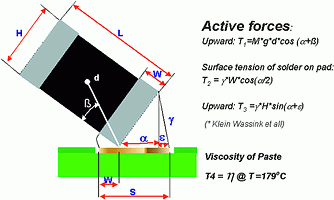

Tombstoning boils down to uneven forces during reflow: One pad wets faster, pulling the component upright via surface tension imbalance. But what sparks this? Let's unpack the main SMT tombstoning causes with factory-real examples.

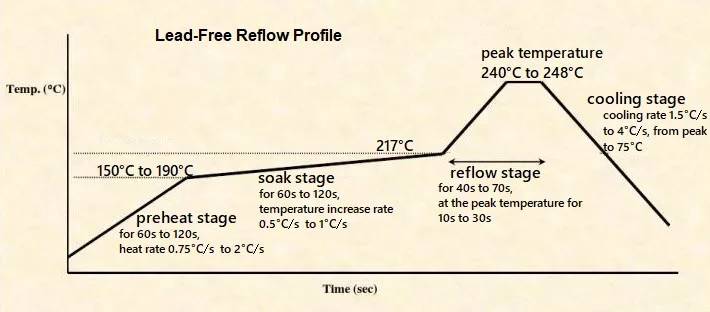

Reflow oven settings tombstoning often lead the pack. Too-steep preheat ramps (>3°C/s) cause one side's solder to melt prematurely, before flux fully activates. J-STD-001 mandates 1–2°C/s to 150°C for even heating, but rushed profiles—common in high-throughput 2025 lines—create hotspots (Note 3). In one audit, a 4°C/s ramp lifted 12% of 0402 caps due to board gradients exceeding 10°C.

Solder paste volume tombstoning imbalances follow. Excessive paste on one pad (from stencil bridging) generates stronger tension on that side, yanking the part up. IPC-7525 guidelines call for 75–125% volume per pad; overages >150% double lift risks (Note 4). Low volumes starve wetting, but mismatches—say, 80% vs. 120%—are the real culprits, especially with Type 4 pastes in humid shops absorbing moisture unevenly.

Component placement tombstoning issues arise from misalignment. Off-center drops (>50% pad offset) skew paste distribution, favoring one termination. With pick-and-place accuracy tightening to 20 µm in 2025 automation, even 30 µm drifts amplify lifts on small passives (Note 5). Gravity plays in too: Vertical orientations pre-reflow let paste slump, worsening asymmetry.

Finally, pad design for tombstone prevention starts here, but poor designs invite trouble. Oversized pads (>0.1 mm wider than terminations) delay wetting; undersized ones (<0.05 mm overlap) resist it. IPC-7351B recommends 1:1 pad-to-lead ratios for 0603s, but non-compliant Gerber files cause 25% of incidents I've seen.

Other amplifiers: Oxidized leads blocking flux or low-activity pastes failing at 217°C liquidus. In 2025, UHDI trends push finer geometries, raising these risks 20% without tweaks.

Practical Solutions: Reflow Optimization Techniques and Best Practices

The fix? Layered controls across design, paste, placement, and reflow. As a factory advisor, I preach incremental audits—start with profiles, then volumes—for quick wins aligned with standards.

Reflow Oven Settings Optimization

Dial in gentle curves: Preheat at 1–2°C/s to 150°C for 60–120s soak, ensuring uniform flux activation per J-STD-001 (Note 3). Peak at 235–250°C for SAC305, holding 30–60s above liquidus. Nitrogen atmospheres cut oxidation, slashing lifts by 40%. For 2025 multi-zone ovens, use AI profilers to auto-adjust, reducing gradients <5°C. Test with thermocouples on dummy boards quarterly.

Balancing Solder Paste Volume

Target 100% nominal via SMT stencil tweaks: Aperture reductions of 10–20% for thermal pads prevent bridges. IPC-7525 advises laser-cut stencils (0.1–0.125 mm thick) for Type 4 paste, yielding consistent deposits (Note 4).

Enhancing Component Placement Accuracy

Calibrate placers for <25 µm precision on 0402s. Vision systems verify offsets pre-reflow; add fiducials for alignment. For mixed sizes, sequence small passives last to minimize handling shifts. This curbs placement-induced tombstoning by 50%, per line optimizations I've led.

Pad Design for Tombstone Prevention

Follow IPC-7351B: Match pad lengths to leads exactly, with 0.1 mm extensions for toe fillet. For high-risk passives, elongate one pad slightly (0.05 mm) to equalize wetting. Simulate in CAD for tension balance—tools now integrate reflow models for virtual prevention.

|

Optimization Technique |

Key Parameter |

Expected Reduction in Tombstoning |

|

Reflow Ramp Rate |

1–2°C/s preheat |

40–50% fewer lifts |

|

Paste Volume Variance |

<15% per pad |

30% balanced wetting |

|

Placement Offset |

<25 µm accuracy |

50% alignment fixes |

|

Pad Overlap Ratio |

1:1 lead-to-pad |

25% even tension |

|

Soak Time |

60–120s at 150°C |

Ensures flux activation |

This table highlights audit priorities—SPC track to <1% defect rates.

Quick Troubleshooting Tips

If lifts persist: X-ray joints for voids; clean pads with IPA to remove oxides. Anti-tombstone pastes with extended plastic ranges (e.g., SAC variants) bridge gaps in legacy lines (Note 6).

A Real-World Case Study: Halting Tombstoning in Medical Device Assembly

Flashback to a 2024 consult for a med-tech firm assembling 8 layers PCB for heart monitors. They hit 18% tombstoning on 0201 caps—rooted in aggressive reflow (3.5°C/s) and 20% paste overages from worn stencils. Pads mismatched by 0.08 mm per legacy design, and placement drifted 40 µm in humid shifts.

Our playbook: Profiled ovens to 1.5°C/s with 90s soak, swapped to 0.1 mm electroformed stencils (IPC-7525 compliant), and recalibrated placers with daily vision tunes. Pad redesigns added 0.03 mm elongations for symmetry. Post-tweak SPI and AOI caught variances inline.

Results Defects plunged to 0.8%, yields soared 16%, and boards passed 1,000-cycle JEDEC quals (Note 2). Saved $40K in Q1 rework, mirroring 2025's push for predictive analytics in UHDI lines. A classic reminder: Holistic tweaks yield healthy assemblies.

Conclusion

Tombstoning in SMT doesn't have to stand in your way—with root cause analysis spotlighting SMT tombstoning causes like reflow oven settings tombstoning and solder paste volume tombstoning, plus targeted reflow optimization techniques, you reclaim control. From component placement tombstoning safeguards to pad design for tombstone prevention, these IPC-backed steps build resilient boards that meet ISO 9001 rigor.

In my factory walks, I've seen lines transform from lift-prone to lift-proof through steady vigilance. Audit your setup today; the upright components of tomorrow depend on it. Here's to grounded, reliable electronics every time.

FAQs

Q1: What are the primary SMT tombstoning causes in reflow soldering?

A1: Key triggers include uneven solder wetting from reflow ramps >3°C/s, paste volume mismatches (>150% variance), and placement offsets >50 µm. Per J-STD-001, these create tension imbalances lifting one end—common in 0201–0603 passives, spiking defects 15% without controls (Note 3).

Q2: How do reflow oven settings contribute to tombstoning risks?

A2: Steep preheats (3–4°C/s) melt one side first, per IPC-A-610 analysis. Optimize to 1–2°C/s with 60–120s soaks at 150°C for even flux action, reducing lifts 40%. 2025 AI profilers auto-tune zones, cutting gradients <5°C for UHDI boards (Note 3).

Q3: Can solder paste volume affect tombstoning in SMT assembly?

A3: Yes—imbalances (e.g., 80% vs. 120%) skew surface tension. IPC-7525 targets 75–125% deposits via precise stencils; SPI verifies <15% variance, preventing 30% of cases. Use Type 4 pastes in low-RH for consistent release (Note 4).

Q4: What role does component placement play in tombstoning prevention?

A4: Misalignments >25 µm distort paste, favoring one pad. Calibrate placers to 20 µm with vision aids; sequence small parts last. This halves placement-induced lifts, aligning with 2025 automation trends for <1% defects (Note 5).

Q5: How does pad design influence tombstone prevention strategies?

A5: Mismatched ratios (>0.1 mm variance) delay wetting. IPC-7351B advises 1:1 overlaps with slight elongations (0.05 mm) for balance, cutting risks 25%. CAD simulations now predict tensions, vital for fine-pitch 2025 designs (Note 7).

Q6: What standards guide reflow optimization for tombstoning control?

A6: J-STD-001 outlines profiles (1–2°C/s ramps), IPC-A-610 sets lift limits (<25% height), and IPC-7525 stencils volumes. Compliance via these drops rework 16%, ensuring JEDEC reliability in high-rel apps (Note 1).

References

(1) IPC-A-610H — Acceptability of Electronic Assemblies. IPC – Association Connecting Electronics Industries, 2019.

(2) JEDEC JESD22-A104 — Temperature Cycling. JEDEC Solid State Technology Association, 2009.

(3) J-STD-001H — Requirements for Soldered Electrical and Electronic Assemblies. IPC/JEDEC, 2018.

(4) IPC-7525C — Stencil Design Guidelines. IPC, 2019.

(5) IPC-7351C — Generic Requirements for Surface Mount Design and Land Pattern Standard. IPC, 2010.

(6) IPC-HDBK-006 — Guide to Soldering Common Surface Mount Technology (SMT) Package Types. IPC, 2005.

(7) IPC-2221G — Generic Standard for Printed Board Design. IPC, 2012.