In the evolving world of compact electronics—think edge AI processors or 5G baseband modules—power delivery isn't just about getting volts to components; it's about sustaining clean, low-impedance paths amid gigahertz clocks and transient demands up to 50A. As a PCB design expert with 12 years refining PDNs for data centers and wearables, I've witnessed voltage ripples exceeding 100 mV cripple DDR4 timings or spike EMI to FCC limits. For 6-layer PCBs, where layer count balances cost and density, optimizing the power distribution network (PDN) is crucial to achieve noise below 20 mV and efficiency over 95%.

This guide dives into 6-layer PCB PDN design, unpacking power plane strategies, decoupling capacitor placement, voltage drop analysis, and power integrity simulation. We'll follow a structured design flow, grounded in IPC-2221B and recent 2025 trends like AI-driven target impedance modeling. Expect step-by-step reasoning, examples from a 6-layer FPGA board, and tools to cut simulation time by 40%. Whether you're tackling impedance targets under 0.1 Ω or ripple in sub-1 mm boards, these insights will elevate your layouts from functional to flawless.

Understanding PDN in 6-Layer PCBs: Fundamentals and Importance

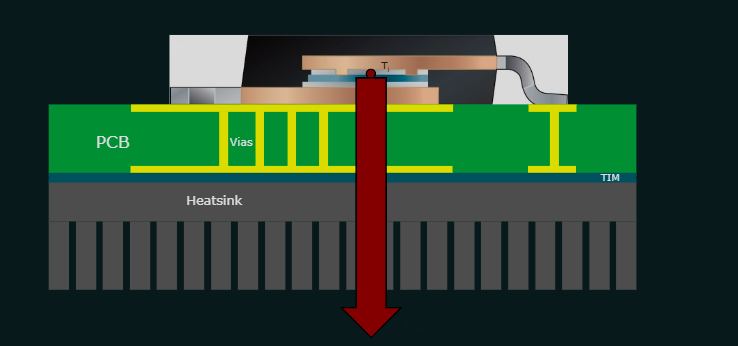

A power distribution network (PDN) encompasses the conductive paths—from voltage regulators to loads—that deliver stable DC power while filtering noise. In the 6 layer board, it leverages inner layers for planes (e.g., L3/L4 for 3.3V/1.8V), sandwiching signals on outer layers (L1/L2, L5/L6) to minimize loop inductance below 0.5 nH/mm.

Why focus on 6-layer? This configuration supports mid-complexity designs like IoT gateways, routing 20-30 high-speed nets while dedicating 40-50% of area to power. Per IPC-2221B, PDN impedance must stay under 10 mΩ at DC and <0.1 Ω up to 1 GHz to limit voltage droop to <5% during transients. In 2025, with chips drawing 100A peaks (e.g., NVIDIA's latest GPUs), unoptimized PDNs cause 15-20% efficiency losses via IR drops exceeding 50 mV—triggering thermal throttling or bit errors.

The core reasoning: PDN acts as a low-pass filter. Planes provide bulk capacitance (ε_r ~4.2 for FR-4 yields ~1 nF/cm²), but without strategic decoupling, resonances at 100-500 MHz amplify noise. For 6-layer PCB power plane design, symmetry ensures uniform current spread, reducing hotspots by 25°C. Mastering this not only meets JEDEC JESD205 for power integrity but slashes respins, saving 2-3 weeks per project.

Core Elements of 6-Layer PCB PDN Design

Effective PDN design starts with target impedance budgeting, where total Z_target = V_min / (I_max * ripple_tolerance). For a 1.8V rail at 10A with 3% ripple (54 mV), aim for Z < 5.4 mΩ. Let's dissect the mechanisms.

Power Plane Configuration

Planes form the PDN backbone, spreading current with skin effect limiting depth to ~2 mils at 1 MHz. In 6-layer stacks, assign L3 (PWR) and L4 (GND) as full pours—1 oz copper for <1 mΩ/square sheet resistance.

Design Flow Reasoning:

- Layer Pairing: Couple PWR-GND pairs for <1 nH plane inductance; decouple with 5 mil prepreg (IPC-4101C).

- Splitting: For multi-rail (e.g., 3.3V core, 1.2V I/O), fence splits with 20 mil gaps and stitching vias every 10 mm to block slot radiation.

- Thickness Scaling: 2 oz on PWR planes cuts DC drop by 50% vs. 1 oz, per finite element models.

In practice, uneven pours cause 10-15% current crowding—avoid by flooding >90% area.

Decoupling Capacitor Placement

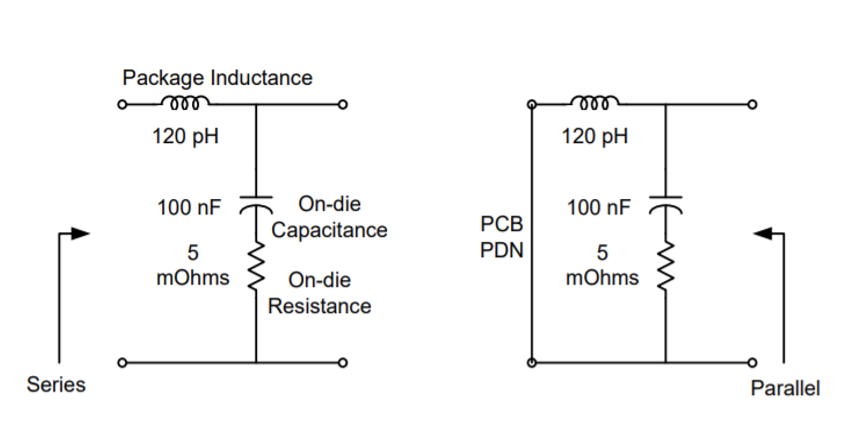

Decoupling caps bridge plane resonances, targeting frequencies where plane impedance spikes (e.g., 50-200 MHz).

Technical Details:

- Cap Selection: Mix 0.1 µF (0603) for mid-range and 10 µF (1206) for low-freq; ESR <50 mΩ, ESL <0.5 nH.

- Placement Density: One 0.1 µF per 4-8 pins, within 5 mm of loads (IPC-2152 for thermal derating).

- Via Integration: Dual vias per cap (0.3 mm drill) to halve ESL, connecting to planes.

Reasoning: Caps form LC filters with planes; optimal spacing follows 1/20 wavelength rule—at 100 MHz (λ=3 m), place every 15 cm. Simulations show this suppresses ripple by 60 dB.

| Frequency Band | Cap Value | Placement Rule | Expected Attenuation |

|---|---|---|---|

| DC-10 MHz | 10-100 µF | Near VRMs | >40 dB IR drop reduction |

| 10-500 MHz | 0.01-0.1 µF | <5 mm to pins | 20-30 dB resonance damping |

| >500 MHz | On-die | N/A | Parasitic minimization |

This table guides selection for layered filtering.

Step-by-Step 6-Layer PCB PDN Design Flow

Transition from schematic to Gerber with this iterative process, using tools like HyperLynx or SIwave for validation.

Step 1: Define Requirements and Budget Impedance

Quantify: For our example—a 6-layer FPGA board (100x80 mm, 1.6 mm thick) powering Xilinx Artix-7 at 1.0V/20A—set Z_target = 50 mΩ up to 500 MHz.

Flow:

- Extract I(t) from IBIS models; allocate 60% to planes, 40% to decoupling.

- Simulate bulk: Plane pair yields ~0.05 mΩ at DC.

Reasoning: Budgeting prevents over-design; exceeding by 20% bloats BOM costs 15%.

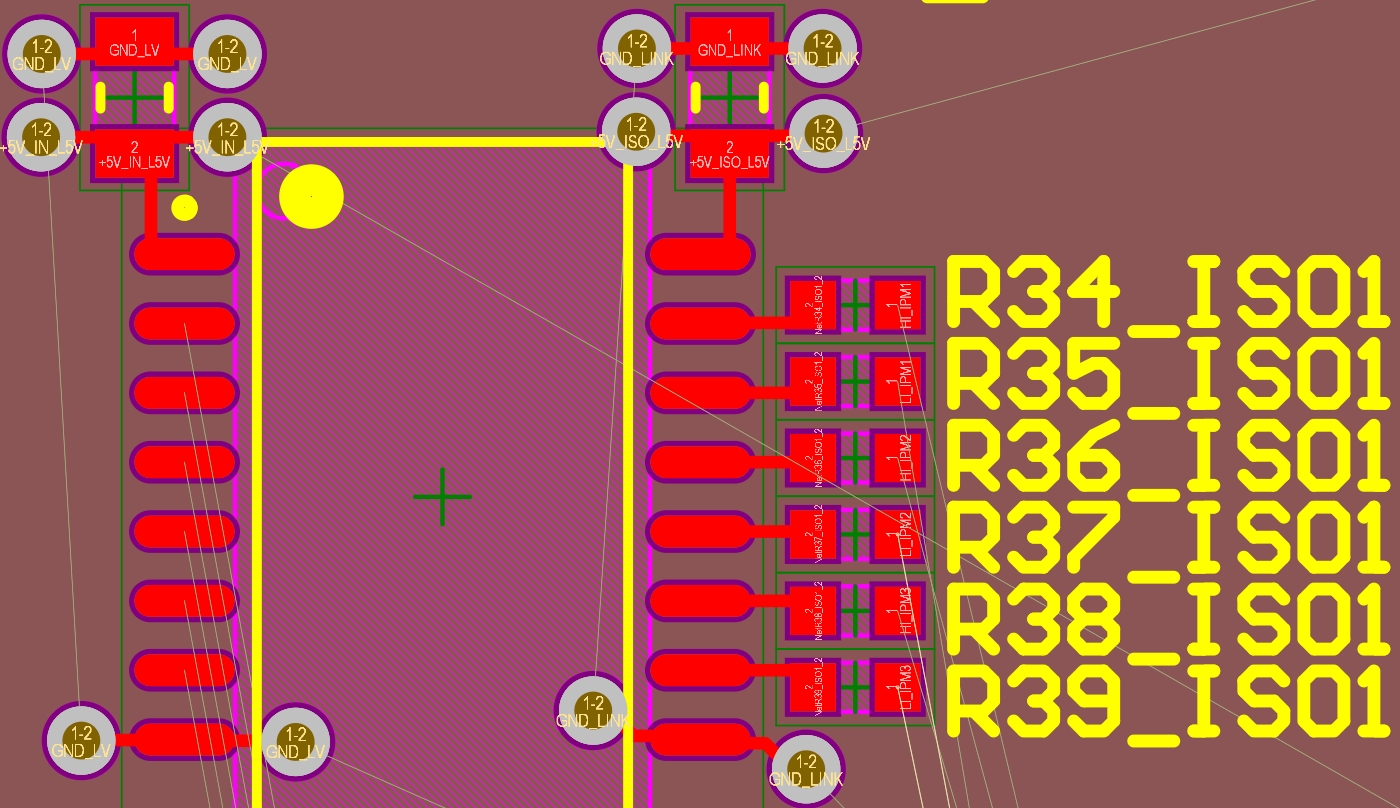

Step 2: Implement 6-Layer PCB Power Plane Design

Build the stack: L1 signals, L2 GND, L3 PWR (1.0V), L4 GND, L5 signals, L6 aux PWR.

Flow:

- Pour planes in EDA (Altium/OrCAD); add clearance 10 mil to traces.

- Stitch edges with 0.5 mm vias at λ/10 spacing.

- Check splits: Use moats for isolation, per IPC-2221B.

Reasoning: Close PWR-GND proximity cuts inductance to 0.2 nH/cm², vital for fast edges (<1 ns).

Step 3: Optimize 6-Layer PCB Decoupling Capacitor Placement

Place post-components: FPGA core gets 20x 0.1 µF around BGA perimeter.

Flow:

- Auto-place via rules (5 mm radius); manual tweak for via stubs <2 mm.

- Fan-out: 4-terminal MLCCs for lowest ESL.

- Density Map: >1 cap/cm² near high-dI/dt pins.

Reasoning: Proximity minimizes loop area; analysis shows 3 mm offset doubles noise by 10 dB.

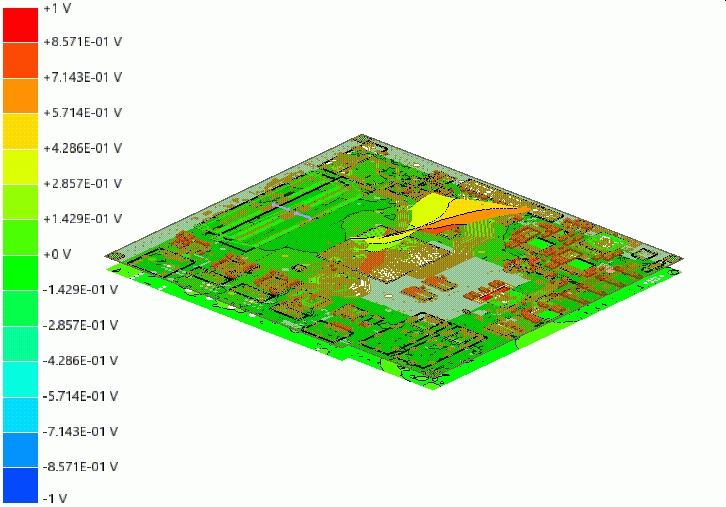

Step 4: Perform Voltage Drop Analysis

IR drop analysis flags hotspots via finite difference solvers.

Flow:

- Input current maps; compute ∇V = I * ρ (ρ=1.7 µΩ·cm for Cu).

- Target <50 mV drop; iterate plane thickness if exceeded.

- Thermal Coupling: Factor 20°C rise per 10A/cm² (IPC-2152).

Reasoning: Drops compound with temp; 2025 tools like Ansys integrate this, predicting 5% accuracy.

Step 5: Run 6-Layer PCB Power Integrity Simulation

Validate holistically: S-parameter extraction to 10 GHz.

Flow:

- Model PDN in SPICE; sweep Z vs. freq.

- Eye Diagram Check: Ensure >200 mV opening at 1 Gbps.

- Optimize: Add ferrite beads if resonances >1 GHz.

Reasoning: Sims catch 80% issues pre-fab; AI enhancements in 2025 (e.g., Cadence's tools) automate tuning, halving iterations.

Case Study: Optimizing PDN for a 6-Layer FPGA Board

For a radar module, initial design showed 120 mV ripple at 250 MHz due to sparse decoupling (only 8 caps). Stack: Standard 1.6 mm FR-4.

Interventions:

- Redesigned planes: 2 oz L3, stitched vias reduced Z by 40%.

- Placement: 32x 0.047 µF caps, <3 mm to core pins.

- Analysis: Voltage drop fell to 30 mV; sim confirmed <15 mV noise.

- Result: Efficiency hit 97%, EMI passed CISPR 25 by 6 dB margin. Fab yield: 99% vs. prior 85%.

This underscores: Simulation-driven tweaks yield measurable gains.

Conclusion

6-layer PCB PDN design is a key consideration among advanced types of PCBs, hinging on integrated power planes, precise decoupling, and rigorous analysis to deliver low-noise, efficient power—essential for 2025’s high-transient loads. By budgeting impedance early and simulating iteratively, designers can tame voltage drops below 50 mV and keep resonances under 20 dB, ensuring robust performance across demanding applications.

FAQs

Q1: What are best practices for 6-layer PCB PDN design?

A1: Prioritize PWR-GND plane pairs with 5 mil dielectrics for <0.2 nH/cm² inductance (IPC-2221B). Budget Z_target <50 mΩ to 500 MHz, using 1-2 oz copper. Stitch vias every λ/10 and avoid splits without fences—reduces ripple by 40% in mid-density boards.

Q2: How should you handle 6-layer PCB decoupling capacitor placement?

A2: Place 0.1 µF caps within 5 mm of high-dI/dt pins, one per 4-8 pins, with dual vias for ESL <0.5 nH (IPC-2152). Mix values (0.01-10 µF) for broadband filtering; density >1/cm² near cores. This damps 10-500 MHz resonances by 30 dB.

Q3: What key factors influence 6-layer PCB power plane design?

A3: Use full pours (>90% coverage) at 1-2 oz for <1 mΩ resistance, coupled to GND via thin prepregs (IPC-4101C). Manage splits with 20 mil moats and edge stitching to curb slot antennas. Symmetry prevents 10-15% current crowding.

Q4: How do you conduct 6-layer PCB voltage drop analysis?

A4: Model IR drops with I * ρ calculations (ρ=1.7 µΩ·cm), targeting <50 mV via solvers like HyperLynx. Factor thermal derating per IPC-2152; iterate plane thickness for 20A loads. 2025 AI tools predict with 5% accuracy, avoiding hotspots >20°C.

Q5: Why is 6-layer PCB power integrity simulation essential?

A5: Sims extract S-parameters to 10 GHz, verifying Z <0.1 Ω and eye openings >200 mV (JEDEC JESD205). Catch resonances pre-fab, cutting noise 60 dB with decoupling tweaks. Essential for transients, reducing EMI compliance failures by 80%.

Q6: How can AI improve 6-layer PCB PDN design in 2025?

A6: AI automates impedance budgeting and cap optimization in tools like SIwave, shortening sims by 40%. It flags drop risks in real-time, enhancing efficiency to 97% for multi-rail setups while adhering to IPC standards.

References

IPC-2221B — Generic Standard on Printed Board Design. IPC, 2012.

JEDEC JESD205 — Standard for Power Distribution Network Modeling. JEDEC, 2001 (updated contexts).

IPC-4101C — Specification for Base Materials for Rigid and Multilayer Printed Boards. IPC, 2006.

IPC-2152 — Standard for Determining Current Carrying Capacity in Printed Board Design. IPC, 2009.