Introduction

As electronic systems operate at higher frequencies, PCB signal loss impedance becomes a critical factor in ensuring reliable performance. Electrical engineers designing high-speed circuits must prioritize impedance control techniques to minimize signal loss and maintain signal integrity. Without proper control, mismatches lead to reflections, distortion, and reduced data rates in applications like telecommunications and computing. This article explores advanced strategies for low-loss PCB design, focusing on practical methods to optimize transmission lines. By understanding these principles, engineers can achieve consistent impedance across the board, reducing high-frequency signal loss effectively.

Understanding Impedance Control in PCBs

Impedance control refers to the process of designing PCB traces to maintain a specific characteristic impedance, typically 50 ohms for single-ended lines or 100 ohms for differential pairs. This characteristic impedance arises from the interaction between inductance and capacitance in the transmission line structure. In PCBs, factors such as trace width, thickness, dielectric height, and material properties dictate the impedance value. Proper control prevents signal reflections at interfaces, which degrade quality and contribute to PCB signal loss impedance issues. For high-speed signals, even small deviations can amplify losses over long traces.

The relevance of impedance control intensifies with rising clock rates in modern electronics. High-frequency signal loss manifests as attenuation and phase shifts, limiting bandwidth and eye diagram opening. Engineers must consider both return loss from mismatches and insertion loss from material dissipation. Standards like IPC-2141A provide guidelines for calculating and verifying controlled impedance in high-speed designs. Implementing these ensures compliance and optimal performance across manufacturing variations.

Key Mechanisms of Signal Loss in High-Frequency PCBs

Signal loss in PCBs primarily stems from conductor losses, dielectric losses, and radiation effects, all exacerbated at high frequencies. Conductor losses dominate due to the skin effect, where current flows near the conductor surface, increasing effective resistance. Surface roughness on copper further elevates this loss by scattering the current path. Dielectric losses occur as the insulating material absorbs energy, quantified by its dissipation factor. Together, these mechanisms cause exponential attenuation with frequency, making minimizing signal loss a priority in low-loss PCB design.

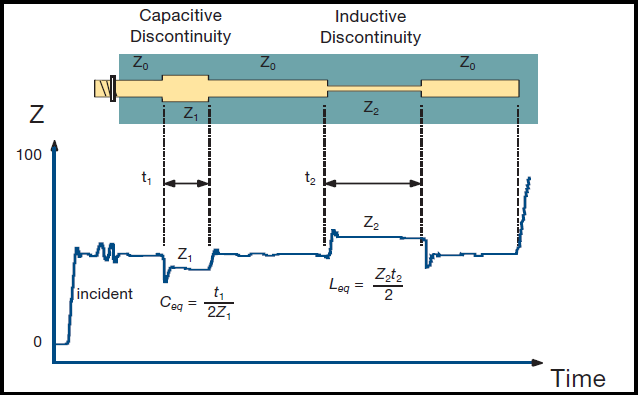

Transmission line theory underpins these losses, modeling traces as distributed RLC networks. Reflections occur when impedance discontinuities disrupt wave propagation, quantified by the reflection coefficient. Radiation losses arise from unbalanced fields or sharp bends, coupling energy away from the signal path. High-frequency signal loss also includes connector and via contributions, which introduce parasitic inductance and capacitance. Understanding these interactions allows engineers to target specific impedance control techniques for mitigation.

Dielectric properties play a pivotal role, with relative permittivity influencing capacitance and thus impedance. Variations in dielectric constant across the board lead to inconsistent Z0, promoting crosstalk and loss. Thermal expansion differences between layers can warp the structure, altering dielectric spacing post-fabrication. Engineers must model these effects during design to predict real-world behavior accurately.

Factors Influencing PCB Impedance

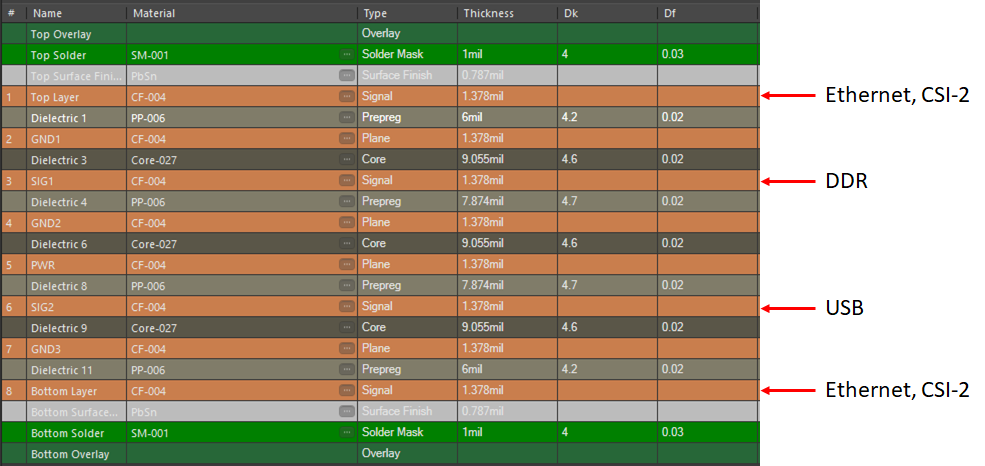

Several geometric and material parameters determine trace impedance in PCB layouts. Trace width directly affects inductance, while height to the reference plane governs capacitance. Copper thickness impacts both, especially in thin high-frequency traces. Dielectric materials with stable permittivity ensure predictable Z0 across temperature and frequency ranges. Symmetric stackups minimize intra-layer variations, supporting uniform impedance control techniques.

Fabrication tolerances introduce variability, such as etching undercuts reducing effective width or plating adding thickness. Reference plane splits or voids create return path discontinuities, spiking impedance. Via stubs act as resonators, reflecting signals at quarter-wave frequencies. Engineers address these through design rules that incorporate statistical margins for manufacturing.

Advanced Techniques for Impedance Control and Loss Minimization

Material selection forms the foundation of low-loss PCB design, favoring dielectrics with low dissipation factor and stable dielectric constant. These materials reduce energy absorption, crucial for high-frequency signal loss reduction. Low-profile copper foils minimize surface roughness, lowering conductor losses via smoother current flow. Combining these yields lower insertion loss over multi-gigabit links.

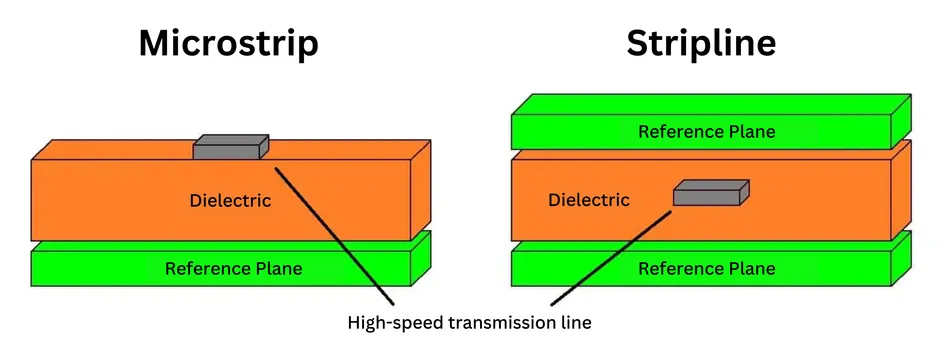

Trace geometry optimization involves precise width and spacing calculations based on stackup specifics. Microstrip lines suit outer layers for easier routing, while striplines offer better shielding in inner layers. Differential pairs require tight length matching to preserve common-mode rejection. Adhering to IPC-2221 design standards ensures traces meet current and thermal requirements alongside impedance targets.

Routing strategies further enhance minimizing signal loss. Length-matched serpentine routes equalize delays in differential signals. Avoiding right-angle bends reduces radiation and stub effects; use 45-degree miters instead. Proximity to reference planes must remain constant, with ground vias stitching planes to contain fields. These impedance control techniques collectively suppress crosstalk and attenuation.

Via design innovations tackle high-frequency bottlenecks. Backdrilling removes stubs, preserving signal fidelity beyond 10 GHz. Blind or buried vias shorten paths, reducing parasitic effects. Controlled depth drilling aligns with layer targets, maintaining stackup integrity. Simulation verifies these before fabrication, correlating with time-domain reflectometry measurements.

Power plane partitioning isolates noisy sections, stabilizing reference potentials. Decoupling capacitors near ICs provide low-impedance return paths. Fill stitching connects plane fragments, minimizing impedance spikes. These practices integrate seamlessly into overall low-loss PCB design workflows.

Troubleshooting Common Impedance Issues

Engineers often encounter impedance drifts from fabrication variances, detectable via TDR scans. Warpage alters dielectric spacing, shifting Z0; controlled lamination per IPC-6012E specifications mitigates this. Moisture absorption swells dielectrics, increasing capacitance; bake-out processes stabilize boards pre-assembly.

Crosstalk troubleshooting involves spacing analysis and guard traces. Simulations reveal coupling levels, guiding layout revisions. Post-fab coupons embedded in panels allow direct impedance verification. Iterative design cycles refine these, ensuring production yields meet specs.

Conclusion

Mastering advanced PCB impedance control techniques is essential for electrical engineers tackling high-speed challenges. By addressing conductor and dielectric losses through material choices, precise geometries, and routing discipline, significant reductions in PCB signal loss impedance occur. Standards like IPC-2141A and IPC-2221 guide these efforts, promoting reliable low-loss PCB design. Implementing simulation, verification, and troubleshooting ensures robust performance. Ultimately, these strategies enable higher data rates and system margins in demanding applications.

FAQs

Q1: What causes PCB signal loss impedance in high-frequency designs?

A1: PCB signal loss impedance arises mainly from mismatches causing reflections, alongside conductor losses from skin effect and dielectric absorption. Surface roughness and via parasitics compound attenuation at gigahertz frequencies. Engineers mitigate this via controlled trace geometries and low-loss materials. Proper stackup symmetry prevents variations, ensuring consistent performance across the board.

Q2: How do impedance control techniques minimize signal loss?

A2: Impedance control techniques minimize signal loss by matching characteristic Z0 to source and load, eliminating reflections and return loss. Low-profile copper and low-Df dielectrics reduce insertion loss components. Symmetric routing and backdrilled vias preserve signal integrity. Verification with TDR confirms tolerances, aligning design with fabrication realities.

Q3: What role does stackup design play in low-loss PCB design?

A3: Stackup design in low-loss PCB design dictates dielectric spacing and plane proximity, directly influencing trace capacitance and inductance. Uniform thicknesses ensure predictable impedance across layers. Reference planes shield signals, curbing radiation losses. Engineers optimize for high-frequency signal loss by balancing symmetry and layer count.

Q4: Why is surface roughness critical for high-frequency signal loss?

A4: Surface roughness increases effective conductor resistance at high frequencies due to current crowding in peaks. Smoother profiles, like reverse-treated foil, lower skin effect losses significantly. This enhances overall minimizing signal loss efforts in impedance-controlled traces. Fabrication processes must prioritize profile control for optimal results.

References

IPC-2141A — Design Guide for High-Speed Controlled Impedance Circuit Boards. IPC

IPC-2221 — Generic Standard on Printed Board Design. IPC

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC, 2015