Introduction

Signal integrity remains a critical concern in modern rigid PCB design, especially as operating frequencies climb into the gigahertz range and data rates exceed several gigabits per second. Engineers face mounting challenges from high-speed signals that demand precise control over transmission paths to prevent degradation. Rigid PCB signal integrity directly impacts system performance, reliability, and compliance with demanding applications in telecommunications, computing, and automotive electronics. This article explores key techniques and best practices for optimizing rigid PCB signal integrity, drawing on established engineering principles. By addressing common pitfalls early in the design phase, teams can achieve robust boards that meet stringent performance criteria. Structured approaches to analysis, simulation, and testing form the foundation for success.

Understanding Signal Integrity in Rigid PCBs

Signal integrity refers to the preservation of electrical signal quality throughout its propagation across a rigid PCB, ensuring that the received waveform closely matches the transmitted one. In rigid PCBs, which consist of solid layers of substrate and copper without flex regions, signals travel through traces, vias, and planes where imperfections can introduce distortions. Core aspects include maintaining characteristic impedance, minimizing losses, and suppressing noise coupling between adjacent lines. Poor rigid PCB signal integrity leads to issues such as bit errors, timing skew, and electromagnetic interference that cascade into system failures. Engineers must prioritize these factors during layout to support high-speed interfaces like PCIe, USB, and DDR memory buses. Adhering to guidelines from IPC-2141 helps establish controlled environments for reliable signal transmission.

Common Signal Integrity Issues in Rigid PCB Design

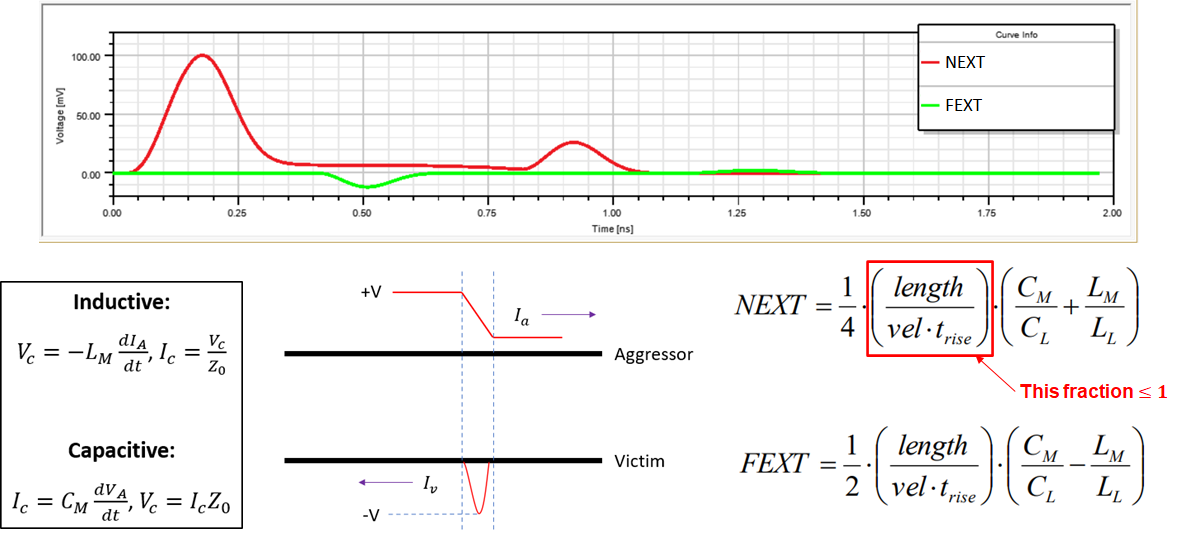

Signal integrity issues in rigid PCB arise primarily from impedance discontinuities, crosstalk, and dielectric losses inherent to multilayer constructions. Reflections occur when signal impedance mismatches at transitions like vias or connectors, causing overshoot, ringing, and reduced eye opening in time-domain signals. Crosstalk manifests as inductive or capacitive coupling between parallel traces, injecting noise that elevates bit error rates in differential pairs. Attenuation from conductor skin effect and dielectric absorption further degrades high-frequency components, limiting effective bandwidth. Ground bounce and power supply noise exacerbate these problems by modulating return paths. Identifying these early through systematic evaluation prevents costly respins.

Vias introduce stub effects in multilayer rigid PCBs, where unused via portions act as resonant stubs reflecting energy back to the source. Improper stackup planning leads to asymmetric fields, skewing differential signaling and common-mode noise. Thermal expansion mismatches between layers can warp traces over time, altering impedances in operational environments. Manufacturing tolerances in trace width and etch depth amplify variations, pushing designs outside acceptable margins. Engineers observe these in prototypes via scope traces revealing closed eyes or jitter exceeding specifications. Proactive mitigation aligns with performance specs in IPC-6012.

Technical Principles of Signal Integrity

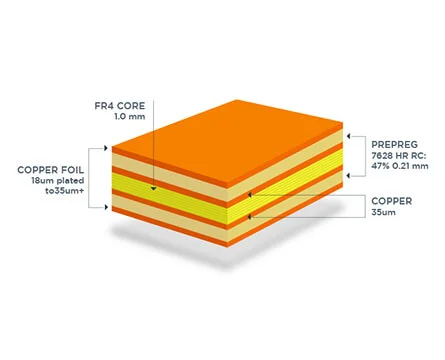

The foundational principle of rigid PCB signal integrity revolves around transmission line theory, where traces behave as distributed inductors and capacitors with defined characteristic impedance Z0. For single-ended lines, Z0 typically targets 50 ohms, while differential pairs aim for 100 ohms differential and 50 ohms common-mode to balance speeds and noise immunity. Dielectric constant Er of the core and prepreg materials dictates capacitance per unit length, influencing propagation delay and loss tangent. Return current flows through adjacent reference planes, forming a transmission line structure essential for low-inductance paths. Engineers calculate Z0 using formulas incorporating trace width W, thickness T, spacing to plane H, and Er. Optimizing these parameters ensures minimal insertion loss and group delay variation.

Loss mechanisms include conductor loss from finite skin depth, dielectric loss from polarization damping, and radiation from unbalanced fields. At frequencies above 1 GHz, skin effect confines current to trace surfaces, increasing effective resistance quadratically with frequency. Low-loss dielectrics with Er around 3.5 to 4.5 and dissipation factor Df below 0.005 minimize absorption. Plane splitting disrupts return paths, forcing signals to detour and pick up inductance, which amplifies ringing. Maintaining continuous ground or power planes beneath high-speed nets preserves integrity. These principles guide stackup decisions for symmetric layering.

Stackup Optimization for Rigid PCB Signal Integrity

Effective stackup design in rigid PCBs allocates layers strategically to isolate high-speed signals from noisy power distribution. Core strategy places signal layers between full ground planes, providing broadside coupled shielding and stable reference for impedance control. Alternating signal-ground-signal configurations reduces intra-pair skew and broadside crosstalk in dense routing. Engineers specify plane clearances around vias to avoid capacitance buildup, typically 10 to 20 times the via diameter. Prepreg thickness uniformity ensures consistent H values across the board. This layered approach supports rigid PCB signal integrity analysis by enabling predictable field distributions.

Thinner dielectrics enable finer impedance tuning but increase capacitive coupling risks between layers. Hybrid stackups blending low-Er materials for signals and higher-Er for power planes balance cost and performance. Thermal management integrates via stitching along plane edges to equalize potentials and dissipate heat. Simulations validate stackup by modeling S-parameters for insertion loss S21 and return loss S11. Field solvers compute coupling coefficients to quantify far-end and near-end crosstalk. Final validation ties back to fabrication capabilities for repeatability.

Routing Techniques and Best Practices

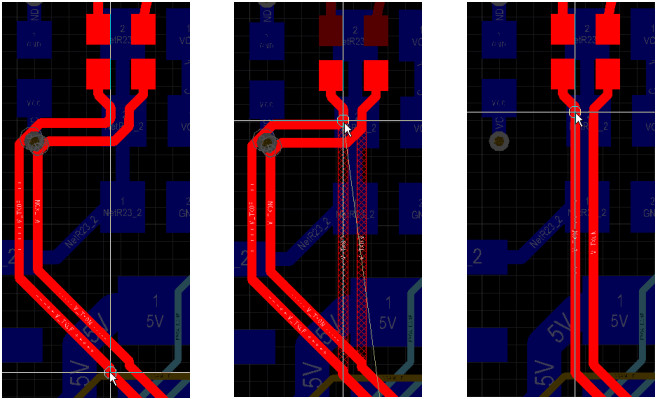

Routing high-speed traces demands length-matched serpentine patterns for parallel buses to equalize propagation delays, preventing setup and hold violations. Differential pairs require constant spacing and symmetric routing to preserve mode conversion immunity. Avoid 90-degree bends; use 45-degree or curved transitions to minimize reflections from corner discontinuities. Length tuning compensates for via delays, targeting sub-picosecond skews in multi-gigabit links. Shield single-ended lines with ground traces or stitches to suppress coupling. These practices form the backbone of rigid PCB signal integrity.

Trace width scaling inversely with frequency maintains Z0 amid skin effect; wider traces at low speeds narrow at highs. Buried routing in inner layers reduces radiation and EMI susceptibility. Decoupling capacitors near ICs provide low-impedance paths for switching currents. Plane cutouts demand stitching vias to bridge splits, ensuring return current flows locally. Post-layout reviews flag violations like excessive meanders or acute angles. Consistent application yields clean eye diagrams.

Via Design and Optimization

Vias pose the greatest discontinuity risk in rigid PCBs due to parasitic inductance and capacitance from pad transitions. Blind and buried vias eliminate stubs in high-density designs, confining transitions to necessary depths. Backdrilling removes unused stub lengths, reducing resonance peaks observable in frequency sweeps. Via pitch optimization spaces arrays to limit ground bounce in power vias. Controlled drill sizes and plating thickness maintain low resistance. Engineers model via S-parameters to predict TDT responses.

Enabling structures like filled vias enhance thermal conductivity while preserving SI. Aspect ratios below 10:1 ensure plating uniformity per fabrication norms. Array configurations with ground vias surround signal vias, forming coaxial shields. Post-drill cleanup prevents debris-induced shorts. Integration with routing preserves pair integrity across layers.

Rigid PCB Signal Integrity Simulation

Rigid PCB signal integrity simulation employs time-domain and frequency-domain tools to predict waveform behavior before fabrication. Pre-layout models assess stackup and trace parameters for Z0 tolerance, typically aiming for +/-10% variation. Channel simulations incorporate transmitter, receiver, and interconnect models to generate eye diagrams revealing height, width, and jitter margins. IBIS models capture nonlinear driver behavior for accurate reflections. Frequency sweeps quantify IL/RL and crosstalk budgets. Iterative refinement converges on passing metrics.

Hyperlynx or similar solvers compute multi-line effects like even/odd mode velocities in pairs. Statistical analysis via Monte Carlo runs accounts for manufacturing variances in Er and geometry. Power integrity co-simulation reveals simultaneous switching noise impacting signals. Post-route verification flags DRC violations and timing pushes. Simulation accelerates design closure, minimizing prototypes.

Rigid PCB Signal Integrity Analysis and Testing

Rigid PCB signal integrity analysis combines simulation with empirical validation to benchmark prototypes. Time-domain reflectometry TDR maps impedance profiles along traces, pinpointing mismatches at vias or bends. Vector network analyzers VNA measure S-parameters for crosstalk Xtalk and loss characterization. Eye pattern analysis on oscilloscopes quantifies Q-factor and bathtub closure under stress. BERT testers inject PRBS patterns to measure BER floors. These methods confirm simulation fidelity.

Fixture design ensures clean launches for measurements, using coplanar launches or adapters. De-embedding removes test structure parasitics for accurate DUT response. Thermal cycling tests reveal impedance drifts from CTE mismatches. Correlation between sim and test guides model tuning. Comprehensive suites per J-STD standards verify end-to-end integrity.

Flying probe or bed-of-nails setups automate DC continuity alongside SI probes. Protocol compliance analyzers decode link training for real-world validation. Failure modes like intermittent opens trace to plating voids. Data logging supports yield analysis for process tweaks.

Advanced Best Practices and Troubleshooting

Implement reference plane pairing religiously, assigning dedicated planes per signal group to isolate domains. Guard traces with grounded edges mitigate edge-coupled noise in fanouts. Decap optimization spaces values logarithmically from 10nF to 10uF for broadband suppression. Firmware tweaks like equalization compensate residual ISI. Troubleshooting starts with scoping critical nets, isolating noise sources via loop area minimization.

Layer sequencing prioritizes signal integrity over routing density where conflicts arise. Design rule checks enforce min spacing scaled by edge rate. Collaboration with fabricators refines DFM for etch control. Lifecycle testing under vibration simulates field conditions.

Conclusion

Optimizing rigid PCB signal integrity demands a holistic approach integrating stackup, routing, vias, simulation, and testing from concept to production. Addressing signal integrity issues in rigid PCB through principled design yields reliable high-speed performance. Key techniques like impedance control, plane continuity, and discontinuity minimization form enduring best practices. Engineers leveraging rigid PCB signal integrity simulation and analysis tools achieve first-pass success rates. Rigorous testing validates assumptions, ensuring compliance and robustness. Prioritizing these elements elevates designs to meet evolving demands.

FAQs

Q1: What are the most common signal integrity issues in rigid PCB designs?

A1: Signal integrity issues in rigid PCB primarily include impedance discontinuities at vias, crosstalk between adjacent traces, and signal attenuation from dielectric losses. Reflections cause overshoot and jitter, while poor return paths amplify ground bounce. Engineers mitigate these via controlled routing and stackup planning, ensuring eye diagrams meet margins for gigabit speeds. Early simulation identifies risks before layout commitment.

Q2: How does rigid PCB signal integrity simulation improve design outcomes?

A2: Rigid PCB signal integrity simulation predicts reflections, crosstalk, and losses using TDR and eye diagram analysis on virtual channels. It enables stackup iterations for Z0 control and via optimization, reducing prototype spins. Co-simulation with PI uncovers noise interactions. Validated models correlate to test, accelerating high-speed certification.

Q3: What techniques are used in rigid PCB signal integrity analysis?

A3: Rigid PCB signal integrity analysis employs TDR for impedance profiling, VNA for S-parameters, and oscilloscope eye patterns for jitter assessment. Protocol testers measure BER under load. De-embedding corrects fixture effects, revealing true interconnect performance. Thermal tests expose drifts.

Q4: Why is rigid PCB signal integrity testing essential post-fabrication?

A4: Rigid PCB signal integrity testing confirms simulation predictions through empirical waveforms, detecting fab variances like etch tolerances. It quantifies margins for compliance, isolating failures like stub resonances. BERT and scoping under stress ensure field reliability. Data informs process controls.

References

IPC-2141 — Design Guide for High-Speed Controlled Impedance Circuit Boards. IPC, 2009

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC, 2015

IPC-2221B — Generic Standard on Printed Board Design. IPC, 2012