Introduction

High density interconnect (HDI) printed circuit boards represent a critical advancement in modern electronics, enabling compact layouts with superior routing density. Stacked vias, a core feature of HDI technology, allow vertical interconnections across multiple layers without consuming excessive board space. Proper adherence to HDI PCB design rules ensures reliable performance in applications demanding high-speed signals and tight spacing. This article explores stacked via design principles, PCB routing strategies, and best practices for signal integrity and impedance control. Electrical engineers benefit from structured guidelines that balance density with manufacturability and long-term reliability.

What Are HDI Stacked Vias and Why Do They Matter?

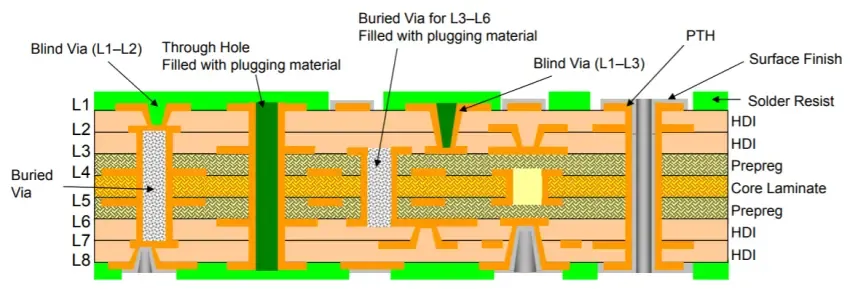

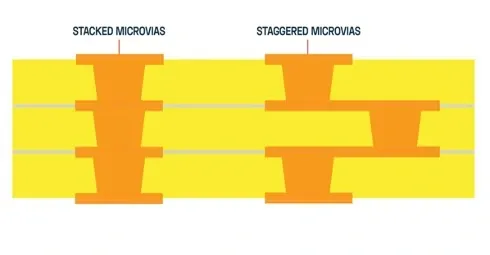

HDI stacked vias consist of microvias aligned directly atop one another, spanning sequential layers in a buildup process. Unlike staggered vias, which offset positions to distribute mechanical stress, stacked configurations maximize vertical density by sharing the same axis. These structures form through laser drilling, copper plating, filling, and planarization steps repeated for each layer. In PCB layout, stacked vias support fine-pitch components like BGAs by facilitating efficient fanout routing. Their relevance grows in high-performance designs where space constraints demand every millimeter of efficiency.

The importance of stacked via design lies in enabling shorter signal paths, which directly impacts signal integrity in high-frequency circuits. Excessive via inductance or capacitance can degrade performance, leading to reflections and crosstalk. Impedance control becomes challenging in dense HDI environments, yet proper rules mitigate these risks. Manufacturers classify HDI boards by via configurations, with stacked vias common in Type III and higher buildups per IPC-2226A guidelines. Engineers must weigh density gains against potential reliability concerns like via cracking under thermal cycling.

Technical Principles of Stacked Via Structures

Stacked vias rely on precise sequential lamination to build interconnects layer by layer. Each microvia requires electroplating to form a barrel, followed by copper filling to create a solid pillar for the next via. Planarization ensures flat surfaces for subsequent imaging and drilling, preventing alignment errors. Mechanical stress concentrates at via interfaces due to CTE mismatches between copper and dielectrics, potentially initiating cracks over time. Reliability testing evaluates these under accelerated conditions, highlighting the need for controlled aspect ratios and fill quality.

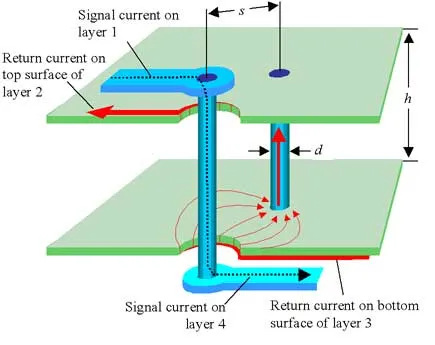

Signal propagation through stacked vias introduces discontinuities that affect impedance profiles. The transition from trace to via barrel alters characteristic impedance, necessitating compensation in PCB routing. For high-speed signals, minimizing stub lengths proves essential, as stubs act as resonant elements. Stacked configurations reduce overall path length compared to through vias, aiding signal integrity. However, poor fill density can trap plating voids, compromising conductivity and thermal dissipation.

In HDI PCB design rules, via pad sizing and annular ring dimensions prevent drill breakout and ensure plating uniformity. IPC-2226A outlines requirements for microvia capture and target pads to accommodate laser tolerances. Dielectric thickness influences capacitance, requiring balanced stackups for controlled impedance. Engineers model these interactions early to predict performance.

Best Practices for HDI Stacked Via Design and PCB Routing

Adopt a conservative stacking approach by limiting consecutive microvias to the minimum necessary, favoring staggered alternatives where routing density permits. This distributes stress and enhances thermal cycling endurance. Always specify copper-filled vias for stacked structures to support planarization and eliminate voids. Plan the stackup during initial layout, allocating buildup layers symmetrically around the core for warpage control. Verify via-to-via spacing exceeds minimum clearances to avoid conductive anodic filamentation (CAF).

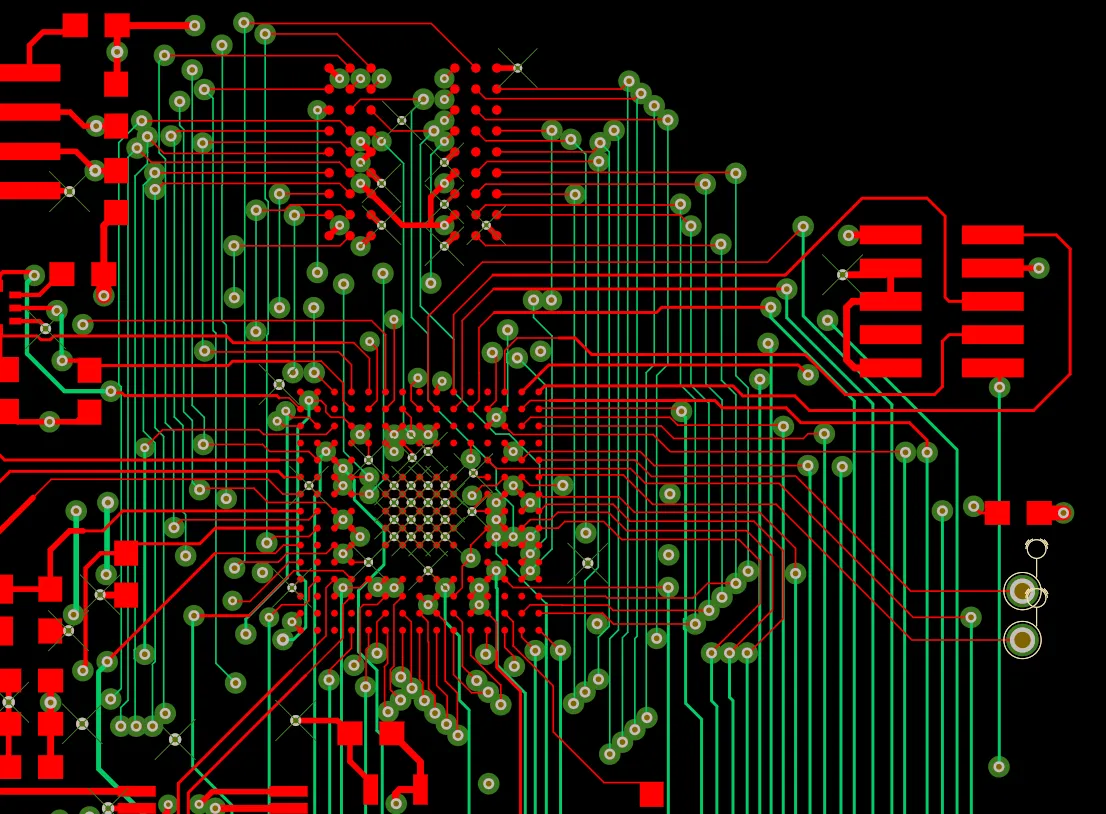

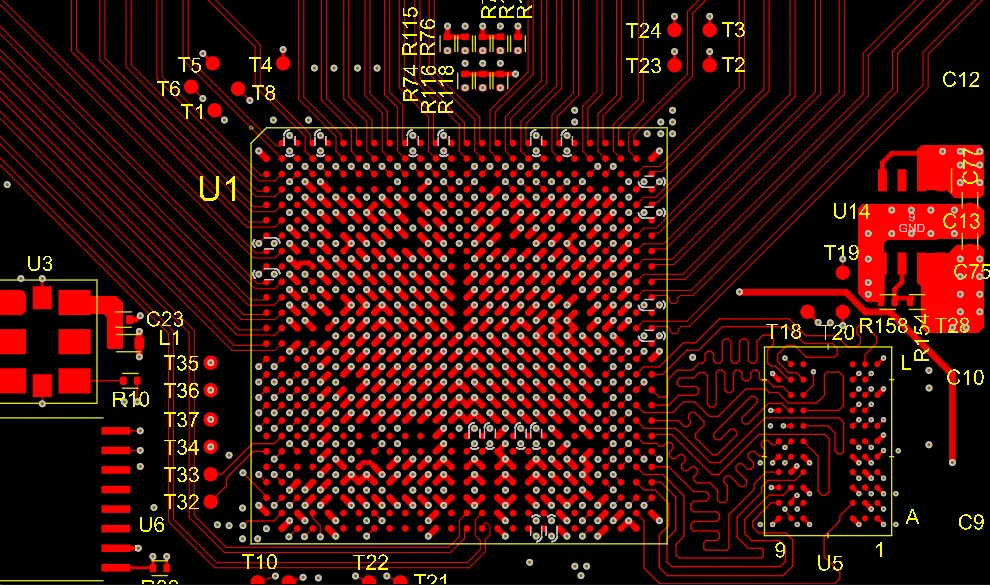

For PCB routing, prioritize escape patterns under high-density components using stacked vias for inner layer transitions. Implement length-matched routing pairs to preserve timing integrity. Maintain consistent trace widths and spacing aligned with target impedance values, typically calculated via field solvers. Transition zones between traces and vias benefit from tapered geometries to smooth impedance profiles. Simulate signal integrity pre-layout to identify hotspots from via farms.

Impedance control demands uniform dielectric heights and material selection with low loss tangents. Reference planes adjacent to signal layers shield against crosstalk, while via anti-pads sized per design rules prevent shorting. In stacked via design, align all vias precisely using fiducials for registration. Post-route verification checks DRC violations and performs electrical rule checks for spacing and annular rings.

Follow IPC-2226A for layer buildup classifications, ensuring compatibility with fabrication capabilities. Document via fill requirements explicitly in fabrication notes. For signal integrity, incorporate backdrilling if through vias interact with stacked sections, though microvias inherently minimize stubs.

Troubleshooting Common Stacked Via Challenges

Misalignment during sequential lamination often stems from drill registration errors, manifesting as open circuits. Cross-section analysis reveals offset barrels; prevention involves tight tolerances on panel tooling. Voids in copper fill arise from inadequate plating current density, detectable via X-ray. Optimize electroplating parameters and use filled vias exclusively for stacks.

Thermal stress induces via barrel cracks, particularly at copper-dielectric interfaces. Staggered vias alleviate this by offsetting loads. Accelerated life testing per industry standards validates designs. Excessive stacking amplifies warpage in thin cores; symmetric buildups counteract this.

Signal reflections from impedance mismatches require S-parameter modeling. Adjust trace-via transitions and verify with time-domain reflectometry.

Conclusion

Mastering HDI stacked via PCB design rules unlocks compact, high-performance layouts essential for modern electronics. Key practices include limited stacking, precise routing, rigorous impedance control, and adherence to standards like IPC-2226A. Balancing density with reliability ensures signal integrity and manufacturability. Electrical engineers achieve optimal results by simulating early, verifying DRCs, and collaborating on stackup planning. Implementing these guidelines minimizes risks and maximizes board efficiency.

FAQs

Q1: What are the primary HDI PCB design rules for stacked via configurations?

A1: HDI PCB design rules emphasize microvia aspect ratios, pad sizing, and fill specifications to ensure plating integrity. Limit consecutive stacks to reduce stress concentration, and maintain clearances for CAF prevention. PCB routing must account for alignment tolerances during sequential buildup. Following IPC-2226A provides structured guidelines for reliable implementations.

Q2: How does stacked via design impact signal integrity in high-speed PCBs?

A2: Stacked via design shortens signal paths, reducing propagation delay and inductance compared to longer through vias. However, transitions introduce discontinuities requiring impedance control through trace geometry and reference planes. Dense via arrays risk crosstalk, mitigated by shielding and spacing rules. Simulations confirm eye diagram quality for optimal performance.

Q3: What are best practices for impedance control in HDI PCB layouts with stacked vias?

A3: Achieve impedance control by selecting low-Dk dielectrics, uniform layer thicknesses, and consistent trace widths in PCB layout. Position ground planes close to signals and size via anti-pads appropriately. Model full stackups including via stubs for accuracy. Verification post-routing ensures tolerance compliance.

Q4: When should engineers choose stacked versus staggered vias in HDI designs?

A4: Opt for stacked vias in ultra-dense areas needing minimal footprint, such as BGA escapes. Choose staggered for better reliability under thermal loads, as offsets distribute stress. Evaluate trade-offs via reliability modeling. Both support high-density interconnects when following design rules.

References

[1] IPC-2226A — Sectional Design Standard for High Density Interconnect (HDI) Printed Boards. IPC, 2017

[2] IPC-2221B — Generic Standard on Printed Board Design. IPC, 2012

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC, 2017