Introduction

In modern PCB manufacturing, high-density interconnects demand precise control over via structures to achieve compact designs without sacrificing reliability. Stacked via aspect ratio emerges as a critical parameter, directly influencing signal integrity, thermal performance, and production yields. Electrical engineers often grapple with optimizing this ratio to enable finer pitch components while adhering to manufacturability constraints. Excessive aspect ratios can lead to plating defects, compromising the barrel integrity essential for current carrying capacity. This guide explores the fundamentals of stacked via aspect ratio, drawing from established PCB design rules and industry practices. By understanding these principles, designers can balance aggressive routing densities with robust fabrication outcomes.

What Is Stacked Via Aspect Ratio and Why It Matters

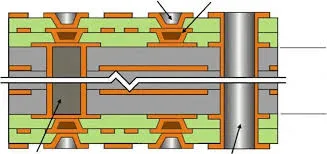

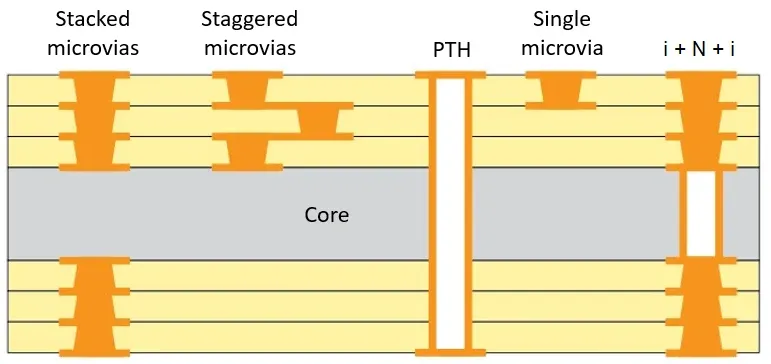

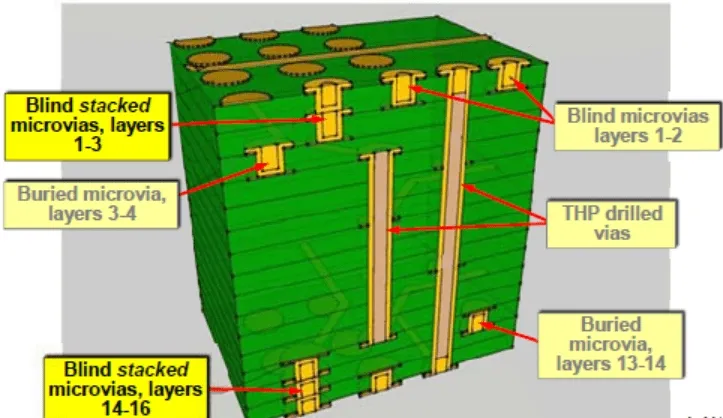

Stacked vias consist of multiple microvias aligned vertically across sequential dielectric layers, forming a continuous interconnect in high-density boards. The aspect ratio for these structures is defined as the ratio of the via's depth, or height, to its drilled diameter, typically expressed as height:diameter. For individual microvias within a stack, industry guidelines cap this at 1:1 maximum, with preferences around 0.75:1 to 0.8:1 for optimal plating uniformity. In stacked configurations, the cumulative height across the stack amplifies challenges, even if each segment meets single-via limits. This metric matters profoundly in PCB manufacturing because it governs copper deposition quality during via plating, affecting void formation and long-term reliability under thermal stress.

High aspect ratios strain electroplating processes, where copper ions struggle to penetrate deep, narrow barrels, resulting in thinner plating at the bottom. Poor plating leads to higher resistance, electromigration risks, and potential failures in high-speed applications. Conversely, conservative ratios enhance manufacturability but may necessitate larger diameters, consuming valuable board real estate in dense layouts. For electrical engineers targeting microvia aspect ratio compliance, adherence to PCB design rules ensures compatibility with standard fabrication flows. Ultimately, mastering stacked via aspect ratio optimizes performance metrics like impedance control while minimizing defects in production.

Technical Principles Behind Stacked Via Aspect Ratio

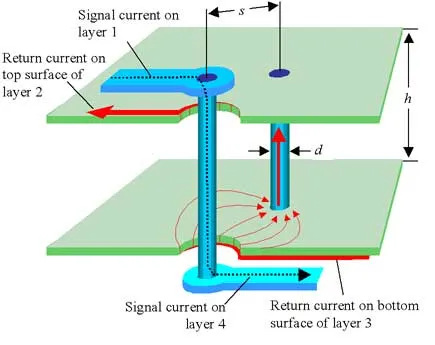

The core challenge in stacked via aspect ratio stems from the physics of electrochemical plating in PCB manufacturing. During via plating, copper is deposited from a solution onto the barrel walls via electrolytic or electroless methods, with plating thickness ideally uniform across the depth. High ratios, exceeding 1:1 for microvias, reduce electrolyte flow and ion diffusion rates, causing tapered deposition where the entrance plates thicker than the base. This phenomenon, known as dog-boning, exacerbates in stacks as each layer's plating interacts with the prior fill. IPC standards for vias, such as those in IPC-6016 for high-density interconnects, emphasize maintaining individual microvia ratios below 1:1 to mitigate these effects.

Thermal expansion mismatches between copper plating and dielectric materials further highlight aspect ratio sensitivity. Under cycling, high-ratio vias experience greater hoop stress on the barrel, promoting cracks or delamination at interfaces. Stacked configurations compound this, as misalignment between vias in adjacent layers creates stress concentrations. Via plating quality directly correlates with aspect ratio, with empirical data showing failure rates doubling beyond 0.8:1 in accelerated life tests. Engineers must consider board thickness, dielectric constants, and layer count when defining stacked via parameters. These principles underscore why microvia aspect ratio serves as a manufacturability gatekeeper in advanced designs.

Fabrication tolerances for drilling also interplay with aspect ratio. Laser-drilled microvias for stacks exhibit entry and exit smear that must be removed via desmear processes, preserving diameter integrity. Mechanical drilling suits larger through-vias but falters in high-density stacks due to aspect ratio limits around 10:1. Sequential lamination builds stacks incrementally, allowing plating per layer, yet cumulative tolerances demand precise alignment. Poor control leads to keyholing, where incomplete bottom plating interrupts conductivity. Thus, stacked via aspect ratio encapsulates a convergence of drilling, plating, and lamination technologies.

PCB Design Rules for Stacked Via Aspect Ratio

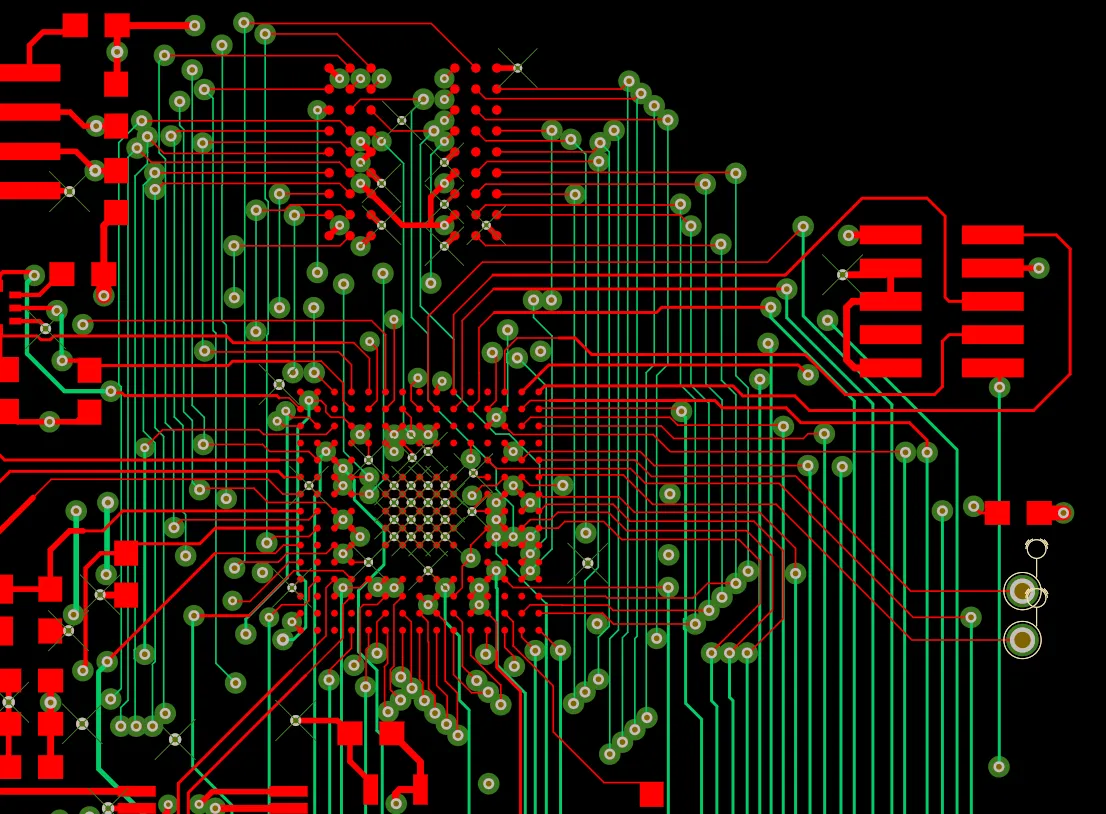

Effective PCB design rules hinge on classifying vias and applying tiered aspect ratio limits. Through-hole vias tolerate up to 10:1 ratios in standard rigid boards, accommodating thicker stacks. Blind and buried vias transition to microvia rules at diameters below 150 microns, enforcing 1:1 maximum per IPC guidelines. For stacked vias, designers specify any-layer or build-up configurations, ensuring each microvia segment adheres to 0.75:1 to 0.8:1 for plating reliability. Pad-to-via clearances, annular ring dimensions, and anti-pad sizes further support these ratios, preventing shorts in dense routing.

Layer pairing strategies influence feasible aspect ratios. Staggered stacks offset vias slightly to distribute stress, allowing marginally higher cumulative heights versus fully aligned stacks. IPC-2226 provides HDI-specific design rules, recommending dielectric thicknesses that yield target ratios post-fabrication tolerances. Engineers simulate plating using software models calibrated to these rules, predicting void risks. Fabricators often impose additional margins, such as 20-30% larger drill diameters to counter plating shrinkage. Integrating these PCB design rules early prevents costly respins.

- Through-Hole: Typical diameter 150-300 μm, max aspect ratio 10:1, used in standard multilayer boards.

- Blind Via: Typical diameter 75-150 μm, max aspect ratio 1:1, connecting core-to-outer layers.

- Microvia (Stacked): Diameter less than 75 μm, target max aspect ratio 0.8:1 per segment for HDI high-density routing.

- Filled Via: Diameter less than 100 μm, max aspect ratio 1:1, commonly used via-in-pad for BGA.

Best Practices for Balancing Performance and Manufacturability

Start with conservative microvia aspect ratios, targeting 0.75:1 across stacks to maximize plating consistency in PCB manufacturing. Select dielectric thicknesses around 75-100 microns for laser vias, pairing with 60-80 micron drills. Employ copper filling for bottom-most vias in stacks to eliminate keyholing propagation. Validate designs against IPC standards for vias, incorporating qualification tests like thermal shock per IPC-6012. Collaborate with fabricators early, sharing stackup details for DFM feedback on achievable ratios.

Optimize via placement to minimize stack depth, using fanout strategies for fine-pitch BGAs. Incorporate filled or plugged vias at stress points to enhance mechanical robustness. Monitor plating thickness targets of 18-25 microns minimum, adjusting current densities in fabrication. For high-reliability apps, limit stacks to two or three microvias, staggering where possible. These practices ensure stacked via aspect ratio supports both electrical performance and yield targets.

Troubleshooting Common Stacked Via Issues

High aspect ratios often manifest as cratering or voids during via plating inspection. Cross-section analysis reveals thin bottom plating; remedy by reducing ratio or enhancing desmear aggressiveness. Misalignment in stacks causes intermittent opens, detectable via flying probe testing. Thermal cycle failures trace to excessive hoop stress, addressed by wider annuli or lower ratios. IPC standards for vias guide acceptance criteria, rejecting barrels with less than 75% continuity. Proactive simulations and pilot builds mitigate these in production.

Conclusion

Stacked via aspect ratio remains pivotal in harmonizing PCB density with fabrication feasibility. By capping microvia ratios at 1:1 and preferring 0.75:1 to 0.8:1, engineers sidestep plating pitfalls while enabling HDI performance. PCB design rules rooted in IPC guidelines provide a reliable framework, from individual segments to full stacks. Practical adherence yields robust boards, minimizing defects and respins. Prioritizing these balances propels designs from prototype to volume manufacturing successfully.

FAQs

Q1: What is the maximum stacked via aspect ratio recommended for PCB manufacturing?

A1: In PCB manufacturing, individual microvias in stacks should not exceed 1:1 aspect ratio, with 0.75:1 to 0.8:1 ideal for via plating reliability. Cumulative stack height depends on layer count, but each segment must comply to avoid voids. Factory processes favor conservative ratios to ensure uniform copper deposition and high yields. Adhering to these limits aligns with standard HDI capabilities.

Q2: How do IPC standards for vias define microvia aspect ratio?

A2: IPC standards for vias classify microvias as blind structures with maximum 1:1 aspect ratio and depth up to 0.25 mm. This ensures manufacturability in stacked configurations. Designers reference these for PCB design rules, prioritizing plating quality. Compliance reduces reliability risks in high-density boards.

Q3: Why is microvia aspect ratio critical in stacked via designs?

A3: Microvia aspect ratio governs electrolyte penetration during via plating, preventing defects like dog-boning in stacked vias. Higher ratios strain deposition, risking thin barrels and thermal failures. Balancing it with PCB design rules optimizes density and performance. Factories enforce limits to maintain process control.

Q4: What PCB design rules improve stacked via manufacturability?

A4: Key PCB design rules include 0.8:1 max per microvia, 20-micron minimum plating, and staggered alignment for stacks. Specify dielectric pairings yielding target ratios post-tolerances. These practices enhance via plating uniformity and reduce stress. Early DFM reviews confirm feasibility.

References

IPC-6012 — Qualification and Performance Specification for Rigid Printed Boards. IPC

IPC-6016 — Qualification and Performance Specification for High Density Interconnect (HDI) Printed Boards. IPC

IPC-2226 — Design Standard for High Density Interconnects. IPC