Introduction

Power is the foundation of any system. A solid power design is a prerequisite for reliable system operation. In many projects the most common topology is an external adapter providing a DC input (5V, 9V, 12V, etc.). On the PCB, DC-DC converters or LDOs are used to generate the rails required by the system. This article summarizes practical details for DC-DC and LDO power circuit design that are easy to overlook. Small improvements in these areas can improve power performance and system stability.

Choosing Between DC-DC and LDO

DC-DC converters and LDOs have clear trade-offs. DC-DC converters offer high efficiency and can supply large currents; efficiencies of around 90% are common, with some devices exceeding 95%. Their disadvantages are more external components, larger PCB area, higher cost, and potential switching noise if filters are not well designed. LDOs are simpler, take less area, and cost less; they provide cleaner linear regulation but their efficiency depends on the input-to-output voltage drop. If the dropout is small or currents are low, an LDO is often a good choice. If the dropout or current is large, a DC-DC converter is usually recommended.

LDO Design Considerations

LDO designs are simple and typically require only a few bypass capacitors. However, several points need attention.

- Thermal dissipation. The LDO dissipates the power from the input-output voltage drop. If the voltage drop and current are large, power dissipation grows and thermal management becomes essential. For example, using 3.3V down to 1.2V at 800mA yields P = (3.3 - 1.2) * 0.8 = 1.68W. Without adequate PCB thermal area, the LDO will run hot. Although many LDOs list maximum junction temperatures around 125°C, sustained high-temperature operation shortens system lifetime and can pose safety risks.

- Dropout voltage. Consider the device's dropout. A common example is the 1117 family with a typical minimum dropout of about 1V. Using 3.3V to get 2.5V with a 1117 is not appropriate; the actual output may be nearer 2.3V and will vary with load current. Newer LDOs have much lower dropout voltages (some around 100mV), which suit many applications.

- Bypass capacitors. Follow the datasheet recommendations for input and output capacitors. Different manufacturers may have different requirements. Some versions of the 1117 recommend an output bypass capacitor of 10μF or larger and may specify capacitor type and ESR range to ensure stable high-frequency response. Check the datasheet carefully for capacitance, type, and ESR guidance.

Trace Inductance and High-Current Routing

DC-DC applications generally involve higher currents and are more sensitive to layout. PCB traces have parasitic inductance that depends on width, thickness, and geometry. A practical reference is: 1 oz copper, 30 mil trace width, 1 inch trace length corresponds to roughly 20 nH of trace inductance. Although that value may seem small, its impact at high di/dt can be substantial.

Use the formula V = L * di/dt, where L is the trace inductance, di is the current change, and dt is the switching transition time. For a 2 A di and a switching transition time of 30 ns,

V = 20 nH * 2 A / 30 ns = 1.33 V

This calculation shows a 1 inch trace can cause a large voltage offset at the switching node, enough to cause power failure. Among the variables, di is set by system demand and dt is largely determined by the power chip. While dt may be adjustable on some devices, slowing transitions increases switching losses. The practical action is to minimize trace length for high-current paths and switch nodes. Low-current control traces such as enable signals are less critical.

Vias and Parasitics

Vias also introduce parasitic inductance. Avoid unnecessary vias on high-current paths, but do not do so at the cost of significantly longer routing. Choose the routing option that produces the smaller overall parasitic impact. A useful rule-of-thumb: a via with a 50 mil board thickness and a 10 mil drill/ID has roughly 1 nH of parasitic inductance. When vias are necessary, paralleling multiple vias is better than a single via, because parallel vias reduce total parasitic inductance.

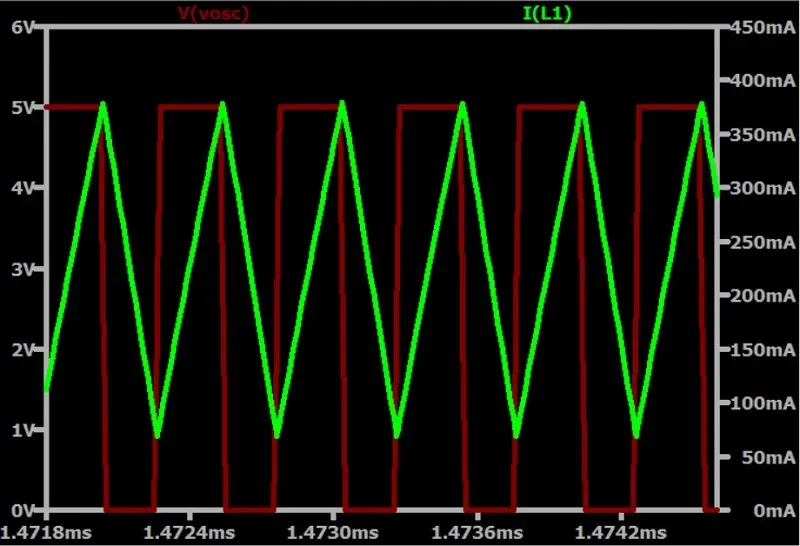

Switching Frequency and Transition Speed

Higher switching frequency reduces the required inductance and inductor size, but higher frequency is not always better. High switching frequency can introduce switching noise; if the system has sensitive circuitry at those frequencies or harmonics, interference can occur. Also, higher switching frequency increases switching losses and reduces efficiency. Distinguish between switching frequency and switching transition speed: switching frequency is like the signal frequency, while transition speed is like the signal rise time. Faster transitions produce steeper edges and richer frequency content, increasing EMI. In practice, switching transition speed often has a larger impact on EMI than the switching frequency itself, so it requires careful attention.

Capacitor Selection

If PCB size and cost are not constrained, using multiple capacitors of different types and values is beneficial. In many consumer designs, cost and space constrain component choices. Use calculation and simulation to determine the required capacitance and number of capacitors. Accurate results require knowledge of the system switching frequency, acceptable voltage ripple, and current transient magnitude. For simple, low-current systems, a pragmatic approach is to place several capacitors of different values (covering multiple decades), which often provides adequate performance without complex calculations.

Inductor Orientation and EMI

Inductor selection is typically guided by the power IC datasheet, which recommends inductance and package choices based on switching frequency. One often-overlooked detail is that inductors can exhibit a preferred winding orientation. The winding has a start and end lead: connecting the start lead to the switch node and the end lead to the output can provide physical shielding of the output from the switch node, reducing EMI. Many inductors mark the start lead with a dot; check and use that marking when possible.

Conclusion

For robust power supply design, consider the points above: choose appropriate topology (DC-DC vs LDO), manage LDO thermal dissipation and dropout, follow datasheet capacitor recommendations, minimize trace length for high-current and switch paths, reduce via parasitics, balance switching frequency with EMI and efficiency, and pay attention to inductor orientation. Optimized component placement and careful routing of high-current and switching traces significantly reduce the risk of power-related failures.