In the early 21st century, the semiconductor industry shifted from analog-driven designs toward digital designs with higher transistor density. As scaling progressed, some predicted analog would be phased out and digital would dominate SoC design.

Why analog remains important for advanced interfaces

Today, with transistor technology scaling below 7 nm, requirements for higher-speed interfaces (for example 112 Gbps and above) have become critical. Implementing such high-speed interfaces purely in the digital domain is very challenging, because supply voltages decrease as power constraints tighten. These factors pose challenges for using pure digital-design circuits in SoCs for functions such as I/O, PLLs, and DLLs.

Emerging applications such as artificial intelligence (AI), high-performance computing (HPC), and high-speed networking add diverse cross-functional features to SoCs. To implement these features, designers leverage RTL logic, standard-cell design, physical design, complex DRC rules, and optimizations in double-patterning flows. However, these optimization techniques face difficulties in I/O design, so the industry requires advanced analog and mixed-signal design techniques.

Balance between analog and digital

Early expectations that signals like sound, light, temperature, position, and heartbeat would be handled purely by analog while other functions would be digital are no longer valid. Specifications now include strict narrowband constraints and operating frequencies have increased by orders of magnitude. As a result, many applications favor analog-top design rather than digital-top design. Advanced interfaces such as HBM, LPDDR, and high-speed D2D SerDes commonly use analog-top approaches. Therefore, trade-offs between analog and digital must be resolved before defining design specifications based on requirements and implementation.

Analog design in sub-7nm processes: key issues and solutions

1. Low supply voltage

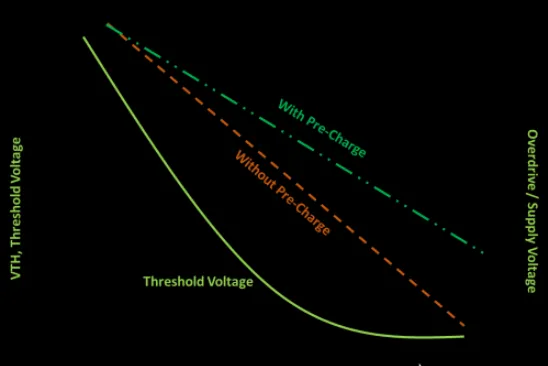

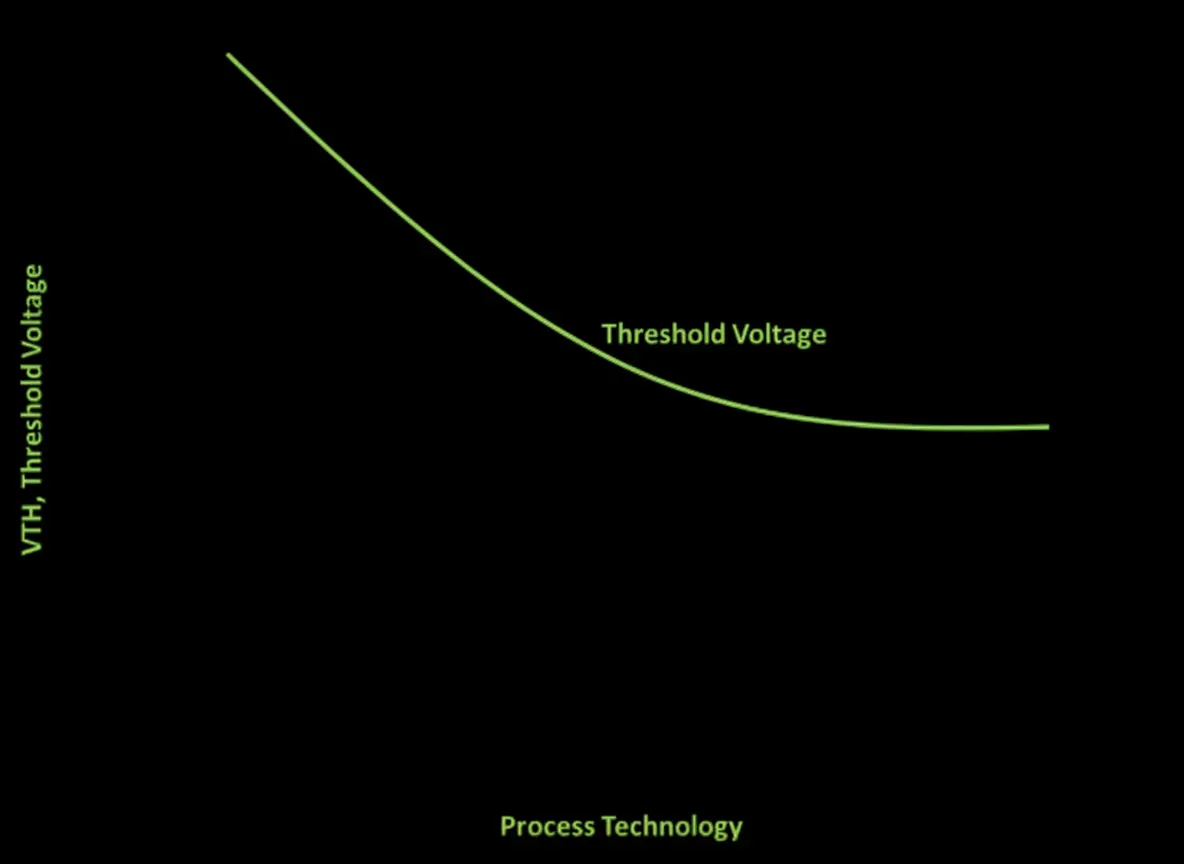

As channel lengths shrink, supply voltages have scaled down from around 3.3 V toward 0.7 V and are expected to fall further. This reduces available overdrive for transistors, both digital and analog. In analog design, this issue can be mitigated by implementing precharged nodes that define initial conditions, enabling circuits to operate at low overdrive.

2. Varying transconductance

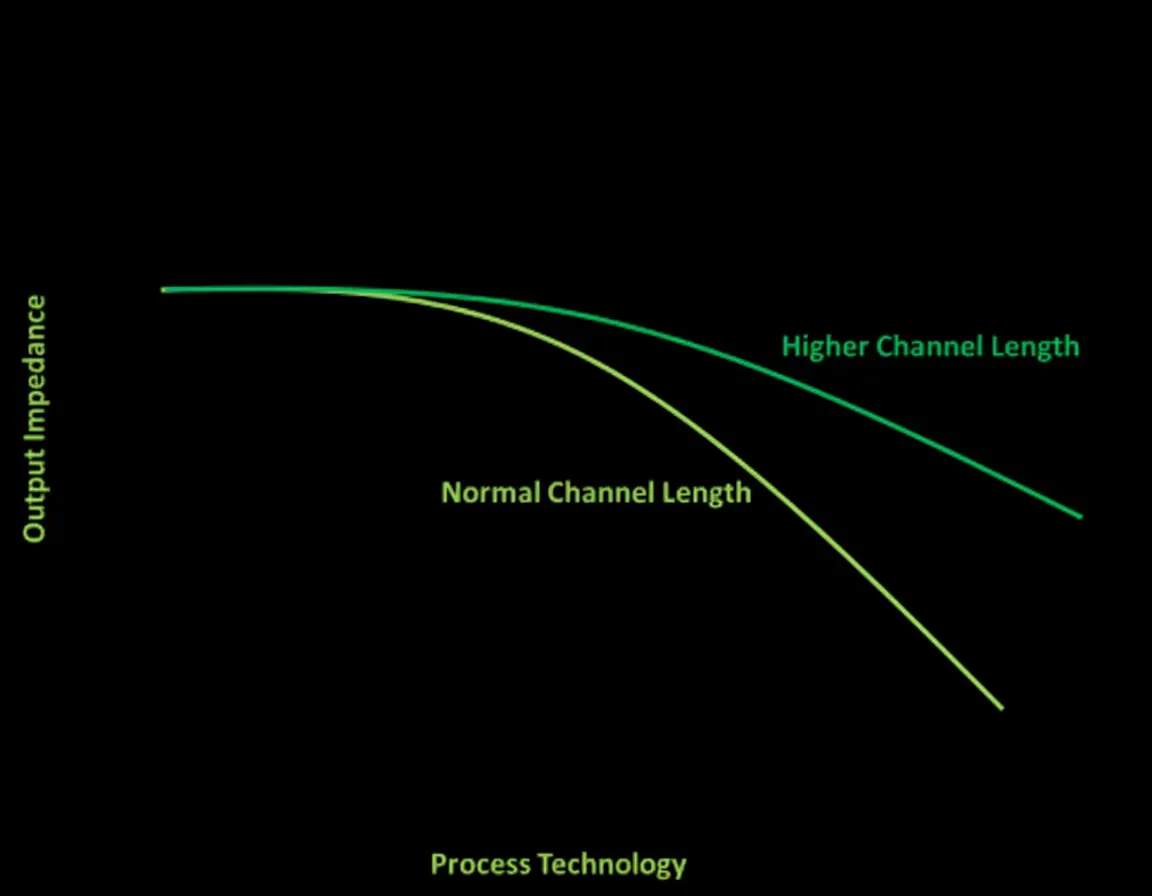

Transconductance is not constant across the voltage range; with shorter channel lengths, biasing becomes critical. Analog designs address this by using longer channel lengths and significant VDS biasing (for example, around 3x overdrive). This approach is not feasible in automated digital flows that default to minimum channel lengths.

3. High threshold voltage

Compared with older nodes, threshold voltage (Vth) is now closer to roughly 50% of supply voltage (versus about 20% in older nodes). The increase of Vth relative to supply is challenging because little headroom remains for circuits that must operate at high speed. Analog designs mitigate high Vth effects using proper pull-up and pull-down transistor structures.

Implementation challenges and strategies for sub-7nm designs

Digital implementation challenges

- Digital implementation relies heavily on scripts and automation. Script improvements are infrequent and the same scripts are used for extended periods. The script owners' institutional knowledge is critical to the automation flow.

- Achieving very small skew remains difficult; a 50 ps skew is an unlikely target yet is a common requirement for high-speed SoC designs at 4 Gbps and above.

- EM/IR issues in digital designs are influenced by script quality. Improving IR drop and EM problems requires both domain expertise and automation expertise.

- Application of APR tools is increasingly important to achieve optimized layouts, routing, and power-grid structures.

Advanced analog implementation strategies

- Precharge techniques that allow advanced on-chip architectures to use defined initial conditions for higher performance.

- Custom layouts for parasitic matching to meet physical-design and timing closure goals for skew/jitter.

- Accurate simulators and system-level signal-integrity/power-integrity (SI/PI) sign-off for complete 2.5D SiP.

- Precise correlation between implementation and sign-off to accelerate design convergence.

- Accurate prediction of path delay, crosstalk, and interconnect delay.

Analog and mixed-signal design challenges

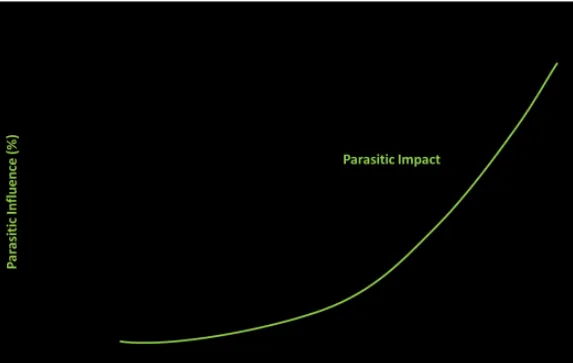

Sub-7nm transistors increase functional density but complicate analog-circuit design. These small transistors cannot tolerate large voltages and practical supply levels are on the order of around 1 V or less. Analog circuits that historically operated at ±5 V have scaled to nominal levels such as 3.3 V, 1.8 V, 1.2 V, and 0.75 V; future projections include 0.5 V or even 0.2 V. Lower supply voltages not only reduce digital power consumption but also increase analog sensitivity to noise and interference, degrading signal quality. In addition, smaller transistors increase mismatch, leading to random offset errors, increased flicker noise (1/f), and reduced gain.

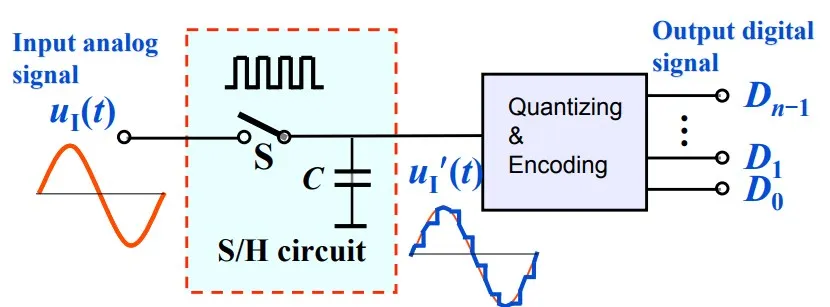

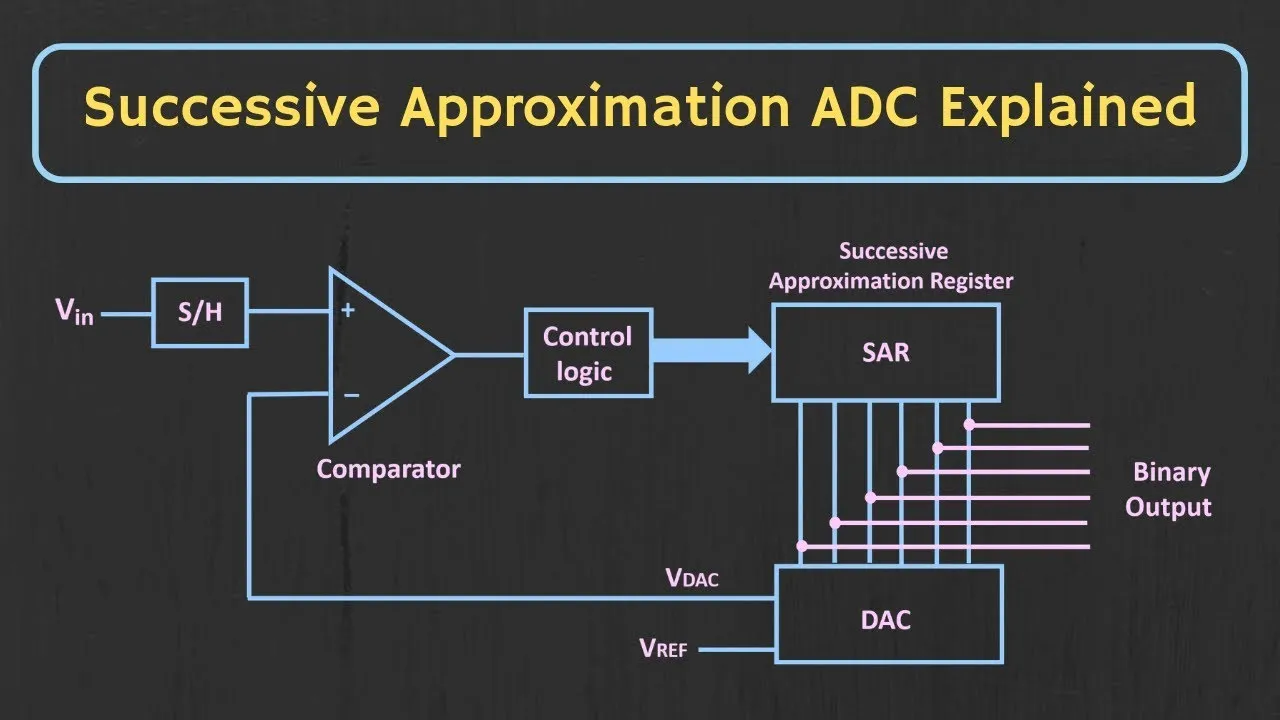

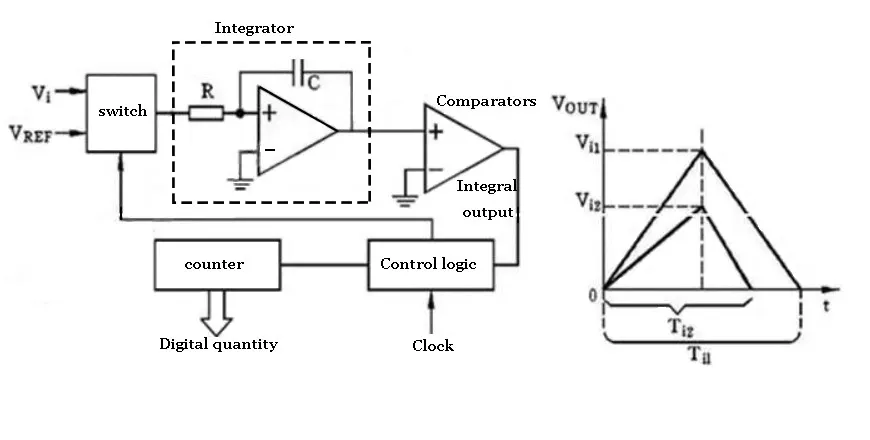

Digital and analog signal exchange is necessary

As wires per millimeter increase in ASICs, many traditional architectures and design techniques become inadequate, requiring new design approaches. Examples include custom layout and precharged node strategies to achieve higher speeds and to avoid crosstalk.

Advanced scaling also opens new possibilities for analog design. In nanoscale processes transistors switch very quickly but cannot handle large voltages. This enables designers to represent analog information using alternative domains at the transistor level, for example using delay instead of traditional voltage or current. Such approaches create new circuit design opportunities.

Furthermore, in advanced technologies switching occurs faster even when processing analog information. Many analog functions can be implemented using traditional digital building blocks such as switches or ring oscillators.

Resurgence of industrial analog techniques

The analog-electronics domain is receiving renewed attention. The broader digital transformation has increased the need for analog solutions. Mobile devices integrate numerous analog interfaces and sensors, and the number of these elements grows with each new generation of products. Internet of Things (IoT) applications require large numbers of sensors, both analog and digital, for data acquisition and processing under strict power and cost constraints. Analog designers who address these complex constraints have substantial opportunities to influence the industry through ongoing developments.