Background

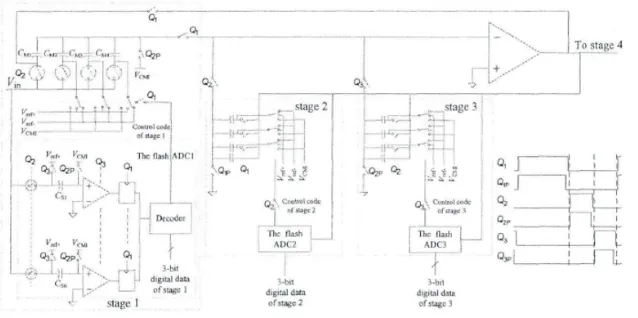

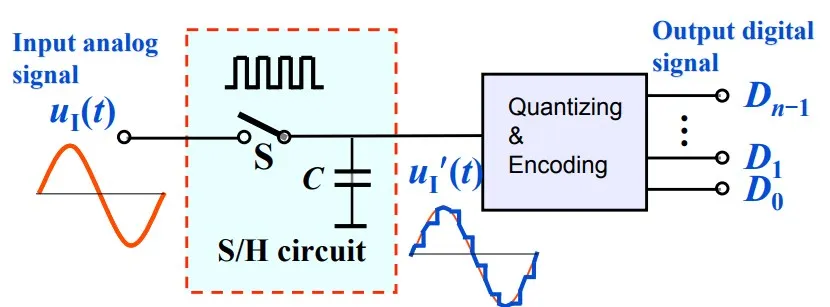

Pipelined ADCs typically use a sample-and-hold amplifier (SHA) at each stage to sample the residue from the previous stage. However, in op-amp-sharing architectures the SHA can account for 20%–30% of total power due to heavy load and bandwidth requirements [1]. Because the SHA is located at the front of each stage, its nonlinearity and noise are amplified by subsequent pipeline stages, degrading overall ADC linearity and dynamic range. For this reason, modern pipelined ADC architectures often adopt SHA-less designs. This approach was proposed in [2], and one such circuit architecture is shown below [3].

SHA-less Architecture and Operation

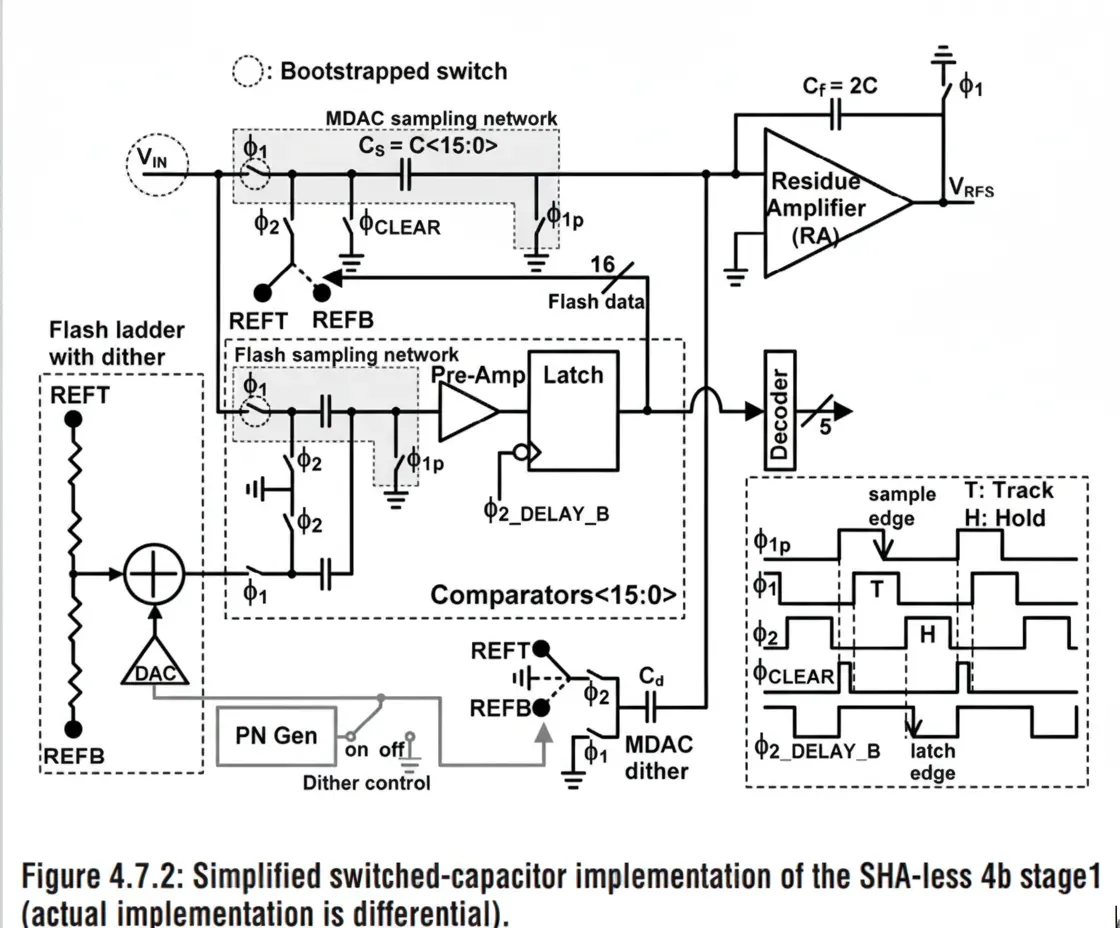

The architecture removes the SHA to reduce power. The top path is an MDAC implemented with a switched-capacitor op amp, and the bottom path is the sub-ADC. The comparator is a discrete-time switched-capacitor comparator. The timing diagram in the figure shows the basic operation.

During φ1 high, the MDAC and comparator sample the input. φ1p is also high to keep the input node at the common-mode level. φ1p is released first to remove charge-injection effects from the switch channel (this effect is explained in Razavi's book); note that the inverting input node is left floating. After that, φ2 closes the switches and the comparator begins operating. The preamplifier develops a differential voltage that is sent to the latch. φ2_DELAY_B is the reset clock. After φ2 goes high, adequate delay is allowed for the preamplifier; then φ2_DELAY_B goes low, and the latch enters the latching phase. The latch uses fast positive feedback to amplify and latch the differential input, and the encoded result is output to the MDAC control switches.

Limitations and Mitigations

This structure still has some drawbacks. First, the signal input paths for the MDAC and the sub-ADC may be mismatched, i.e., the RC time constants of the switches can differ. At high input frequencies this can cause substantial sampling differences (aperture error) [2]. This issue can be mitigated by using the same topology at the MDAC and comparator sampling nodes and by designing the sampling switch W/L ratios to match RC time constants.

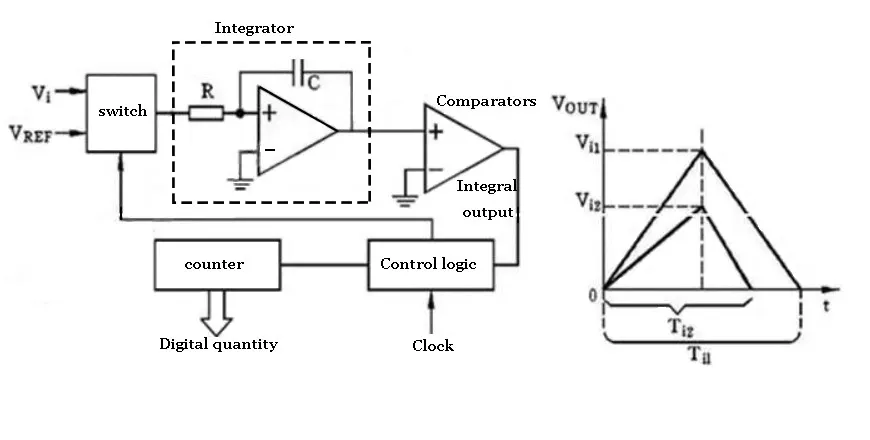

Second, the speed is limited. As seen from the timing analysis, there is an additional comparison time between the sampling phase and the amplification phase. Only after the comparator output is established will the MDAC switches move to the correct reference voltages to complete the conversion. One solution is to split the sampling phase into two segments and perform the comparison during the second segment. A structure and timing diagram that split the sampling phase are shown below [4].