Background

Recently I watched a webinar on balancing MOSFET differential-pair analog layout parasitic effects. The topic was of interest because, as early as 1982, I wrote my first IC layout automation tool at Intel. That tool automatically created about 15% of the layout for the 82786 GPU chip. In 1986 I joined Silicon Compilers. Historically, automation for digital layout modules led the way because analog IC layouts have many more constraints and have been more difficult to automate.

Differential Pair Design Requirements

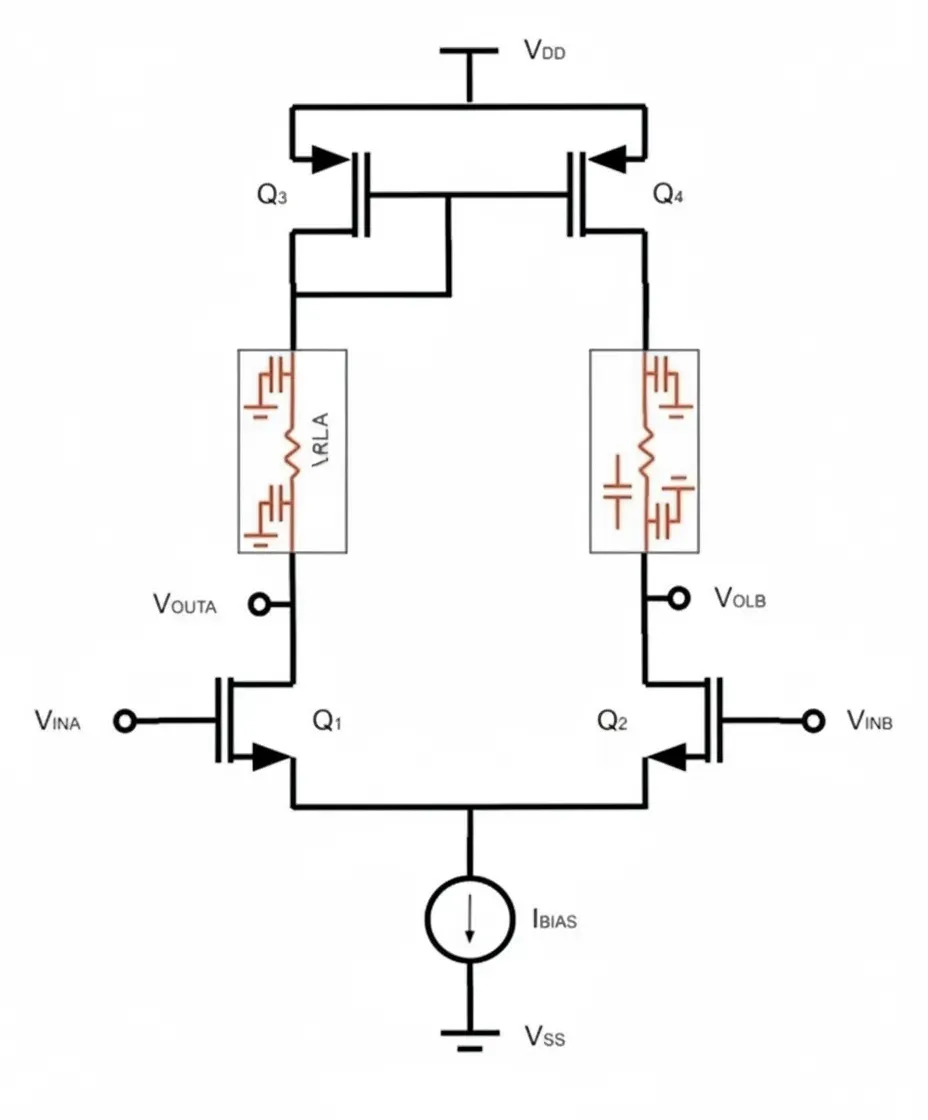

For a matched differential pair amplifier, there are many specific requirements to ensure robust performance, for example:

- Matching transistor W and L values in the amplifier

- Balanced interconnect parasitics

- Use of common-centroid layouts to reduce layout-related effects

- Current mirror layouts with minimal parasitic RC

Analog IC Layout Automation

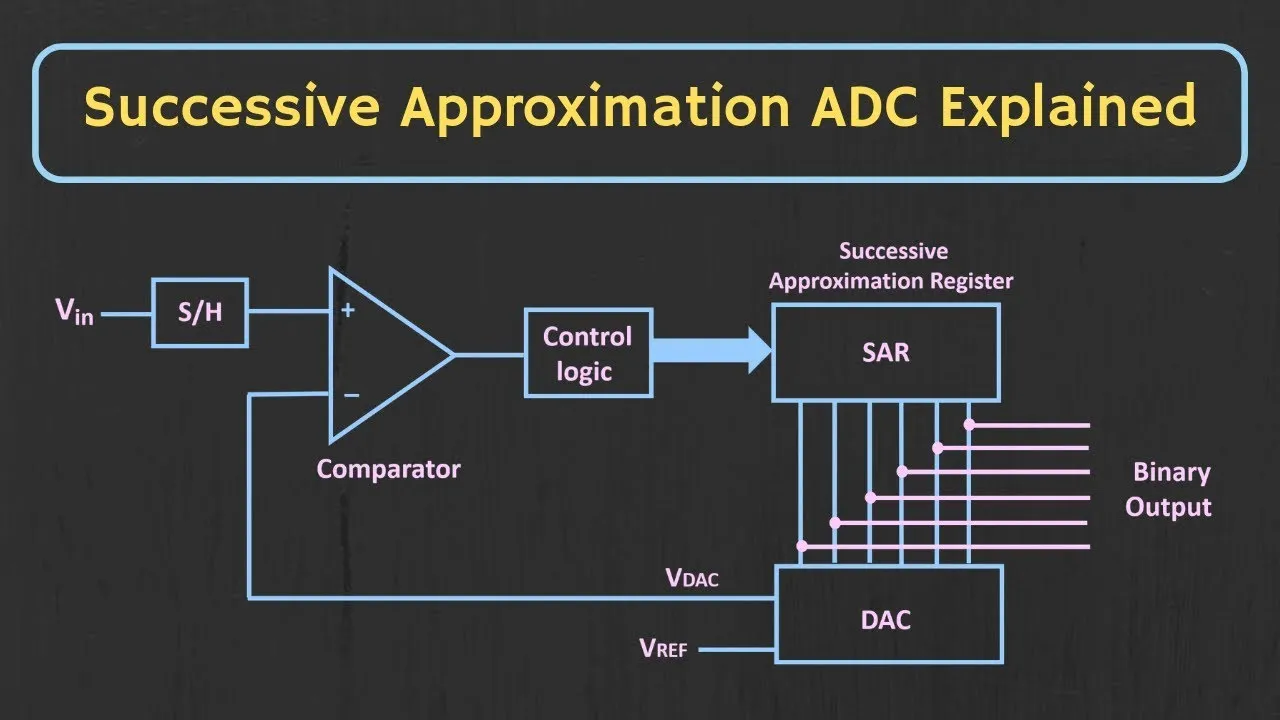

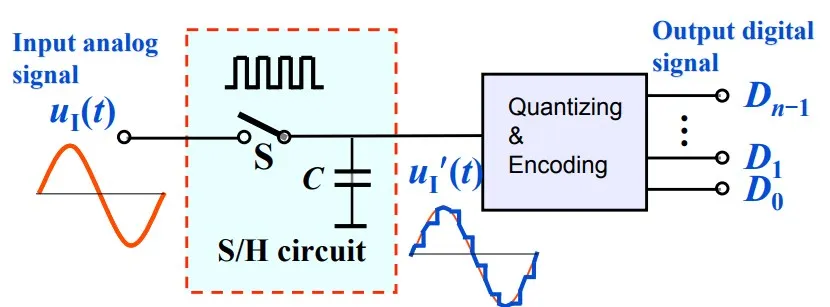

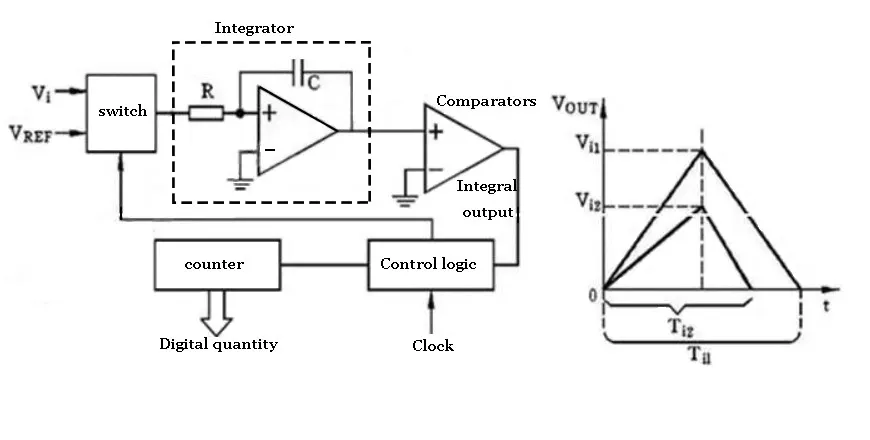

Paul demonstrated how the Animate Preview plugin works within the Cadence Virtuoso environment. The tool automatically recognizes schematic structures such as current mirrors and differential pairs, then constrains placement in the layout similarly to how an experienced IC layout designer would. Multiple layout options that are DRC-clean after construction can be generated quickly, allowing rapid comparison of alternatives.

The schematic identifies transistor matching for W and L values.

Demo Details

The first automatically generated layout opens the "Animate Preview" dialog, which shows panels for hierarchy, schematic, layout, results, and constraints. The Layout panel displays nine generated layout topologies. The Results panel lists analyses for each layout, such as aspect ratio, width, height, and area. Each constraint generated from the schematic is listed in the Constraints panel.

Animate recognizes the differential pair in the schematic. By zooming into the schematic you can inspect layout options for the transistors, including the number of rows used. Clicking any element in the schematic cross-probes and highlights the corresponding device in the layout window.

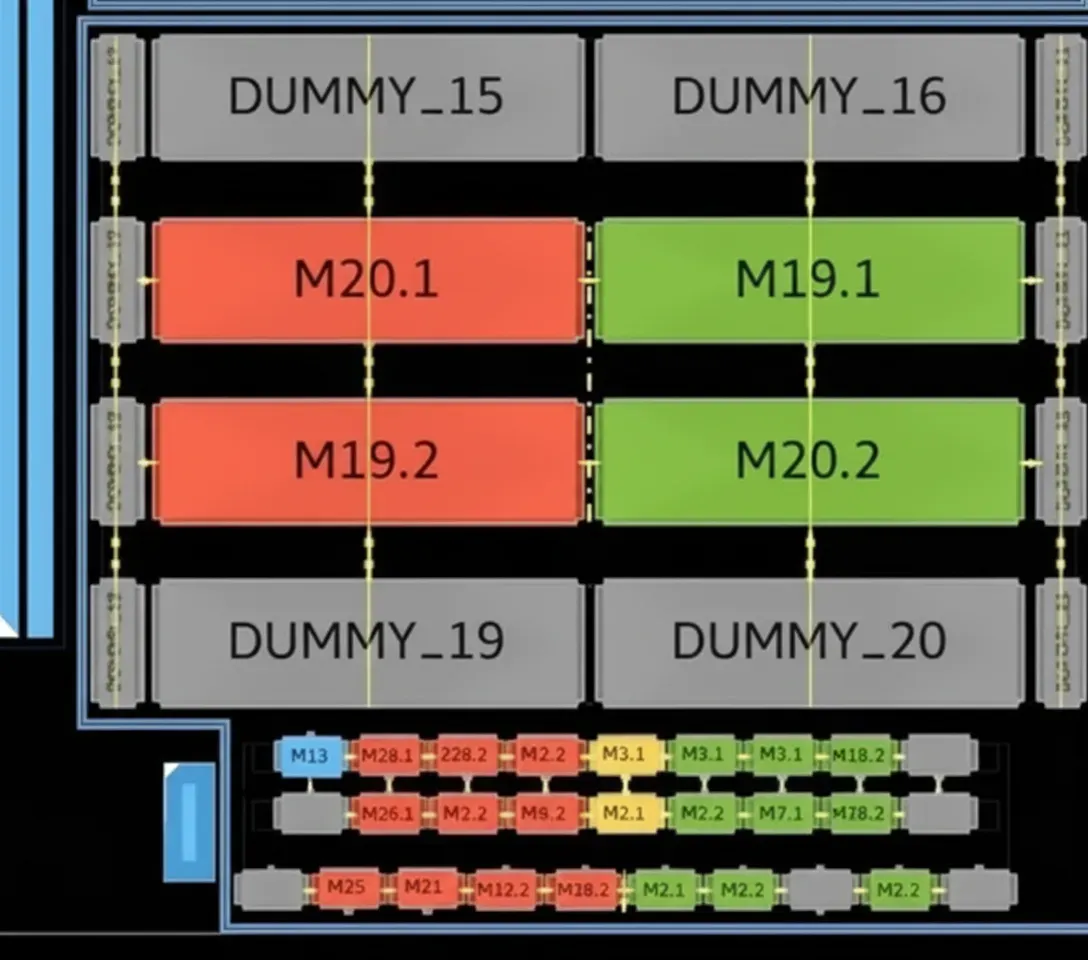

The transistors M19 and M20 define the differential pair. The layout shows these devices placed in regular rows and columns using a common-centroid arrangement, which helps minimize process variation and enforces matched spacing both vertically and horizontally. The polygon head orientation is defined consistently as part of the matching strategy.

To further optimize the layout for vertical matching, virtual rows were added above and below devices M19 and M20 using a menu option.

The tool also allows viewing detailed metal routing by isolating polygon, metal1, metal2, metal3, metal4, and metal5 layers so you can confirm that interconnects in the differential pair are identical and balanced. The routing of source and drain nodes can be visually compared to ensure balance.

The demo also showed a common-centroid layout for four current-mirror devices: M8, M10, M11, and M12. Depending on the design, routing between the current mirror and the differential pair is minimized and symmetric. Inspecting the interconnect between the current mirror and the differential pair confirmed that the metal layers were symmetric and matched.

The differential pair outputs connect to two additional devices whose placement and routing are also balanced. Constraint options were changed from basic analog to mirrored basic analog to control symmetric layout of the left (red) and right (green) devices. A butterfly layout choice is available in the interface.

Summary

Traditionally, analog integrated circuit design followed a flow where circuit designers drew schematics, annotated them with notes for layout engineers, and then handed them off. The layout engineer implemented placement and routing based on those notes, then returned layouts to the circuit designer for checks on symmetry and matching. This iterative loop continued until matching constraints were satisfied.

Automation tools demonstrated in the webinar enable circuit designers to generate balanced and symmetric layouts in minutes rather than days by applying automated schematic-driven placement and constraint enforcement within the layout environment.