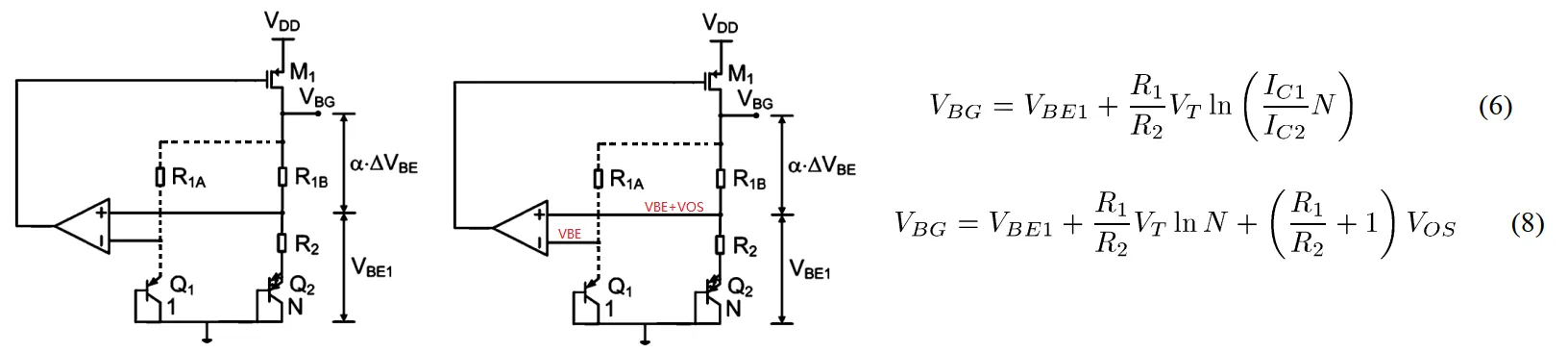

Effect of op-amp VOS on bandgap output

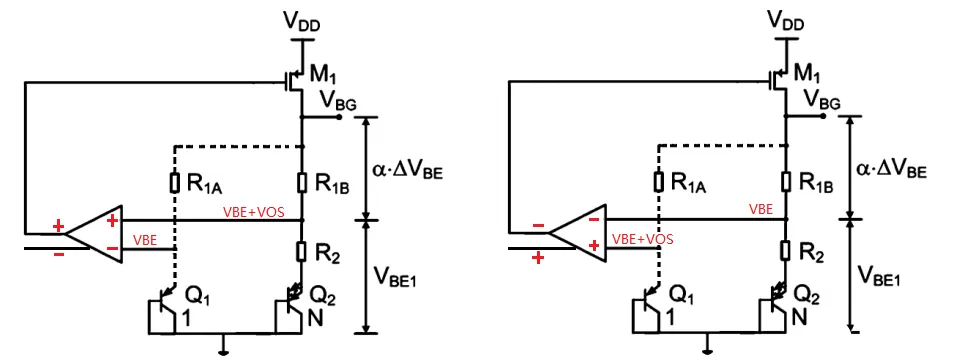

The influence of the op amp input offset voltage VOS on the bandgap output VBG is shown below.

The VBG voltage expression on the left is given by equation (6).

Considering the op amp has a total input offset voltage VOS, the loop gain with the op amp in the circuit is

G_loop = (R1 + R2 + 1/gmQ2) / (R2 + 1/gmQ2) ≈ (R1 + R2) / R2

(1/gmQ2 is small relative to R1 and R2). Assuming the op amp open-loop gain is sufficiently large so that the inputs are effectively clamped to VBEQ1, the negative input is VBE and the positive input is VBE + VOS. The input differential is therefore VOS, which is reflected at the output as VBG + VOS * G_loop, leading to equation (8). Clearly, VOS is amplified by the loop and adds to VBG, affecting the reference voltage. Therefore, the op amp offset VOS must be suppressed.

Derivation update for equation (8)

Updated 2023/08/04: The original VBG expression is

VBG0 = VBE2 + (R1 + R2) * (VBE1 - VBE2) / R2.

After introducing +VOS, the top of R2 becomes VBE1 + VOS, so

VBG = VBE2 + (R1 + R2) * (VBE1 + VOS - VBE2) / R2 = VBG0 + (R1 + R2) / R2 * VOS.

If the derivation uses VBE1 as the variable: after adding +VOS, the top of R2 is VBE1 + VOS, then

VBG = VBE1 + VOS + R1 * (VBE1 + VOS - VBE2) / R2 = VBE1 + R1/R2 * (VBE1 - VBE2) + (1 + R1/R2) * VOS = VBG0 + (R1 + R2) / R2 * VOS.

Offset cancellation with a chopper

The main contribution to the op amp offset comes from mismatch in the input pair (other contributions exist and will be analyzed later).

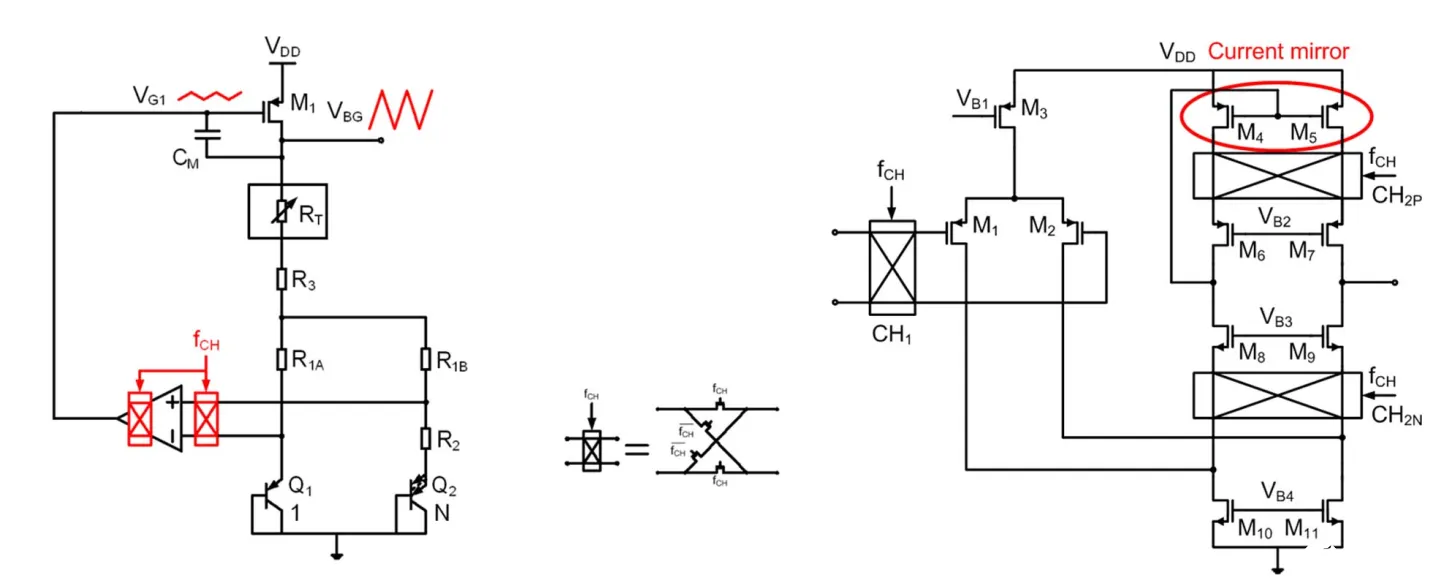

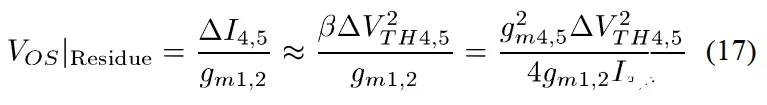

The chopper technique periodically swaps the op amp inputs. To keep the feedback polarity unchanged, the outputs are swapped correspondingly, as shown below.

During the first half of the chopper period, the op amp adds +VOS to VBG; during the second half it adds -VOS. Over one full chopper period, the ±VOS contributions cancel, eliminating the offset effect on VBG.

Inputs and outputs must be switched simultaneously to preserve the op amp feedback polarity within the loop.

Chopper analysis for a folded-cascode op amp

Consider the folded-cascode op amp with chopper switches:

Using a chopper clock, the op amp output is periodically inverted. Note CH1 and CH2N are complementary clocks. The resulting configuration is shown below.

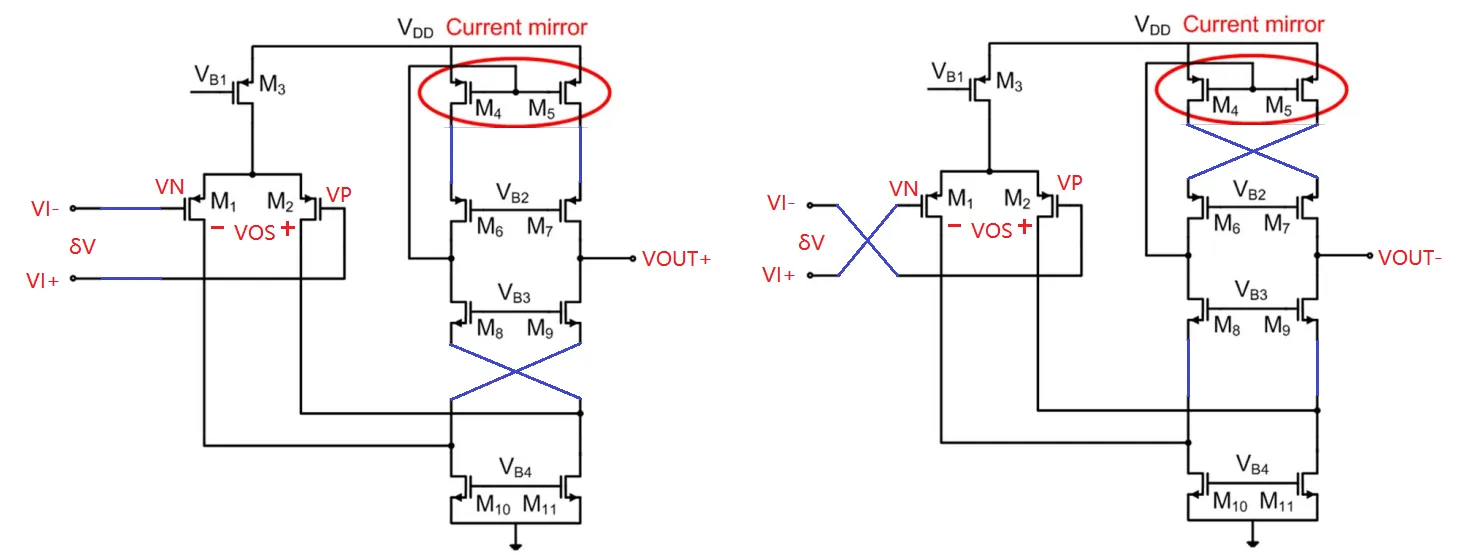

Assume mismatch in M1/M2 appears as VP - VN = +VOS, and the op amp open-loop gain is A.

Left case: VI+ connected to VP, VI- to VN, and VI+ - VI- = δV → VOUT+ = A * (δV + VOS).

Right case: VI+ connected to VN, VI- to VP, and VI+ - VI- = δV → VOUT- = A * (δV - VOS).

The average over the two halves is (VOUT+ + VOUT-) / 2 = A * δV, so the input offset VOS is canceled over a full period.

Similarly, mismatch between M10 and M11 can be canceled by this mechanism; derivation omitted here.

Mismatch among M6/M7/M8/M9 has less impact compared with the input pair M1/M2 and the tail current devices M10/M11, and therefore is not considered further; good layout matching is sufficient.

Residual mismatch between M4 and M5

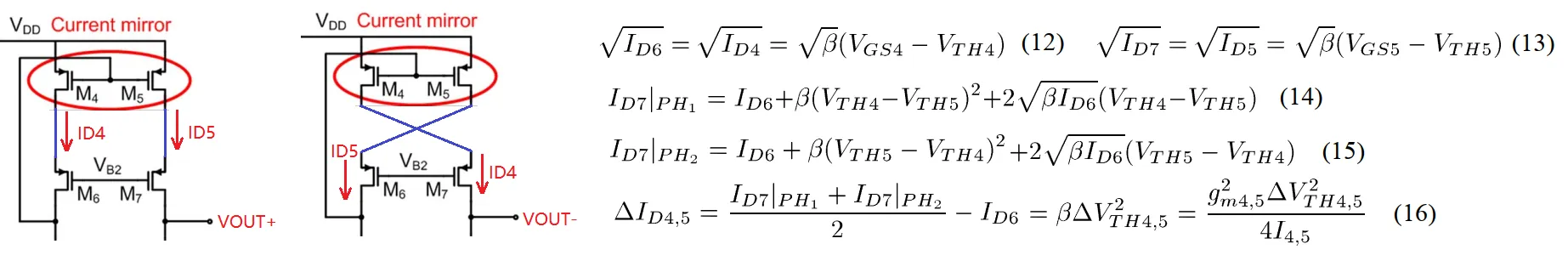

Mismatch between M4 and M5 cannot be completely eliminated.

In the first half period: ID7 = ID5, ID6 = ID4, yielding equation (14). In the second half period: ID7 = ID4, ID6 = ID5, yielding equation (15).

Equations (14) and (15) both use ID6 as the reference variable, eliminating VGS as a variable. If M4/M5 differ in VTH, then VGS values in the two halves will differ and make the derivation more complex. In an initial derivation, assuming the two VGS values are equal led to cancellation and suggested M4/M5 mismatch could be removed.

Combining equations (14) and (15) to eliminate ID6 gives the change in branch currents between the two halves. The first-order term in (VTH4 - VTH5) is canceled by the chopper; the remaining uncompensated term is a second-order term proportional to β * (VTH4 - VTH5)^2.

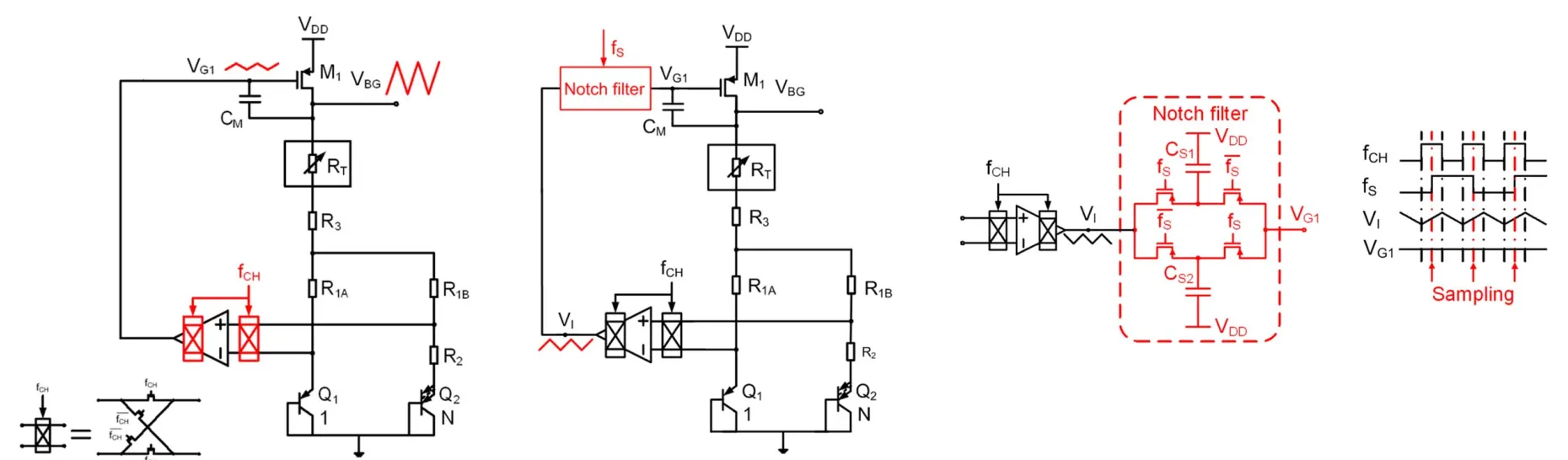

This current change, when referred back to the input pair, requires an input correction of the magnitude shown below.

Assuming a VTH difference between M4 and M5 of 3 mV, the equivalent input offset contributed is on the order of microvolts. Careful layout matching between M4 and M5 effectively reduces this value.

Post-chopper filtering

Chopping introduces switching ripple at the op amp output. This ripple is removed using a notch filter.

A simple switched-capacitor (SC) notch filter uses a T-shaped arrangement of capacitors and switches. When fs is high, CS1 samples VI and CS2 holds VG1; when fs is low, CS2 samples V1 and CS1 holds VG1.

The switch-and-capacitor network forms an RC low-pass filter that removes high-frequency noise on V1. To ensure accurate sampling, the fs clock must be phase-shifted by 1/4 period relative to the op amp chopper clock.

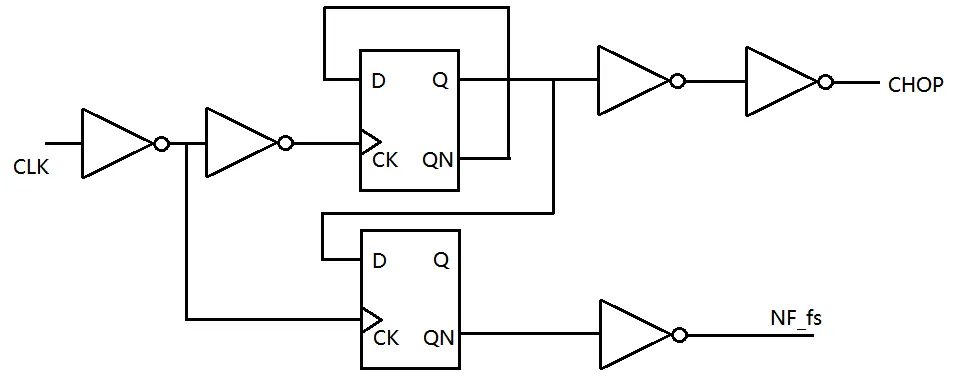

Clock implementation

A practical clock generation circuit is shown below.

The input CLK is divided by two using D-type flip-flops to produce the CHOP clock. By inverting CLK and sampling the CHOP clock, the notch filter clock fs is generated with a 1/4-period phase shift relative to the CHOP clock.