Overview

Modern communication systems and test equipment often need to convert analog signals to digital as quickly as possible so that signal processing can be performed in the digital domain. Designing a transformer-coupled front end for an analog-to-digital converter (ADC) can be challenging, especially in mid-to-high intermediate frequency (IF) systems. This article summarizes five design steps to guide ADC front-end development: 1) understand system and design requirements; 2) determine the ADC input impedance; 3) determine the ADC baseline performance; 4) select the transformer and passive components to match the load; 5) benchmark the design. This approach is straightforward and helps achieve the desired performance for many applications.

These steps may sound simple, but they are important. Knowing the requirements for a specific application reduces iteration, enables appropriate component selection from the start, and accelerates achievement of target performance. List the design requirements and set performance metric bounds so you can quickly choose an appropriate ADC and transformer.

Step 1: Define system and design requirements

For example, assume an application requires a sampling rate of 61.44 Msps to capture a 20 MHz bandwidth input centered at 110 MHz (100-120 MHz). An SNR above 72 dB implies a 14-bit ADC is needed to meet SNR targets. Power per channel should be below 500 mW. Analog Devices (ADI) AD9246, a 14-bit, 80 Msps ADC, can meet these system-level requirements; it supports a 1.8-3.3 V supply range and offers wide input bandwidth with low power consumption.

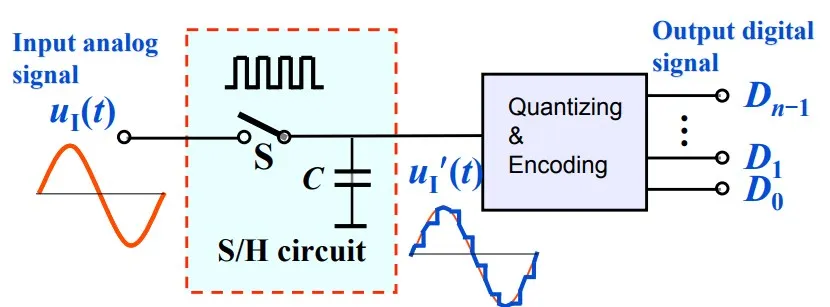

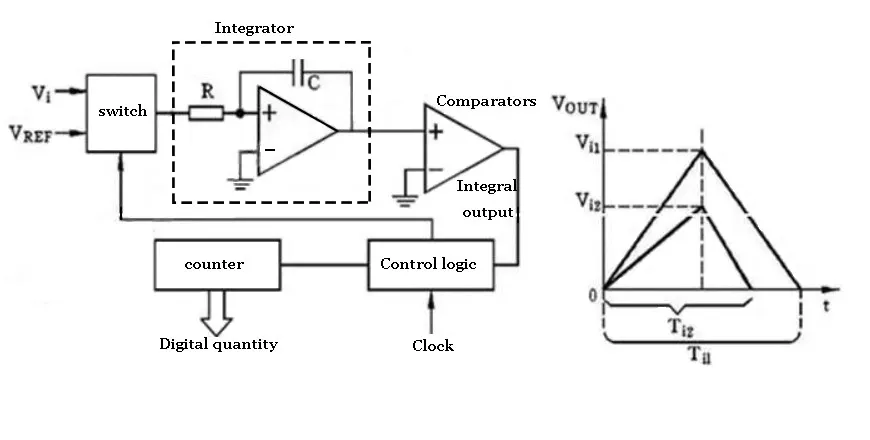

In this example the ADC input is a 110 MHz IF signal with 20 MHz bandwidth and a 61.44 Msps sampling rate. Since the input bandwidth is narrow (one Nyquist bandwidth), resonant matching is used. Resonant matching provides a narrow bandwidth but very good matching within the targeted frequency range. This technique typically requires adding an inductor or a ferrite bead on the analog input to block parasitic capacitance seen at the ADC input. If the IF of interest were at baseband (one Nyquist bandwidth), a simple RC network could form a low-pass anti-aliasing filter.

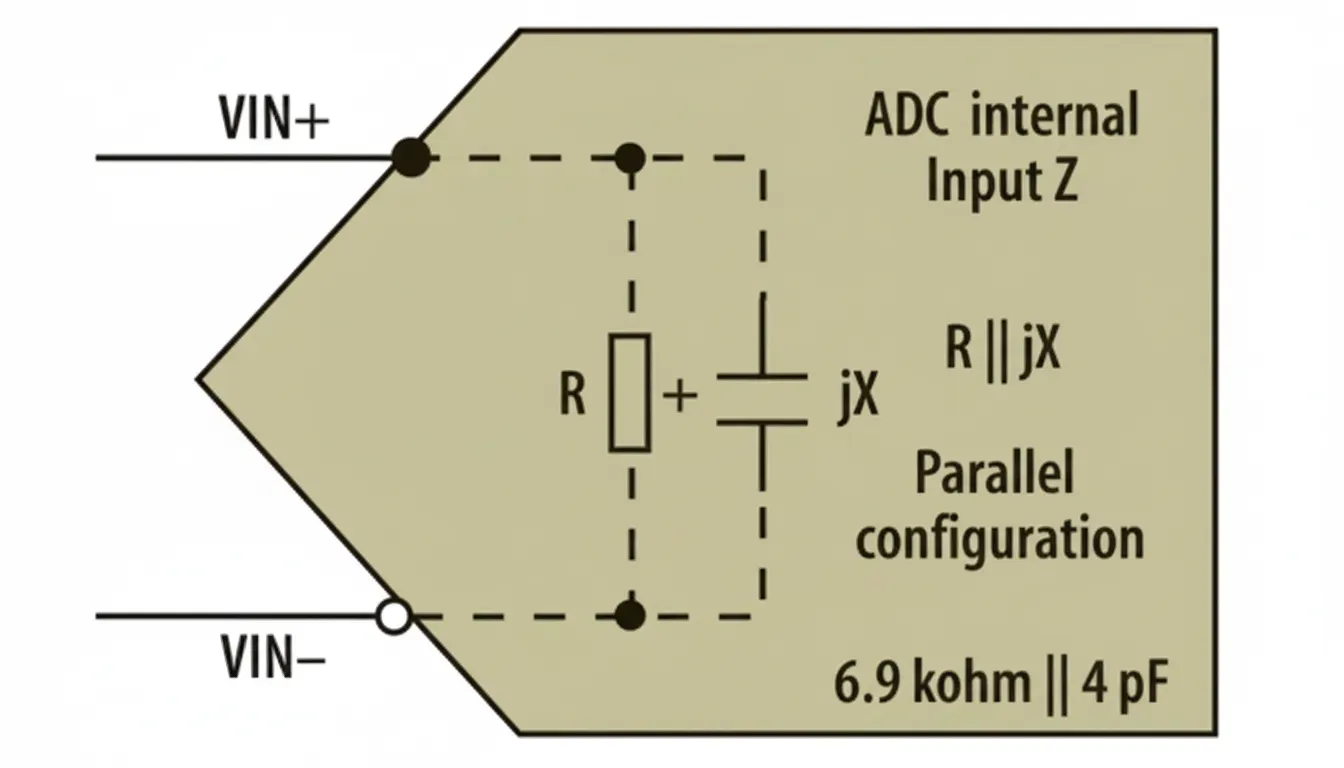

Step 2: Determine the ADC input impedance

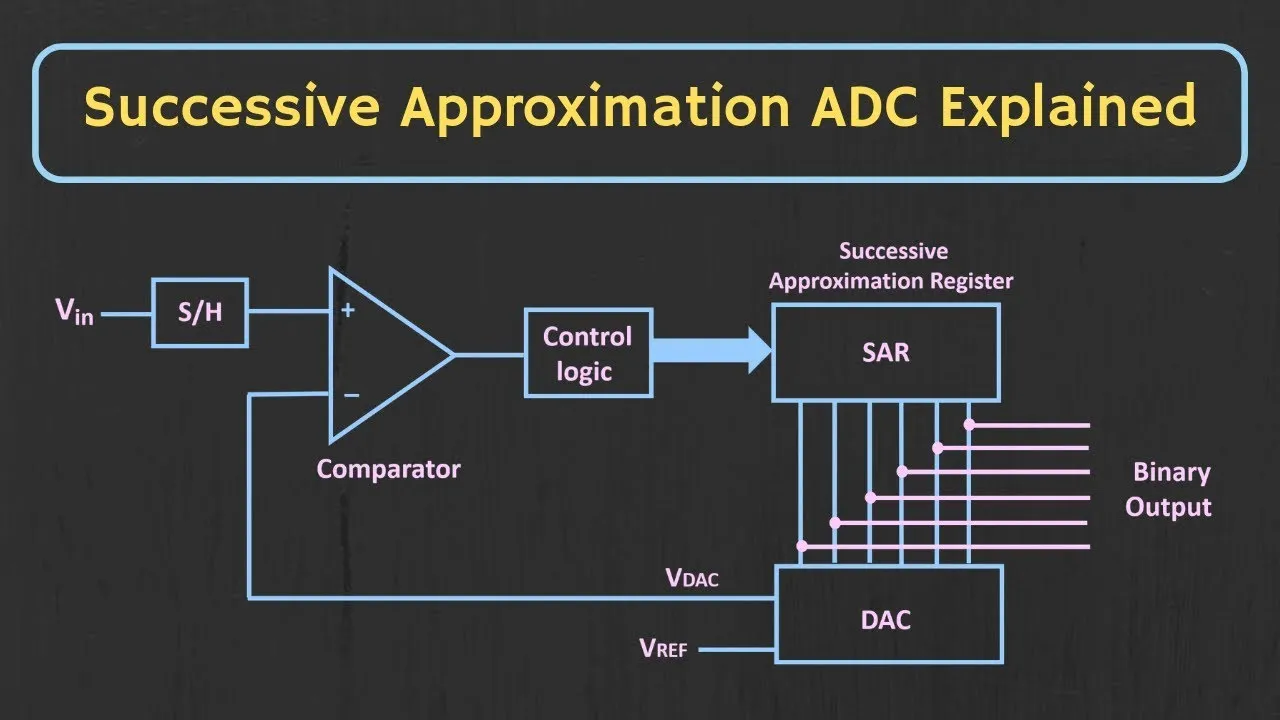

Determine the ADC input impedance (see Figure 1). The AD9246 is an unbuffered, switched-capacitor ADC, so its input impedance is time-varying and depends on the analog input frequency. Refer to the AD9246 datasheet to find the input impedance measured in track mode. In this example, the ADC’s internal input load is equivalent to a 6.9 kΩ differential resistance in parallel with a 4 pF capacitance when the ADC is in track mode and sampling.

Figure 1: The ADC internal input impedance can be modeled as a resistor in parallel with a capacitor.

Step 3: Establish ADC baseline performance

Before optimizing design parameters, establish a baseline to understand ADC behavior. Use the evaluation board in its default configuration. The ADC characteristics in the product datasheet are usually determined this way.

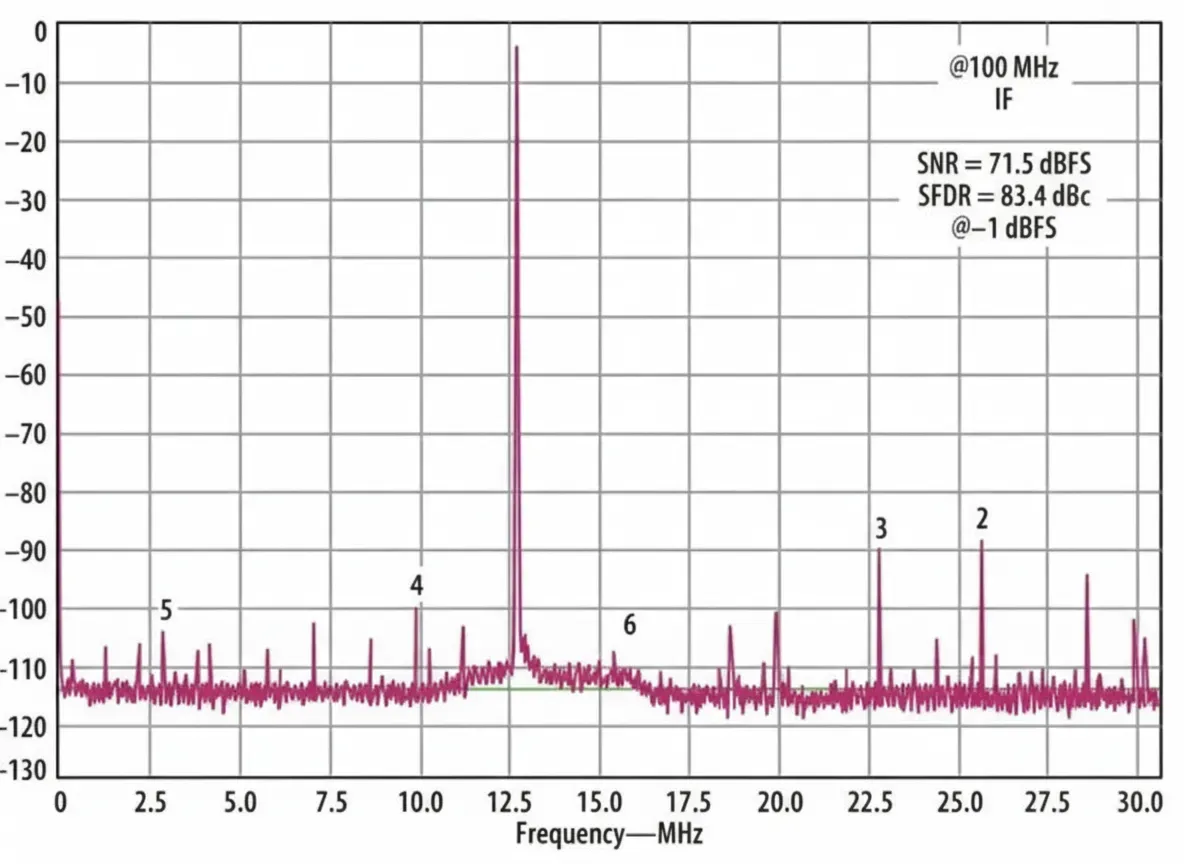

Collect baseline performance parameters: in this example, SNR is 72 dB and SFDR is 82.7 dBc, values close to the datasheet. Use a high-performance signal generator and appropriate filters when measuring to remove generator harmonics and spurious components from the test signal.

Next, remove the filter and reconnect the evaluation board directly to the test signal generator. Re-adjust the generator output level (in this example the level is +14 dBm) and record the drive required. Sweep the input frequency with sufficient bandwidth to observe passband flatness and find the -3 dB points. In this example, the default front end uses a simple RC filter producing passband flatness of 1.2 dB and an approximate bandwidth of 100 MHz.

With this data, decide on improvements. For the 72 dB SNR and 83 dBc SFDR targets, an anti-aliasing filter (AAF) is important to improve spurious performance and keep signal harmonics low. However, input drive and passband flatness remain issues. The default evaluation board AAF attenuates the band of interest too rapidly. Because a shunt inductor provides less attenuation at the frequency of interest and better roll-off outside the band, a simple shunt inductor can help. For input drive, consider a 1:4 transformer to bring the ADC closer to full scale, which adds +6 dB to the signal and reduces drive requirements. Use a vector network analyzer (VNA) to measure input impedance and VSWR and observe matching at the frequency of interest. In this example, the input impedance measured 35 Ω at 110 MHz, yielding a VSWR of 1.44:1.

Step 4: Select transformer and passive components to match the load

Select transformer and passive element values that match the load. Transformer and resistor/inductor values must be chosen so the overall AAF between the ADC and the transformer secondary meets the desired performance.

Experience and measurement are useful here. Transformer performance varies greatly, so selection is not trivial. After measuring and understanding transformer characteristics, the transformer shown in this example was chosen. Generally, choose a transformer with good phase balance. For this narrowband application with low required input drive, a common 1:4 impedance-ratio transformer was used.

Simple rules when choosing an ADC transformer include reviewing parameters such as return loss, insertion loss, and phase and amplitude balance. If these parameters are not on the datasheet, request them from the manufacturer or measure them with a VNA. Choosing a standard magnetically coupled transformer or an unbalanced transformer depends on bandwidth requirements. Standard transformers typically have bandwidths below 1 GHz, while unbalanced transformers can support much wider bandwidths.

Note that termination may be required on both primary and secondary, but in this example only the secondary was terminated to minimize component count. Depending on the application, terminating both primary and secondary could be more appropriate.

Place a series resistor of 15-50 Ω on the analog input. This example uses two 33 Ω resistors to limit reverse charge injection into the analog input of an unbuffered ADC and to help define the source impedance. A 33 Ω value works for about 90% of cases, but adjusting this resistor can slightly improve performance in some situations.

Then calculate the differential termination on the transformer secondary. Calculations indicate that differential termination starting below about 251 Ω is acceptable. An ideal 1:4 impedance-ratio transformer typically uses 200 Ω termination resistors. When beginning calculations, use the measured return loss at the center frequency to compute the actual characteristic impedance (Z0).

Keep in mind transformers vary significantly, and comparing different parts requires understanding their performance specifications. If specifications are missing, request them from the manufacturer. High-IF designs can be sensitive to transformer phase balance. Very high IF designs may require two transformers or an unbalanced-to-balanced transformer to suppress even-order harmonic distortion.

Step 5: Consider buffered vs. unbuffered ADCs and finalize tuning

Decide whether to use a buffered or unbuffered ADC. Unbuffered or switched-capacitor ADCs have time-varying input impedance and are more difficult to design around at high IF. If using an unbuffered ADC, always match to the ADC in track mode and use the input impedance table from the manufacturer. Buffered ADCs typically consume more power but are easier to design with, even at high IF. When calculating resistor and inductor values, remember these provide a good starting point. PCB layout and parasitics vary by application, so some iteration will likely be needed to meet the specific performance goals of a given design.