Overview

Depending on the hardware, calibration equations can be implemented using fixed-point or floating-point methods. Another option is to use ADCs that include integrated calibration features. Precision ADCs commonly provide several calibration modes:

- Self-calibration

- System calibration

- Background calibration

This article focuses on self-calibration features.

ADC Calibration Options

Some ADCs support built-in calibration modes, which can simplify system design and reduce processor CPU cycles. In these ADCs, the user configures the ADC, issues the appropriate calibration command, and the ADC determines offset and gain errors automatically.

The ADC typically stores the calibration results in on-chip registers and uses them to correct subsequent conversions for offset and gain. For example, the Texas Instruments ADS1246 provides offset (OFC) and full-scale (FSC) registers used to correct conversion results. The ADC subtracts the OFC value from the raw digital value, then multiplies the result by FSC and divides by 400000h for normalization.

When FSC = 800000h, the A/D result is multiplied by 2 because FSC is normalized to 1.0 at code 400000h. Users may also write values directly to OFC and FSC to control calibration behavior.

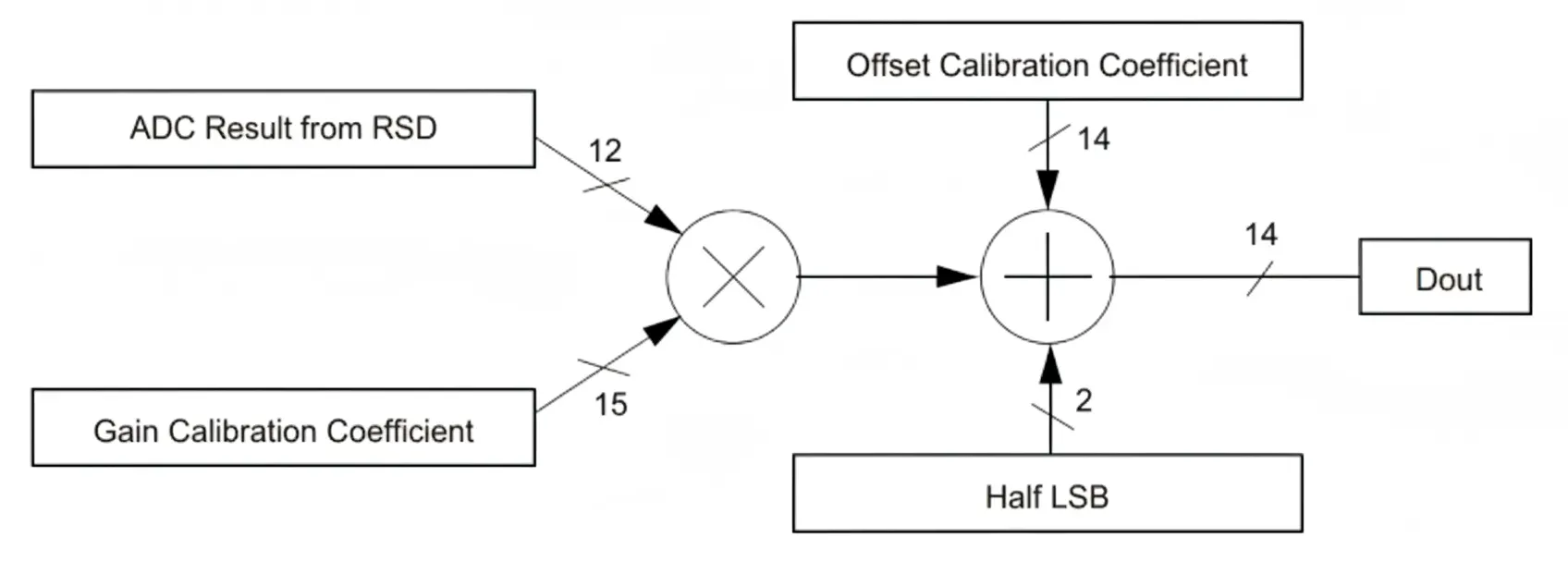

Note that most ADCs first subtract an offset calibration coefficient and then apply a gain correction. Some ADCs first adjust the slope of the transfer function and then correct the offset. For example, ADCs in the NXP MPC5500 family use a multiply-accumulate unit to implement calibration.

The two approaches above result in different offset and gain calibration coefficients for a given system. Typically, calibration involves one or two ADC conversions performed with known input voltages. The ADC uses these results to determine the transfer function offset and slope, then updates its calibration registers accordingly.

Self-Calibration or Internal Calibration

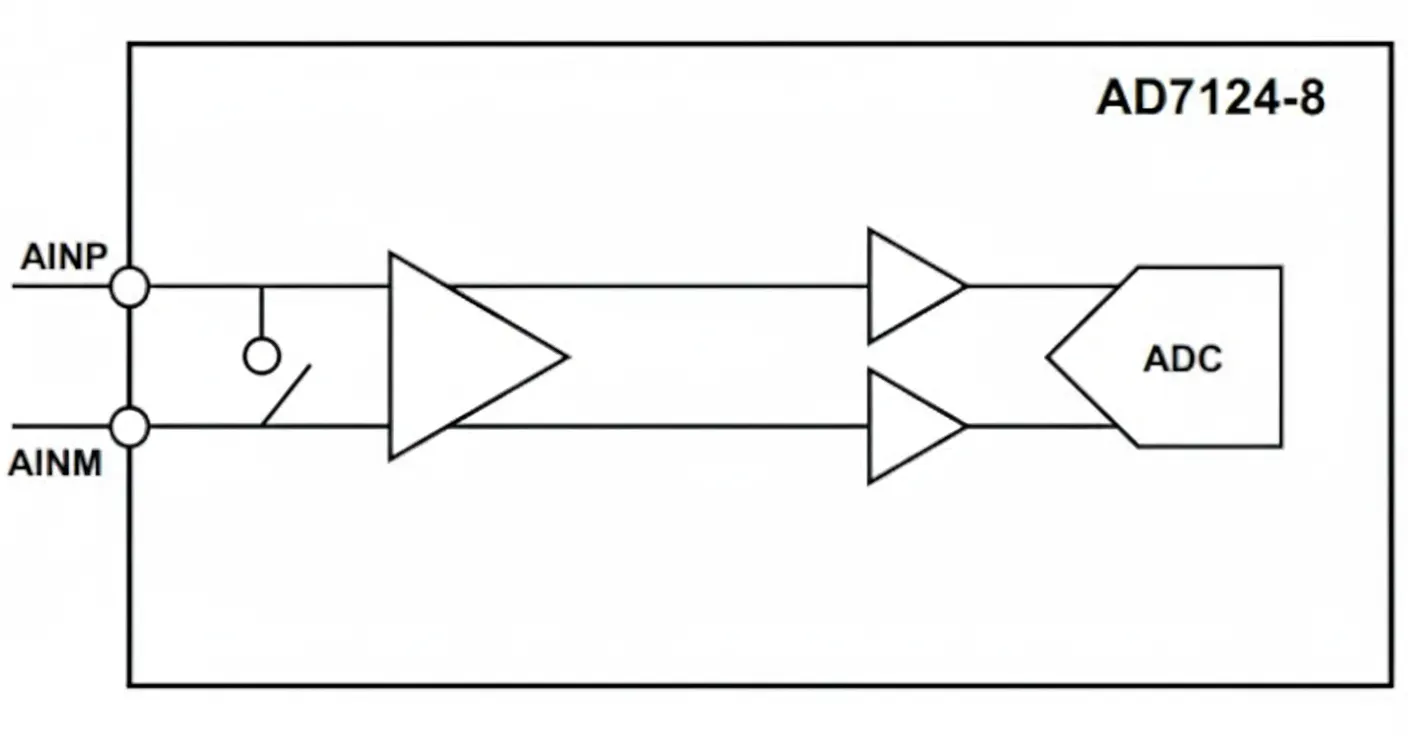

Self-calibration, sometimes called internal calibration, attempts to characterize and compensate offset and gain errors generated by internal ADC modules. For example, in delta-sigma ADCs with an integrated PGA, self-calibration can remove DC errors from the PGA and delta-sigma modulator. Some devices, such as the AD7124-4, support both offset (zero-scale) and gain (full-scale) self-calibration. Other devices, such as the AD7172-2, provide only offset calibration in their self-calibration routine.

Internal Offset Calibration

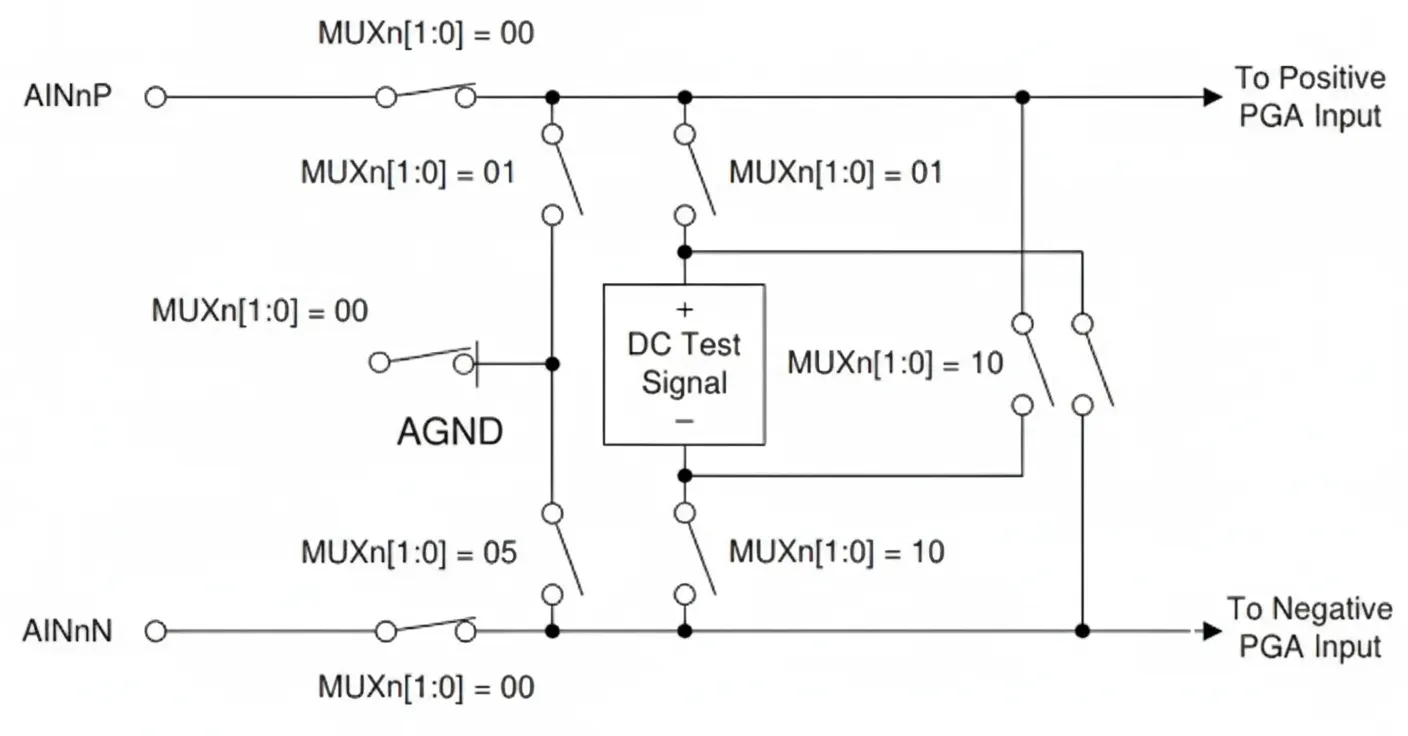

For internal offset calibration, the selected ADC input channel is internally shorted. The ADC compares the encoded output to the ideal value to determine offset error. Many ADCs integrate input multiplexers to disconnect the inputs from external circuitry and connect them internally to a common voltage for offset calibration. For example, the ADS1260-Q1 provides a multiplexer that shorts both inputs to ground for offset calibration. The ADS131M06 has a simpler input multiplexer with a configuration that shorts both inputs to ground for offset calibration.

Some ADCs disconnect only one input from the external circuit. For example, the AD7124-4 internal connection diagram shows that during offset calibration both inputs are shorted together, but the negative input may remain connected to the external circuit. Designers must ensure no extraneous noise or interference appears on that input during offset calibration and that the input voltage stays within ratings during calibration.

Internal Full-Scale Calibration

Full-scale calibration is usually performed by applying an internally generated full-scale voltage to the ADC input. If the ADC input range is ±Vref, the internal connection is made to +Vref and -Vref lines. Knowing the input is at full-scale, the ADC determines the required gain calibration coefficient. If the ADC includes an integrated PGA, the internally generated voltage is often Vref divided by the PGA gain to avoid overrange. This allows internal full-scale calibration at each gain setting.

ADC calibration routines often repeat zero-scale and full-scale measurements multiple times (for example, 16 times) and average the conversion results. Averaging reduces conversion noise and increases calibration accuracy.

Effectiveness of ADC Self-Calibration

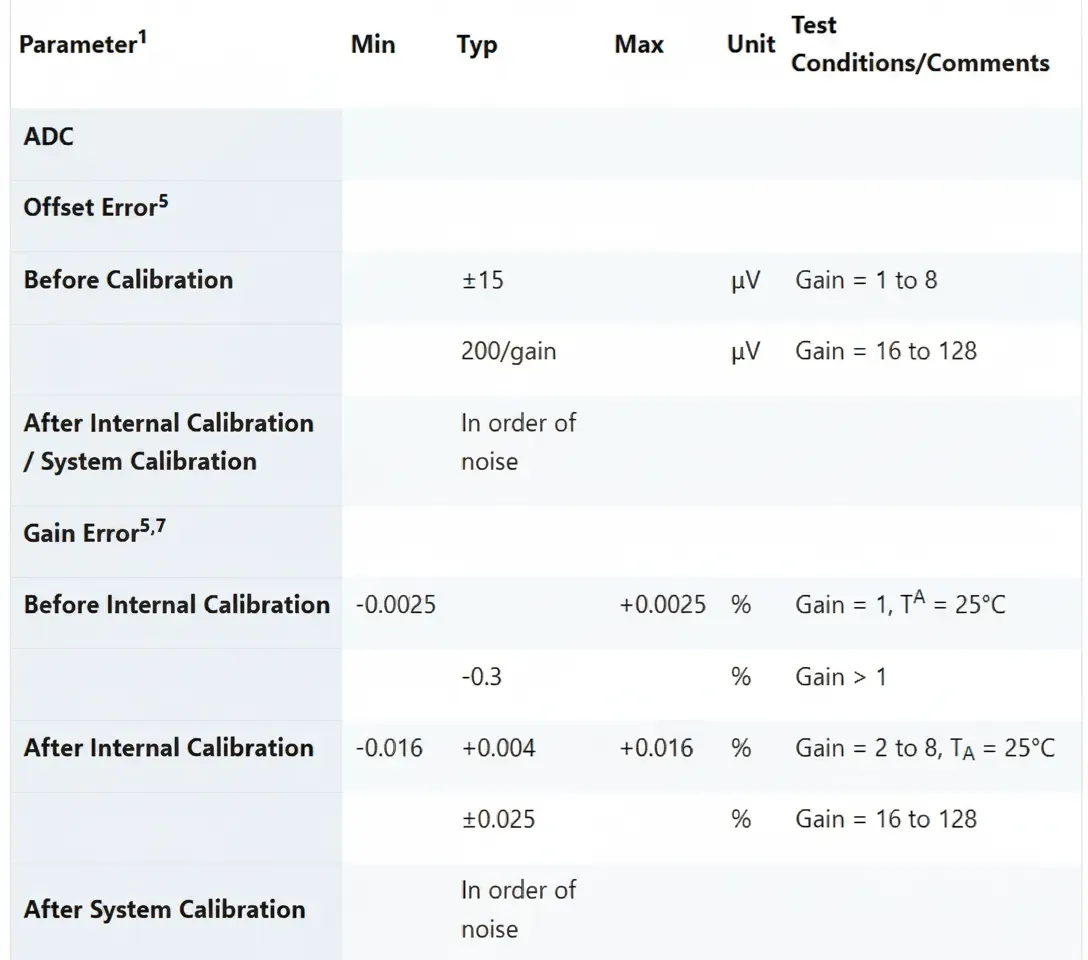

The AD7124-4 datasheet provides example calibration data. Before offset calibration, the ADC offset may be on the order of ±15 μV. After offset calibration, residual offset is on the order of the device noise; the datasheet shows noise below 400 nV RMS. Gain calibration can also significantly reduce ADC gain error.

The example uses the AD7124-8. Without calibration, measurement error exceeds the expected Pt100 response. A one-time calibration of ADC offset and gain at 25°C brings the measurement error within the expected range. Note that external circuit-induced offset and gain errors are not eliminated by ADC-only calibration. For a complete view of calibration effects in common RTD configurations, refer to the ADI reference design.

As the RTD example and reference design results indicate, many applications meet accuracy targets by removing ADC offset and gain errors alone. For higher precision requirements, system calibration is often needed to remove offset and gain errors introduced by the ADC and external circuitry.

Estimating ADC Error: How System Calibration Helps

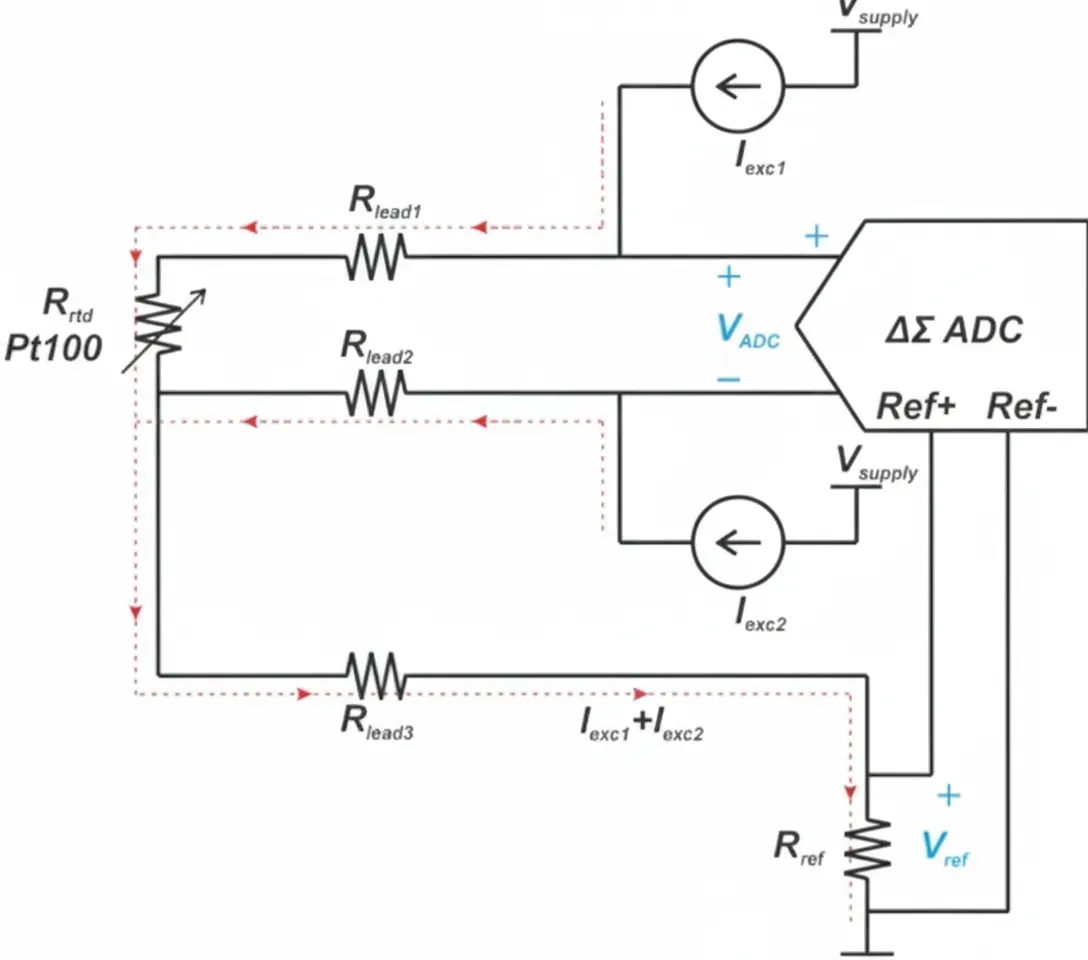

Consider a 3-wire, ratiometric RTD measurement system. Assume excitation currents Iexc1 and Iexc2 are 0.5 mA and the reference resistor Rref is 1.6 kΩ, producing a 1.6 V reference. Major external error sources include:

- DC offset and gain error

- ADC integral nonlinearity (INL)

- Tolerance of the reference resistor

- Mismatching of Iexc1 and Iexc2

If excitation currents are well matched or current reversal techniques are used, current mismatch can be neglected. The dominant external error source then becomes the tolerance of Rref.

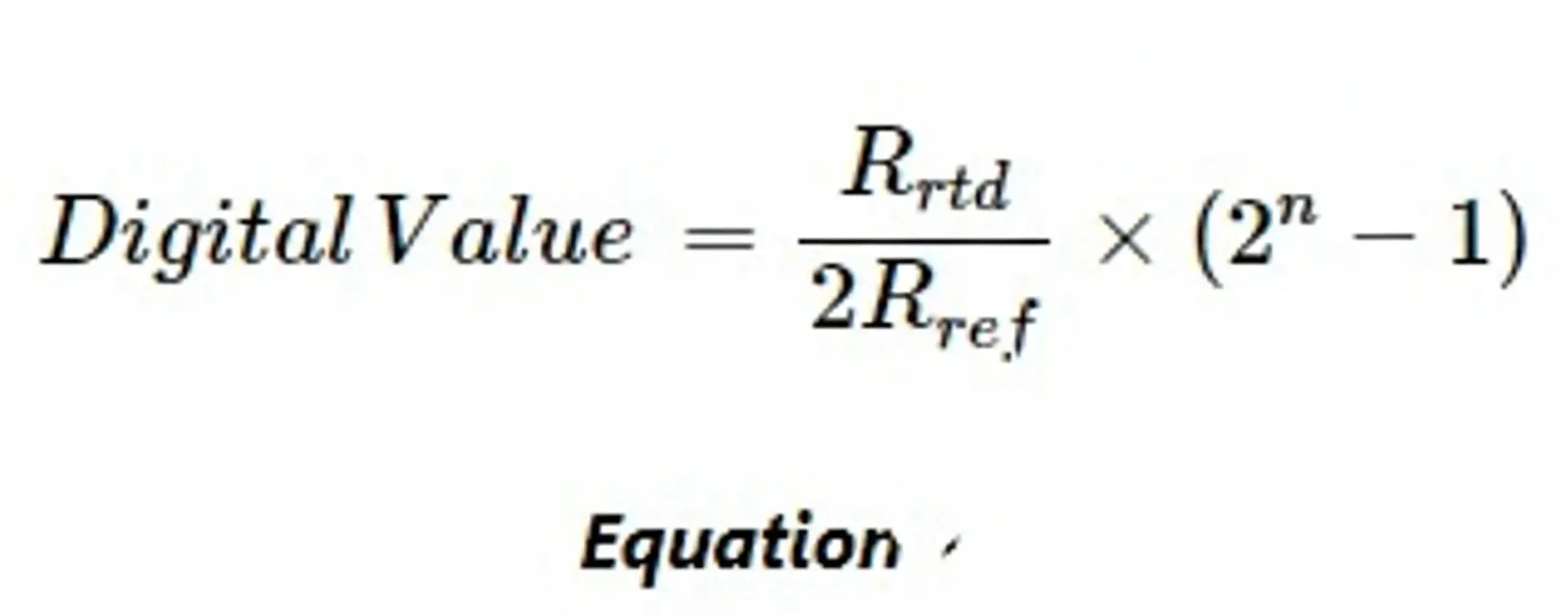

Using the ratiometric circuit, the ADC digital output for an n-bit ADC can be expressed as shown in the diagram below.

Assuming Iexc1 = Iexc2, the expression simplifies to:

Comparing this with the ideal relation shows that a small error in Rref causes the same fractional error in the system transfer function slope. For example, a 0.1% reference resistor tolerance (α = 0.001) produces a 0.1% system gain error. That gain error can be comparable to ADC gain error, depending on the ADC chosen.

For example, the ADS1260-Q1 has a maximum uncalibrated gain error of 0.6%. For demanding applications, system calibration can substantially improve accuracy. For further details on error sources in RTD applications, see the Texas Instruments reference design. The next article will continue the discussion and examine system calibration and background calibration modes in precision ADCs.