Overview

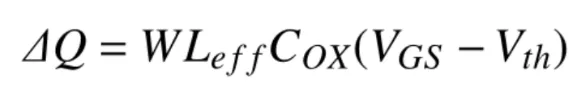

In ADCs, sampling-switch induced errors are mainly caused by two factors: charge injection and nonlinear on-resistance. Charge injection is caused by creation and removal of the conduction-channel charge when a MOSFET conducts. When a MOSFET operates in the triode region, the channel charge is:

Charge Injection

When the switch turns off, the channel charge must disappear. That charge can only flow into the MOSFET's source or drain, affecting the voltages at both terminals. Consequently, charge that flows onto the sampling capacitor produces an offset. The offset magnitude depends on several factors, such as process, transistor size, input voltage, and switching timing. Crucially, the offset is input dependent, which leads to harmonic distortion during sampling.

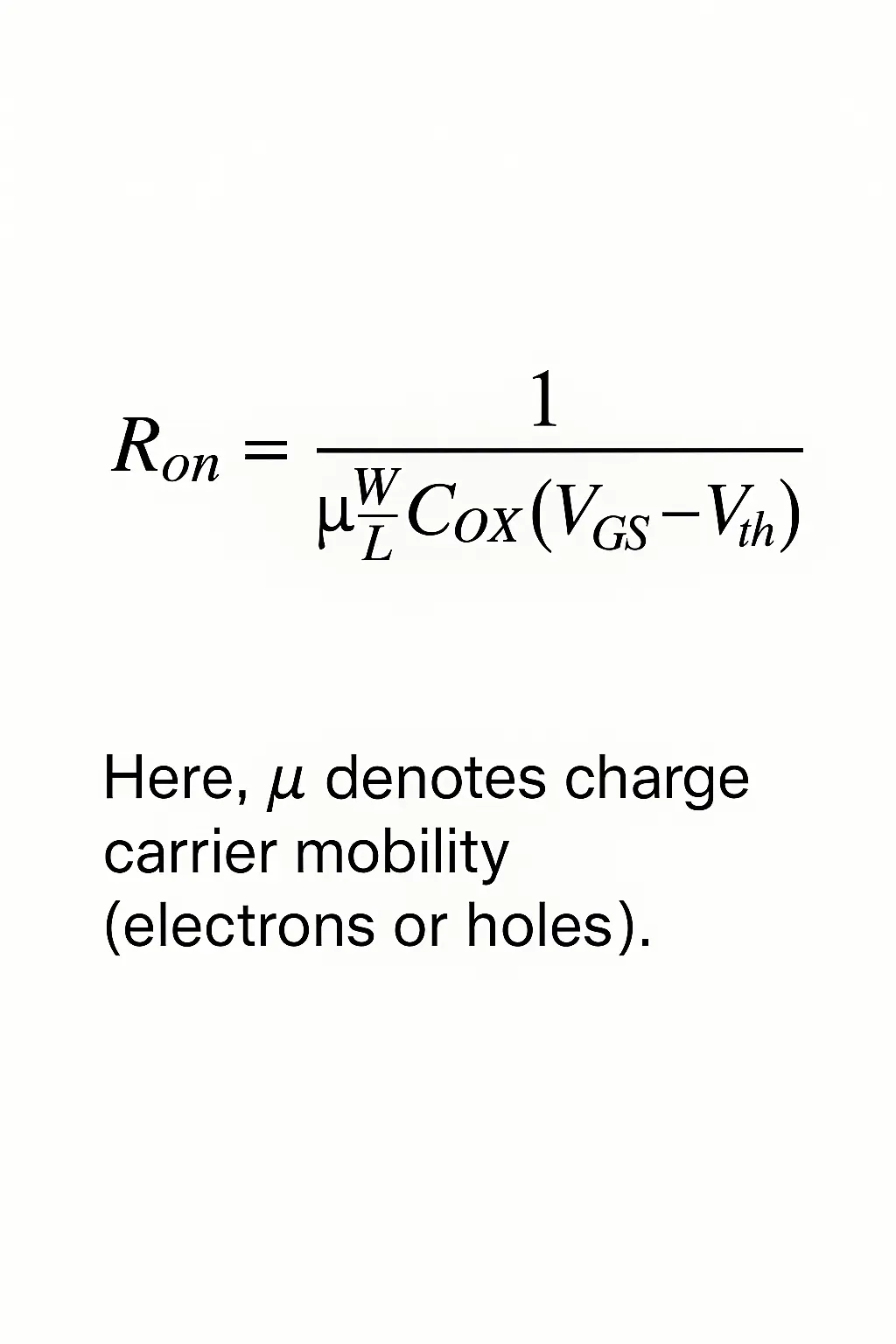

On-Resistance Nonlinearity

Nonlinear on-resistance is mainly caused by the dependence of the switch on-resistance on the input signal. The plot below shows the on-resistance magnitude:

As shown, when VS = VIN, the overdrive voltage VGS is a function of the input voltage in both cases.

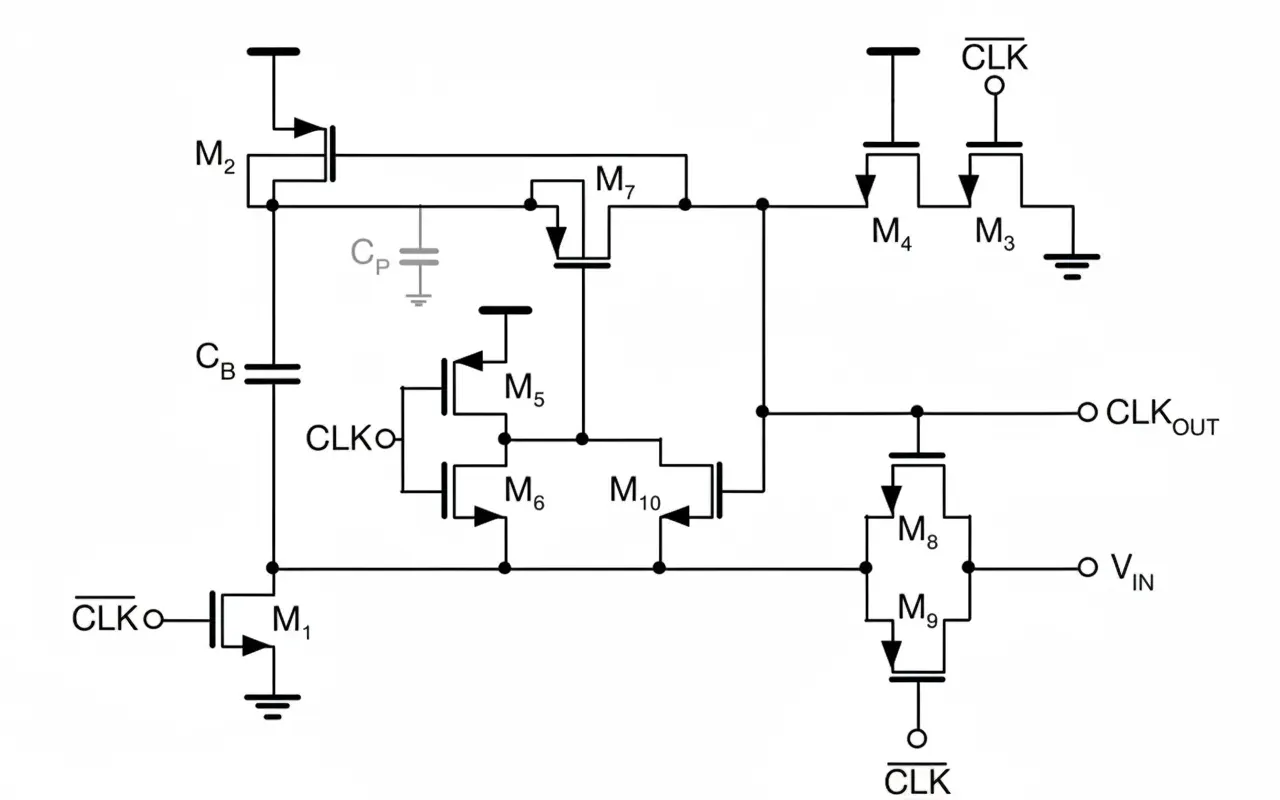

Gate Bootstrap Circuit

The gate bootstrap circuit below can, in theory, remove VGS dependence on the input signal by making VGS approximately constant. That improves on-resistance linearity and reduces harmonic distortion.

Figure 1 Gate bootstrap circuit

Operation details:

- When CLK = 0, capacitor CB is precharged to VDD by M1 and M2. M3 and M4 pull CLK_OUT to ground, turning off M8 and M10, while M5 turns off M7.

- When CLK = 1, M6 turns on M7, and M7 turns on M8. M8 and M9 receive VIN at the bottom plate of CB, which causes the top plate of CB to become VDD + VIN and allows M7 to drive that value to CLK_OUT. In practice, this voltage is attenuated by a parasitic capacitor CP. The parasitic is mainly formed by body parasitics of M2 and M7 and routing capacitance. Therefore there is a trade-off between the bootstrap effectiveness and the maximum achievable sampling speed.

- M4 reduces the VDS and VGS stress on M3 during CLK = 1 to prevent overvoltage. M4 and M3 are usually sized large enough to avoid introducing excessive jitter noise on the falling edge of the sampling clock. M10 ensures M7 remains conductive throughout the sampling phase.

Note: M9 is optional. It acts as a virtual switch to balance the load seen at CLK_OUT and to ensure symmetry with the subsequent stage.