1. What is a chip IO circuit?

In simple terms, an IO circuit refers to the chip's signal input/output interface circuitry, typically located at the periphery of the chip layout. IO circuits generally provide the following functions:

- Level shifting

- Increasing drive capability

- ESD protection

Level shifting is used when the internal logic voltage levels differ from external requirements; the IO circuit converts between levels. Drive capability is important, especially for digital chips: a single output may have multiple fan-outs and drive capacitive loads, so sufficient drive strength prevents excessively slow rising/falling edges. ESD protection is essential for IO circuits to prevent damage from electrostatic discharges.

2. IO circuit classifications

Input IOs are relatively simple. They can be divided into types with or without pull-up/pull-down resistors. A typical input IO is a buffer built from an inverter. Without an external drive, a pull-up keeps the input default high and a pull-down keeps it default low. Because pull resistors are usually weak, they do not affect the signal when an external drive is present.

Output IOs are generally divided into three types.

First is the push-pull output structure, the common inverter-type driver.

Second is the OC/OD (open-collector / open-drain) output structure. This topology cannot directly drive a high level; a pull-up resistor must be added externally at the open end.

OC/OD outputs have the following characteristics:

- They allow convenient adjustment of the output high level and provide flexible level shifting.

- They can implement wired-AND (line-AND) functions.

- They introduce rise-time delay related to the chosen external pull-up resistance.

Third is the tri-state output structure. Compared with a standard gate that has only 0 and 1 states, a tri-state gate adds a high-impedance state. There are unidirectional and bidirectional tri-state variants.

In the high-impedance state the output resistance is very large, effectively open-circuit, which disconnects the gate from the connected circuit. Thus tri-state gates extend output functionality and can act as controlled switches. This structure is commonly used for bus connections, where the bus should have only one active driver at a time. Multiple devices on a data bus use OE/CE or similar signals to enable their outputs; when a device is not enabled it remains in high-impedance and does not affect other devices on the bus.

3. Key challenges in IO circuit design

Although IO circuit principles are straightforward, a major design challenge is managing ground bounce. Optimizing ground bounce behavior is the difficult part of IO design.

Ground bounce refers to variations of the chip's internal ground potential relative to the PCB ground. From the PCB ground reference, the chip internal ground appears to jump, hence the term ground bounce.

Ground bounce is caused by package parasitic inductance. If the package parasitic inductance is ignored, the chip ground could be seen as an ideal ground. In reality, there is a parasitic inductance between the chip ground and the external PCB ground. When inverters switch dynamically, transient current changes induce a voltage across that inductance, producing observable ground bounce.

Why is ground bounce problematic? It can cause the IO circuitry to misinterpret external high/low input levels. For example, under CMOS thresholds an external 2.0 V input might be intended as a logical high, but ground bounce could cause the chip to detect it as low or produce intermittent toggling. Such behavior leads to functional failures.

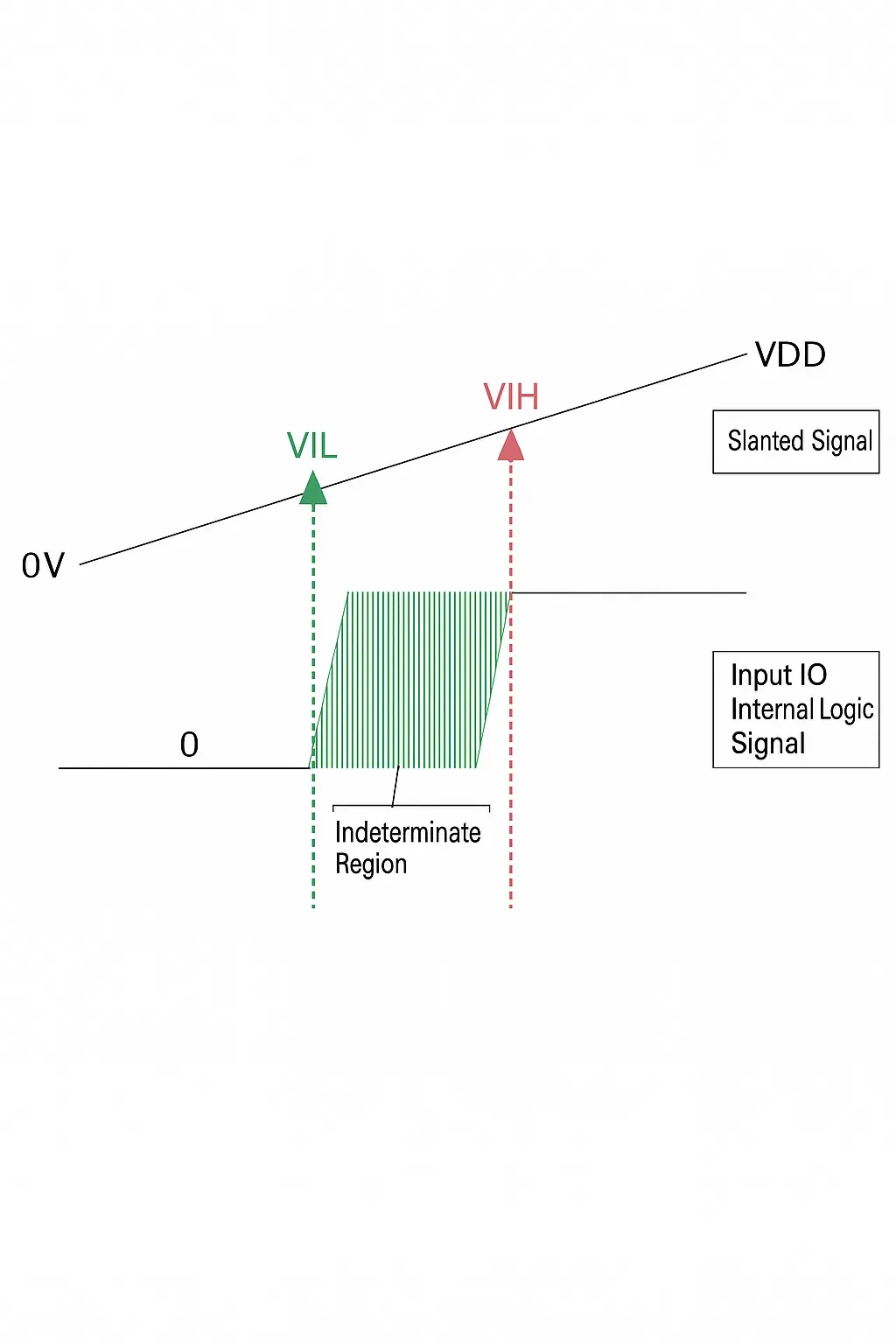

Therefore, IO design must ensure correct detection of input high and low levels under ground bounce conditions, i.e., also guarantee that VIH/VIL meet datasheet specifications when ground bounce occurs.

4. Methods to measure VIH/VIL under ground bounce

There are two simulation measurement methods; both can be automated via formulas. The first applies a ramped input signal, as shown below.

Figure 6 Input ramp measurement method

When using a ramp, the input value at the first incorrect switching of the input IO corresponds to VIL, and the input value at the last incorrect switching corresponds to VIH. The ramp must be sufficiently slow for accurate measurement. A practical guideline is slope K = 10 mV / (2T), where T is the switching period; that is, the voltage change over two switching periods is 10 mV. A smaller slope yields more accurate results but increases simulation time.

The second method uses a stepped input signal, as shown below.

Figure 7 Step input measurement method

With the step method, the value of the step before the first incorrect switching corresponds to VIL, and the value of the step after the last incorrect switching corresponds to VIH. The step size must be sufficiently small for accurate measurement. A practical guideline is STEP = 10 mV / (2T), where T is the switching period; the voltage change represented by a step is 10 mV. A 10 mV resolution is acceptable; smaller steps increase accuracy but also simulation time.

Both methods produce consistent results. The ramp method requires reducing the slope for accuracy, which increases simulation time. For PVT simulations, the step method is often recommended because an efficient approach preserves only the edge regions of interest instead of all intermediate steps. Since VIH and VIL extremes in PVT simulations are typically within the edge ranges, this approach can accelerate simulations without sacrificing accuracy.