Supply disruptions and the growing automotive electronics market

In 2018 the automotive industry experienced an unexpected shortage of semiconductor components that later affected many electronic component categories. After several years of upstream capacity expansion and recent weakness in vehicle demand, shortages have eased, though some vehicle-grade main control chips still face extended lead times.

Market growth driven by vehicle electrification and intelligence

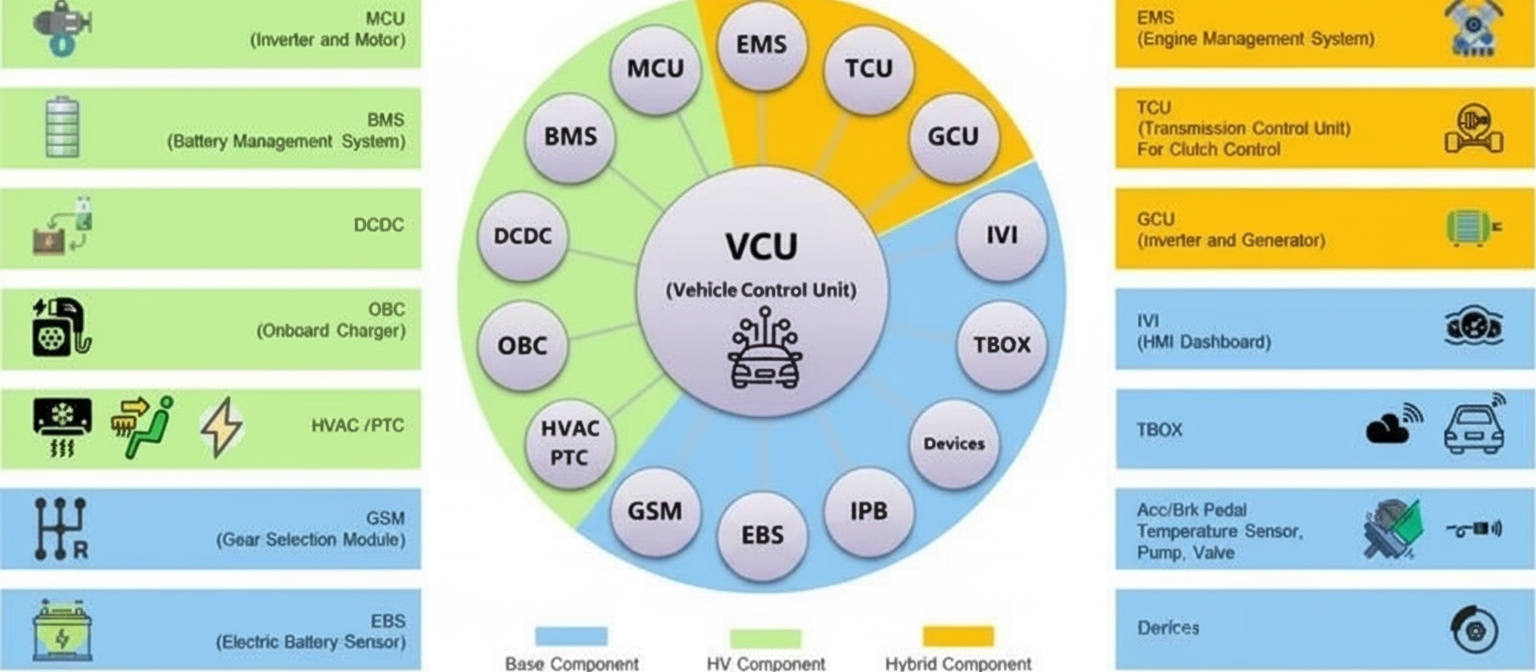

The root cause of the shortages was not only cyclical supply issues but also the rapid increase in demand driven by vehicle electrification and intelligence, which transformed vehicle electrical/electronic architectures. This rising incremental market outpaced available supply of automotive-grade chips, triggering shortages and price pressure.

Automotive chips fall into three main categories: functional chips, power devices, and sensors. In conventional internal-combustion vehicles, the average chip count is about 500–600 chips per vehicle. With electrification and intelligence, that figure has risen to roughly 1,000 chips per vehicle; in new-energy vehicles it exceeds 2,000 chips per vehicle. As electric vehicles become more intelligent, chip counts could rise to 3,000 per vehicle or more.

Commercial focus: L2 and L2+ as short-term industry consensus

Autonomous driving technology has progressed rapidly in recent years. Some manufacturers now offer vehicles with L2-level automated driving features, such as Tesla Model S, GAC Aion S, XPeng G3, NIO ES8, FAW-Volkswagen Tanyue, Changan CS75, WEY VV6, and Geely Binrui.

There are two commonly referenced classification systems for driving automation. One is the SAE J3016 standard released in 2014, "SAE J3016: Taxonomy and Definitions for Terms Related to Driving Automation Systems for On-Road Motor Vehicles," often referred to as the SAE levels. The other is the national standard released in 2021 by China’s State Administration for Market Regulation and the Standardization Administration. The national standard groups L1–L2 as driver assistance and L3–L5 as automated driving. The following summarizes the SAE levels.

SAE driving automation levels (L0–L5)

L0: No automation. Fully manual driving.

L2: Partial automation. The system can perform certain driving tasks, but the driver must remain attentive to the road and be ready to intervene if the system fails. Typical features include adaptive cruise control, active lane keeping, automatic emergency braking assistance, and automated parking.

L3: Conditional automation. The vehicle can handle driving in specific scenarios with system priority over the driver, but the driver can regain control using an intervention mechanism. Examples include automated follow-in-traffic and remote reverse parking. The Audi A8, for instance, was equipped with many sensors and dozens of driver assistance software functions to support L3 capabilities.

L4: High automation. Within defined roads and environments, the system can perform all driving tasks and manage emergencies without human intervention. The driver is not required to monitor driving, and traditional controls may be removed in some designs.

L5: Full automation. The system can handle all driving tasks in all conditions without any human intervention; the concept of a driver’s cockpit may no longer apply.

Before 2022 many firms across the automotive supply chain did not clearly define target scenarios and therefore relied on increasing compute to provide hardware redundancy. As development moves from L2 toward L3 and above, the main challenge for large-scale deployment is the demand-side acceptance and cost control required by OEMs. Industry experience over recent years indicates that L2 and L2+ automated driving will become a standard offering for many OEMs, which has become an industry consensus.

Technical evolution: large SoCs becoming standard

As autonomous driving advances, not only has the number of in-vehicle chips increased, but in zonal/consolidated and centralized computing architectures large chips have become standard, and chip design complexity has risen sharply.

From 2014 to 2018 distributed E/E architectures dominated while cross-domain centralized architectures began to emerge. Early mainstream suppliers such as Mobileye, NVIDIA, Renesas, TI and other MCU vendors offered vehicle-mounted ADAS compute mostly below 10 TOPS. For example, Mobileye EyeQ3 and EyeQ4 provided approximately 0.256 TOPS and 2.5 TOPS respectively.

There are exceptions: NVIDIA’s Tegra Parker SoC in the Tesla HW2.0 platform reached about 24 TOPS and helped establish the GPU-based SoC approach for autonomous driving.

From 2019 to 2023, development of cross-domain centralized architectures accelerated and NVIDIA began to lead the high-compute segment. Tesla’s in-house FSD chips and domestic suppliers such as Horizon Robotics, Black Sesame, and Xinchi began to pursue market opportunities. Compute demands diverged according to application scenarios and OEM positioning. The consensus emerged that L2/L2+ delivers stronger near-term commercial value, prompting intense market competition in that segment.

In the mid-to-high compute L2/L2+ market, compute requirements range roughly from 30 TOPS to 1,000 TOPS. Examples include NVIDIA Xavier (30 TOPS) used in some L2 vehicles, Horizon Robotics J5 (128 TOPS) used by several OEMs, and NVIDIA Orin (256 TOPS) targeted at higher-end assisted-driving models. The arrival of high-compute SoCs such as Orin exerted pressure on many autonomous-driving chip vendors including Mobileye, Horizon, Qualcomm, Black Sesame, and Cambricon.

EDA is helping automotive chip vendors achieve performance and time-to-market

For designers of large automotive SoCs, reducing time-to-market while improving compute and safety and optimizing PPA (power, performance, and area) is critical.

Traditional EDA workflows often rely on rule-of-thumb methods and designer experience for optimization. Such modeling and simulation approaches have limitations: they cannot fully leverage prior designs for insight, iterative cycles increase design time, HLS can demand longer synthesis times, placement and routing depend heavily on designer predictions, and manufacturing costs are high in terms of time and resources. Automotive-grade chip quality also depends heavily on underlying semiconductor technology and design rules, raising the bar for EDA solutions.

For large automotive SoCs, extensive simulation and verification prior to fabrication is necessary. As compute scales and integration density increase, verification complexity grows, requiring faster convergence and validation to reduce costs and improve result quality. Traditional ATPG approaches also struggle to meet fault coverage requirements. Integrating AI with EDA workflows is therefore an important trend.

Cadence provides a portfolio of EDA tools and design flows for automotive intelligent design, and offers tools that integrate AI/ML capabilities to move from manual to increasingly automated optimization. These tools aim to support multidisciplinary analysis and optimization to improve design outcomes, accelerate verification convergence, and support more precise system behavior modeling for improved product fidelity and safety.

Tensilica processor IP

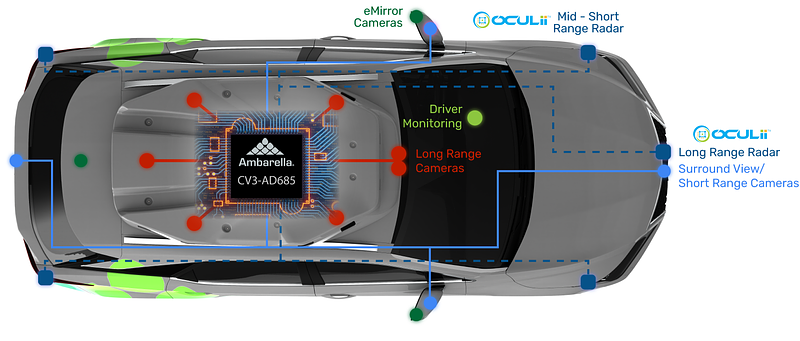

Tensilica processor IP is a configurable processor family intended to meet a range of ADAS hardware acceleration needs. The Tensilica ConnX DSP core is positioned for high-performance data processing in L2-level ADAS LIDAR and millimeter-wave radar, offering a balance of performance, power, and area. Integration of Tensilica Vision DSP and Tensilica AI processors supports visual sensor data processing.

Integrating Tensilica DSP products into an SoC enables rapid software/hardware partitioning exploration, reduces load on CPU, GPU, and AI processors as algorithms evolve, and supports automated generation of processor extensions using the Tensilica Instruction Extension (TIE) language with matching software tools to create domain-specific solutions.

Tensilica Xtensa processors with FlexLock have achieved automotive safety certifications and meet ASIL-D requirements for system-level and random fault protection, applicable to functional safety applications. This enables SoC designers to integrate safety modules and reduce module design and verification time.

For example, a radar module SoC typically comprises multiple processing elements including a controller CPU and one or more DSPs. Random faults can occur in transistors or other physical elements, leading to permanent or transient faults that affect logic or memory bits. System designers must set safety goals, such as preventing random DSP faults from causing missed lane-marking detection. Safety mechanisms must notify a safety controller to take actions like reinitializing the DSP. The safety controller itself may be subject to faults, so redundancy and synchronized controllers are common design choices to reduce failure risk.

Given the complexity of processor design for system-level safety targets, SoC designers commonly license IP from third parties to simplify design flows and improve tape-out success rates; Tensilica processor IP is one such option.

Xcelium ML

Xcelium Logic Simulation is a simulator intended to accelerate convergence for IP and SoC verification, supporting SystemVerilog, VHDL, SystemC, e, UVM, mixed-signal, low power, and X-propagation with a high-performance core to increase verification throughput.

The Xcelium Machine Learning (ML) App uses proprietary machine learning techniques to shorten regression time by learning from previous regression runs and guiding the random stimulus engine. This can substantially reduce simulation regression cycles for equivalent coverage, or increase bug discovery for specific coverage points to improve verification quality.

Cadence also offers domain-specific apps, including mixed-signal, ML-based test compression, and functional safety apps, to help automotive chip design teams achieve verification convergence earlier, which is suitable for Level 2+ and above SoC designs.

Renesas reported that integrating the Xcelium ML App into their verification flow helped accelerate coverage convergence with fewer regression runs while improving verification performance and efficiency. Using AI-driven verification tools contributed to substantial reductions in regression runs and overall verification time.

Conclusion

The automotive industry transformation continues, and the importance of chips and electronic systems will increase. Overcoming emerging challenges will require cooperation across the supply chain, with EDA and IP providers playing important roles in enabling automotive SoC development and verification.