At IMAPS DPC 2024, Yole analysts Rayane Mazari and Gabriela Pereira presented an analysis of smartphone SoCs. The following summarizes their findings on the application of fan-out packaging in smartphone application processors (APUs) and its potential impact on future phone designs.

Part 1: Smartphone APU market overview

According to Yole Group data, the smartphone APU market is expected to remain stable over the next few years. Major smartphone APU designers include Qualcomm, Apple, and MediaTek. Although overall smartphone market growth has slowed, demand for high-performance APUs in premium devices remains robust.

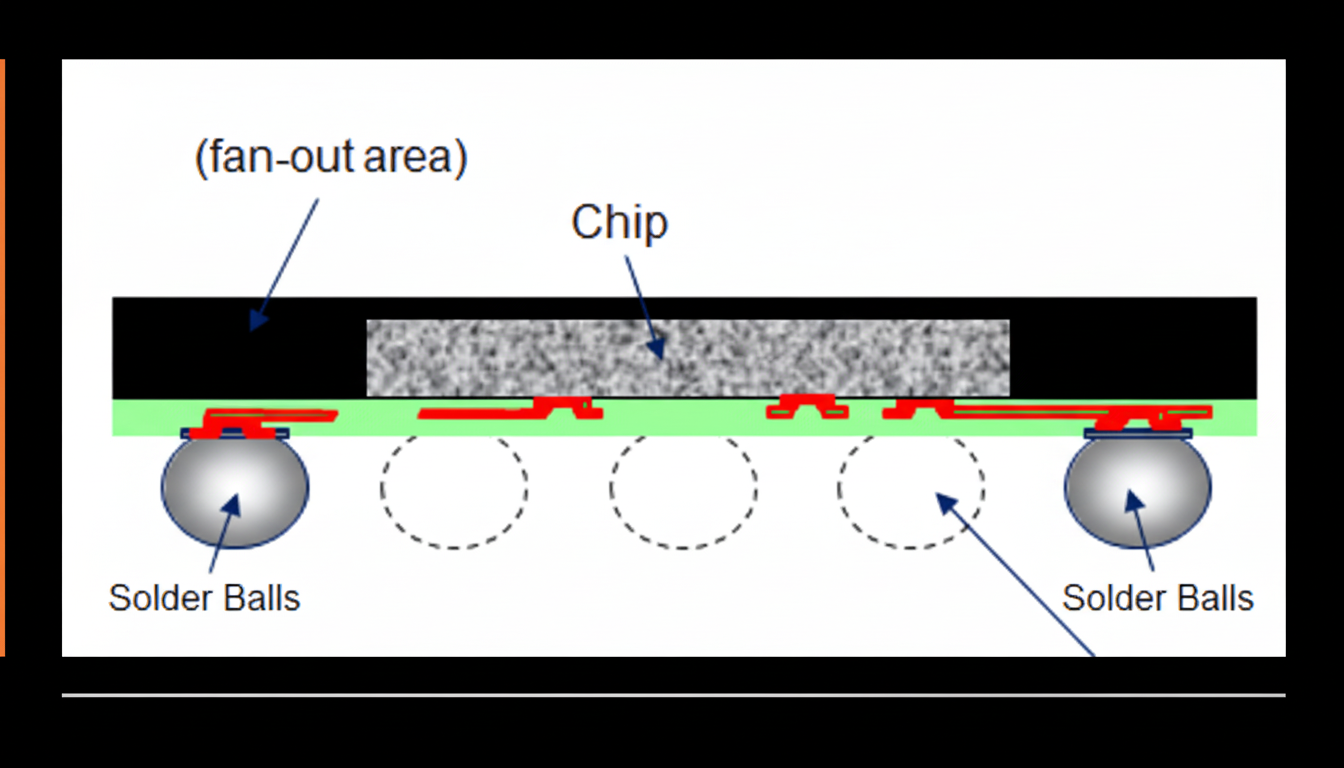

What is fan-out packaging?

Fan-out packaging is an advanced packaging technique that enables additional I/O points to be formed outside the wafer footprint, increasing chip functionality and performance. Compared with traditional wafer-level packaging, fan-out packaging can provide improved electrical and thermal performance while enabling smaller package sizes.

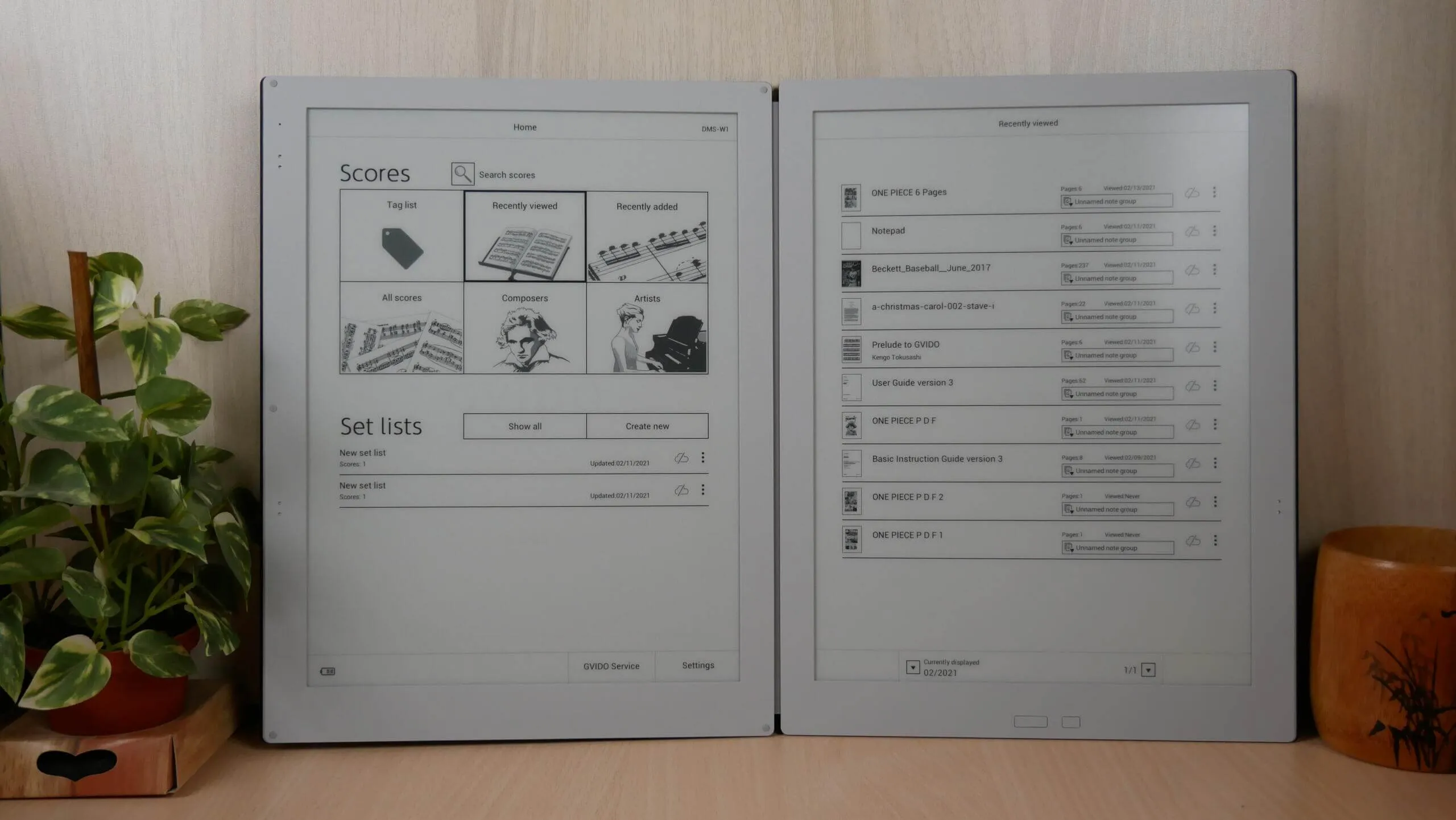

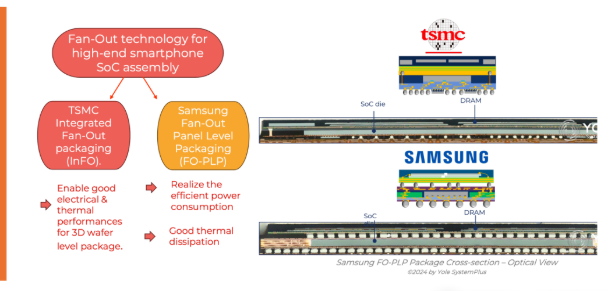

Fan-out in high-end smartphones

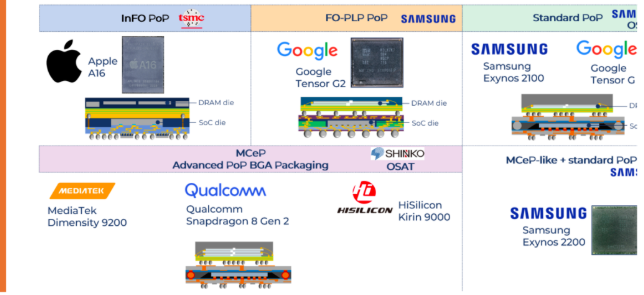

Samsung and TSMC are leading suppliers of fan-out technology. For example, the Google Pixel 7 Pro uses a Google Tensor G2 SoC packaged using Samsung's fan-out process. This packaging improves SoC power efficiency and thermal dissipation, and enables package-on-package (PoP) stacking with DRAM for integration on smartphone mainboards.

Part 2: Cost analysis and market outlook

Fan-out packaging offers performance gains, but cost remains a key consideration. Yole Group's analysis indicates fan-out packaging costs are gradually declining, and by 2028 average selling prices (ASPs) for fan-out packages are expected to compete with other package types. The fan-out market is growing rapidly.

TSMC and Samsung are the main suppliers in the fan-out packaging market. By 2024, major APU designers such as Qualcomm, MediaTek, and Huawei's HiSilicon may adopt fan-out WLP (wafer-level package) and PLP (panel-level package) solutions for smartphone APUs.

Future directions for fan-out development include using additional redistribution layers (RDLs) to increase interconnect density, and reducing system cost while improving performance through die partitioning and chiplet approaches. Integration methods such as side-by-side integration, 3D stacking, through-silicon vias (TSVs), and hybrid bonding will also drive fan-out evolution.

Summary

Fan-out packaging is becoming a key technology for high-end smartphone SoC packaging. It improves device performance and points the way for future packaging developments. As costs decline and the technology matures, fan-out packaging is likely to play an increasingly important role in future smartphone designs.