Evoked potentials are specific electrical responses produced by the nervous system following various external stimuli. They can be detected at corresponding sites in the central and peripheral nervous systems. Because these potentials are time-locked to the stimulus, they provide quantitative and spatial information and are often more stable than conventional electroencephalography, making them valuable for diagnosing and studying electrophysiological changes in neural structures.

Introduction

This project generates auditory and visual stimulus signals at specified frequencies to elicit evoked potentials in the human brain. Clinicians can extract additional information from the elicited EEG to assist diagnosis. The stimulator can produce audio and video stimuli. Audio stimuli include short clicks, pure tones, or recorded sounds; video stimuli include a chessboard pattern reversal. Stimulus duration and frequency are configurable. The implementation uses an FPGA and associated chips, and the development platform is the ALTERA DE2 board.

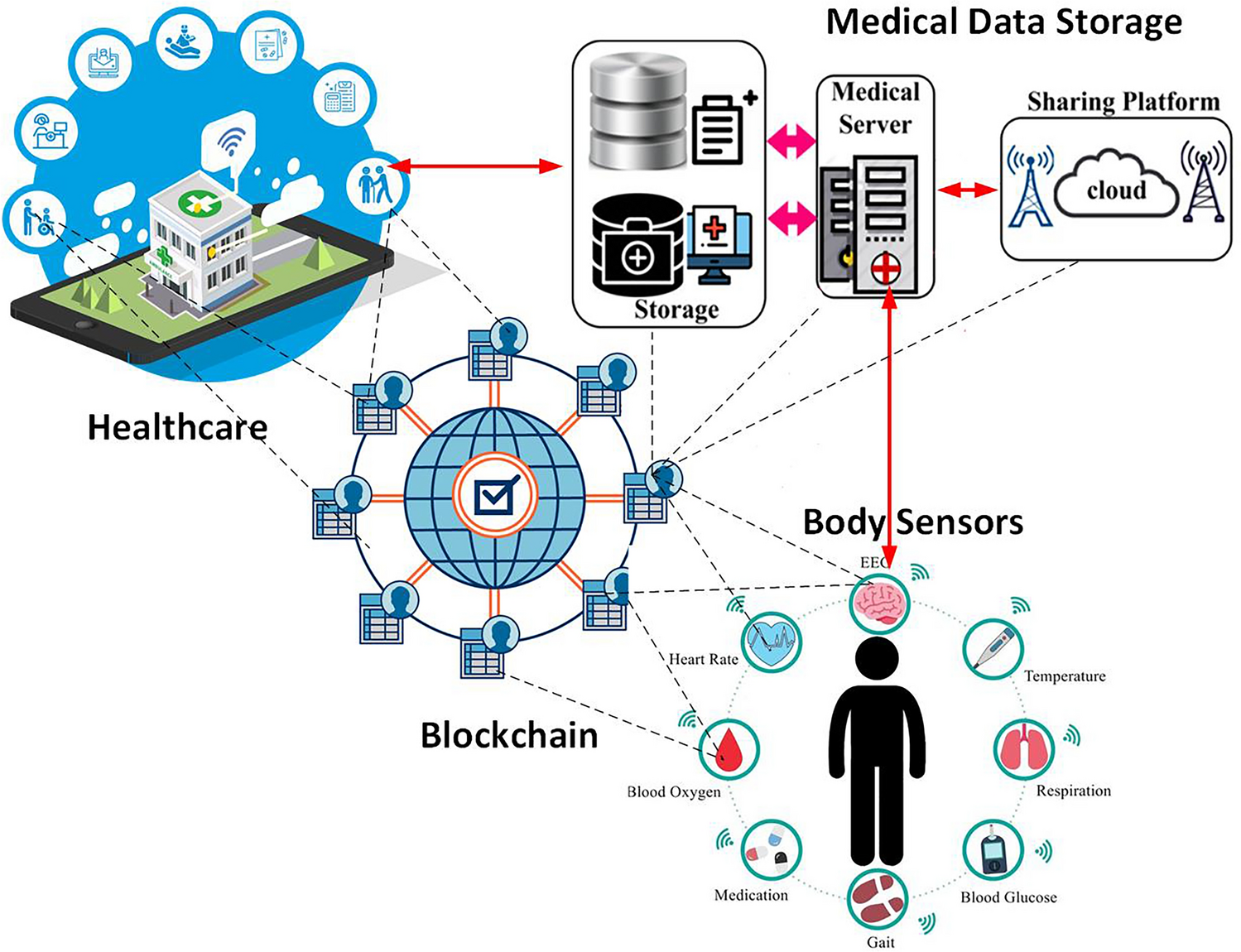

Evoked Potential System Architecture

This design implements the stimulator functionality using FPGA programming and analog interfaces.

In related products worldwide, some designs use many discrete components and incur higher cost; some use analog components to generate stimulus signals, limiting flexibility; others store video frames in FLASH, which limits storage. As FPGA devices evolve, they can host DSP soft cores and support C-language programming, enabling more flexible designs where a single FPGA can implement all required functions.

Hardware Design

The system produces auditory and visual stimuli at specified frequencies to induce evoked potentials. The device is programmable, allowing control commands to set different stimulus frequencies, durations, and modes, and to play user-supplied WAV audio files and display user-supplied BMP images. To ensure stable signal transmission between the FPGA, audio codec, and video output module, the multilayer PCB used in the prototype was fabricated by AIVON, whose controlled-impedance manufacturing capability helped maintain low noise performance required for electrophysiological stimulus generation.

The system consists of the following parts: development platform; pure tone (sine wave) and short-click audio output; recorded-audio input and output; and chessboard-reversal video output.

Development platform

The development platform is the ALTERA DE2 board, featuring a Cyclone II 2C35 F672C6 FPGA. The design uses the on-board FPGA, a 24-bit CD-quality audio codec WM8731 (MIC input, LINEIN, LINEOUT), a video decoder (NTSC/PAL support), and a VGA module with a high-speed DAC for video output.

FPGA devices offer high flexibility for electronic design and are expected to play a growing role in future development. An FPGA acts as a semi-custom circuit in the application-specific integrated circuit domain, addressing limitations of custom circuits while providing scalable programmable logic.

Audio input and output module

The design uses the WM8731 audio codec. The WM8731 is a low-power, high-performance 24-bit stereo audio codec featuring headphone drivers, configurable sample rates, selectable filters, on-chip ADCs, and an oversampled DAC for high-quality line and headphone outputs. It includes a crystal oscillator and configurable digital audio interfaces and provides a 2- or 3-wire control interface for configuration. The controller configures the WM8731 via the control interface and reads/writes audio data over the digital audio interface. On the DE2 board, LINEOUT is connected through a headphone amplifier and can drive headphones directly. LINEIN is coupled through DC-blocking capacitors, while MICIN can be used directly.

The design uses the WM831 audio codec to control output of pure tones and short clicks and to handle MIC audio input. After sampling, audio is output via the LINEOUT interface to headphones.

Audio sample values range from -2^31 to 2^31-1. A pure tone is a standard sine wave. One period of the sine wave is sampled at 48 points to form a sine table stored in the FPGA RAM. Values from the table are sent to the audio output at specified time intervals. Changing the interval controls the audio frequency. Each pure tone segment plays for about 10 seconds and is then stopped by a timer.

The short click is a square wave perceived as a "beep" sound. Like the pure tone, the click is generated by timer-driven interrupts that send samples to the audio output. The click has a cycle of about 2 seconds, with 1 second on and 1 second off, and plays for about 10 seconds before stopping.

Audio input can be recorded via the MIC input port for approximately 10 seconds. The audio input sampling rate is 48 kHz. After sampling, the recorded audio is output through the audio output port, similar to the pure tone and click playback processes.

Video output module

VGA (Video Graphics Array) is a standard interface for monitors. A standard VGA signal includes five lines: R, G, B color signals, HS horizontal sync, and VS vertical sync. In this design only luminance is required, so the G channel is used for the video signal. Horizontal sync (HS) and vertical sync (VS) are generated to meet VGA timing. These sync signals define the start and end of a line and a frame, ensuring image data is scanned left-to-right and top-to-bottom to form complete frames.

The video stimulus output is a chessboard pattern reversal. Test parameters: a 4×4 grid, alternating black and green squares. The reversal frequency is 1 Hz, and stimulus duration is 10 seconds.