Introduction

With the development of IoT technology, wearable products have become widespread. Wearable health monitors can measure multiple key physiological parameters at any time, alert when values are abnormal, and transmit monitoring data wirelessly to professional equipment or a personal mobile phone. Various wearable health monitors are already available on the market, including heart rate monitors, blood pressure monitors, body fat testers, and sleep trackers. This article describes the application of Cypress PSoC BLE in wearable heart rate monitors.

Heart Rate Monitoring Background

Heart rate is the number of heartbeats per unit time. It is an important parameter for assessing cardiac function and is also a useful indicator of physical and mental workload. Therefore, designing a wearable device that can continuously record, display, and store heart rate data, communicate with a mobile phone via Bluetooth, resist interference, and alert when heart rate falls outside normal ranges is necessary.

Design Challenges

Designing a heart rate monitor product typically faces the following issues:

- Need for low-energy Bluetooth communication to exchange information with a mobile phone, provide timely feedback to the user, and allow configuration via the phone.

- Requirement for an analog front end (AFE) and filtering circuitry to measure the heart rate signal. ADC sampling accuracy has a significant impact on the accuracy of heart rate measurements.

- Need to provide user input interfaces, such as capacitive touch buttons or sliders.

- Need to drive a segmented LCD display to show measured heart rate values.

- Requirement for low-power operation to extend standby time so the product can be powered by a coin cell battery.

PSoC BLE Single-Chip Solution

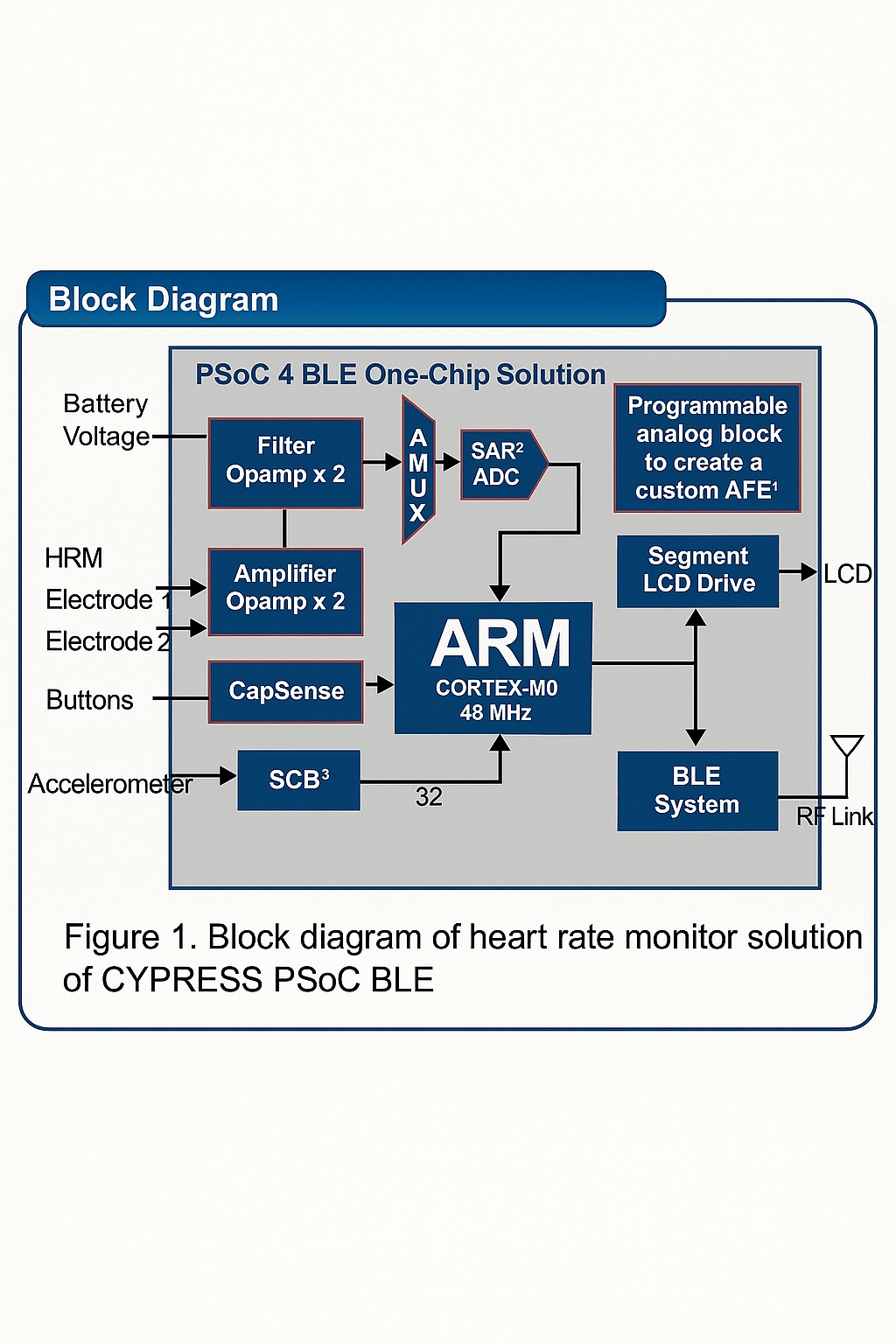

Cypress PSoC BLE series addresses the above requirements with a single-chip BLE solution and provides a standard heart rate profile example for developers. PSoC 4 is a scalable and reconfigurable platform based on an ARM Cortex-M0 CPU. It combines programmable, reconfigurable analog and digital blocks with flexible routing resources. PSoC BLE integrates a low-power Bluetooth microcontroller, radio subsystem, digital programmable logic, high-performance ADC, programmable op-amps in comparator mode, and standard communication and timing peripherals.

The PSoC BLE family includes programmable op-amps and a SAR ADC suitable for detecting and filtering heart rate signals. It integrates CapSense for capacitive touch buttons, sliders, and touchpads, and an LCD segment driver for displaying heart rate values. For low-power applications, it provides five configurable low-power modes to extend standby time. The on-chip BALUN simplifies antenna design. The graphical PSoC Creator development environment offers a visual interface for faster development and shorter time to market.

Block Diagram

The block diagram of the PSoC BLE heart rate monitor solution is shown below.

Conclusion

The Cypress PSoC BLE series can provide a single-chip solution for heart rate monitors. Integrating the required analog front end, BLE radio, user interface, and display drivers on one chip can meet product requirements while reducing development cost and development time.