Overview

To learn an MCU, first study the chip architecture, for example whether the chip is a 32-bit RISC IC or uses a Harvard architecture. The STM32F4 family implements the ARMv7-ME architecture. It is a 32-bit processor with a Harvard structure, a three-stage pipeline, the Thumb-2 instruction set, extended DSP and SIMD instructions, single-cycle MAC, optional single-precision FPU, optional MPU, and optional debug trace interface. The core includes a configurable NVIC and a configurable WIC (wake-up interrupt controller).

AHB-Lite Bus Interfaces

The main system consists of a 32-bit multi-layer AHB bus matrix that implements interconnections among the following:

- Eight master buses:

- Cortex-M4F core: ICode bus (instruction fetch), DCode bus (data access), and System bus (core system bus)

- DMA1 memory bus

- DMA2 memory bus

- DMA2 peripheral bus

- Ethernet DMA bus

- USB OTG HS DMA bus

- Seven slave buses:

- Internal Flash ICode bus

- Internal Flash DCode bus

- Main internal SRAM1 (112 KB)

- Auxiliary internal SRAM2 (16 KB)

- Auxiliary internal SRAM3 (64 KB) (only for STM32F42xxx and STM32F43xxx devices)

- AHB1 peripherals (including AHB-APB bridge and APB peripherals)

- AHB2 peripherals

- FSMC

After each chip reset, clocks to all peripherals are disabled (except SRAM and Flash interface). Before using a peripheral, its clock must be enabled in the RCC_AHBxENR or RCC_APBxENR registers.

Note: Performing 16-bit or 8-bit accesses to APB registers is converted to a 32-bit access. The bus bridge replicates the 16-bit or 8-bit data into a 32-bit word.

Memory Organization

Program memory, data memory, registers, and I/O ports are arranged within a single 4 GB address space. Bytes are encoded in little-endian format: the lowest-numbered byte in a word is the least significant byte, and the highest-numbered byte is the most significant byte.

The addressable memory space is divided into eight main regions of 512 MB each.

Embedded SRAM

STM32F405xx/07xx and STM32F415xx/17xx devices provide 4 KB of backup SRAM and 192 KB of system SRAM.

System SRAM is accessible by byte, halfword (16-bit), or word (32-bit). Read and write operations occur at CPU speed with zero wait states. The system SRAM is divided into three blocks:

- A 112 KB block and a 16 KB block mapped at address 0x2000 0000, accessible by all AHB master buses.

- A 64 KB block mapped at address 0x1000 0000, accessible only by the CPU via the DCode bus.

Flash

The Flash interface manages CPU accesses to Flash through the AHB I-Code and D-Code buses. The interface supports erase and programming operations, implements read/write protection mechanisms, and accelerates code execution through instruction prefetch and cache mechanisms.

Main Flash features:

- For STM32F40x and STM32F41x, capacity up to 1 MB

- 128-bit wide data read

- Byte, halfword, word, and double word programming

- Sector erase and mass erase

Flash memory organization:

- Main memory block, divided into four 16 KB sectors, one 64 KB sector, and seven 128 KB sectors

- System memory, from which the device can boot in system memory bootstrap mode

- 512-byte OTP (one-time programmable) area for user data

The OTP area also contains 16 additional bytes used to lock the corresponding OTP data blocks.

Option bytes are used to configure read/write protection, BOR level, software/hardware watchdog, and device reset behavior in standby or stop modes.

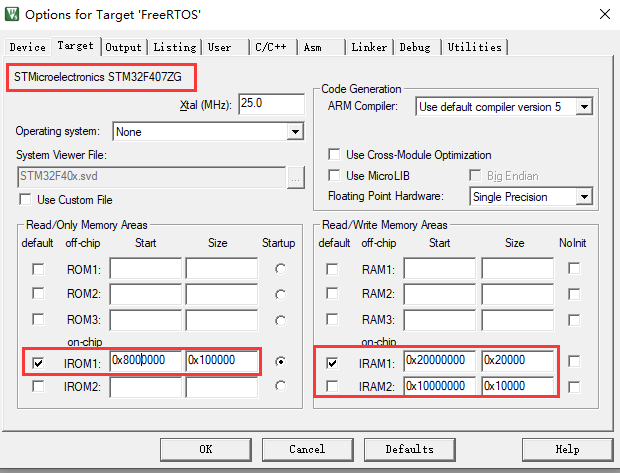

Compared with a typical project file, the default configuration for SRAM and ROM is shown below:

This indicates that the STM32F407 series typically uses four 16 KB Flash sectors, and SRAM uses 112 KB and 16 KB blocks. The 64 KB region mapped at 0x1000 0000 can be enabled, but that region is accessible only by the CPU via data access.

Bit-Banding

The Cortex-M4F memory map includes two bit-band regions. These regions map each word in the bit-band alias region to the corresponding bit in the bit-band region. Writing a word in the alias region performs a read-modify-write operation on the target bit in the bit-band region.

In STM32F4 devices, peripheral registers and SRAM are mapped into a bit-band region, enabling single-bit read/write operations. These operations apply only to Cortex-M4F accesses; they are not valid for other bus masters such as DMA.

The mapping between an alias word and a bit-band bit is given by the formula:

bit_word_addr = bit_band_base + (byte_offset * 32) + (bit_number * 4)

where:

- bit_word_addr is the address in the alias region that maps to the target bit

- bit_band_base is the start address of the alias region

- byte_offset is the byte offset of the target bit within the bit-band region

- bit_number is the bit position within the byte (0-7)

Example:

To map bit 2 of the byte at SRAM address 0x2000 0300 to the alias region:

0x22006008 = 0x22000000 + (0x300 * 32) + (2 * 4)

Writing to address 0x22006008 performs a read-modify-write on bit 2 of the byte at SRAM address 0x2000 0300. Reading from address 0x22006008 returns the bit value of that bit (0x01 for bit set, 0x00 for bit reset).

Bootstrap Configuration

The memory map is fixed: code starts at 0x0000 0000 (accessed through the ICode/DCode buses) and data starts at 0x2000 0000 (accessed via the system bus). The Cortex-M4F CPU always fetches the reset vector through the ICode bus, which means only the code region (typically Flash) can provide the initial bootstrap space. STM32F4 devices implement a mechanism to bootstrap from other memories such as internal SRAM.

In STM32F4 devices, three bootstrap modes can be selected via the BOOT[1:0] pins.

Typically, BOOT0 is pulled low on boards. During development, BOOT0 and BOOT1 can be driven to select boot from alternate memory, which can reduce Flash erase cycles and extend Flash endurance.

When booting from SRAM, application initialization must relocate the NVIC exception and interrupt vector table to the vector table and offset registers in SRAM.

After reset, the values on the BOOT pins are sampled on the fourth rising edge of SYSCLK. Users can select the desired bootstrap mode using BOOT1 and BOOT0 after reset. BOOT0 is a dedicated pin; BOOT1 is shared with a GPIO pin. Once BOOT1 is sampled, the corresponding GPIO pin becomes available for other uses.

BOOT pin values are also re-sampled when the device exits standby mode. Therefore, these pins must retain the required bootstrap configuration while the device is in standby. After the bootstrap sampling and any start-up delay, the CPU loads the stack pointer from address 0x0000 0000 and begins executing code at 0x0000 0004.

Embedded Bootloader

The embedded bootloader mode is used to reprogram Flash via the following serial interfaces:

- USART1 (PA9/PA10)

- USART3 (PB10/11 and PC10/11)

- CAN2 (PB5/13)

- USB OTG FS (PA11/12) in device mode (DFU: Device Firmware Upgrade)

USART peripherals run from the internal 16 MHz HSI oscillator, while CAN and USB OTG FS require an external clock (HSE) with a frequency multiple of 1 MHz (typically 4 MHz to 26 MHz).

The embedded bootloader code resides in the system memory and is programmed during device manufacture.