DRAM types

DRAM modules are available in several types:

- SDRAM (Synchronous Dynamic Random Access Memory): an early, widely used DRAM type. It is synchronized with the system clock and supports faster data transfers compared with asynchronous DRAM.

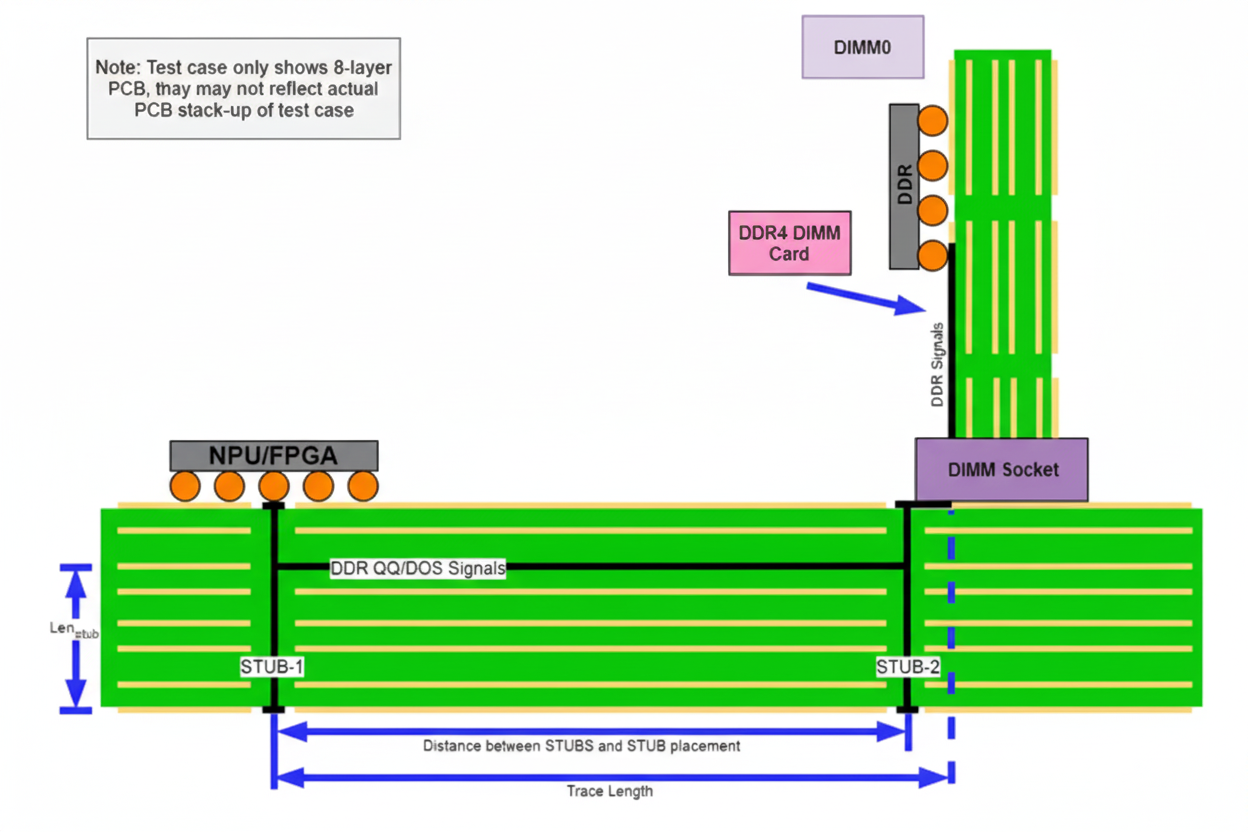

- DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory): an improved version of SDRAM. DDR transfers data on both the rising and falling edges of the clock, effectively doubling the data rate per clock cycle.

- DDR2 SDRAM: a successor to DDR SDRAM that offers higher data transfer rates and lower power consumption through improved circuit design and higher clock frequencies.

- DDR3 SDRAM: the successor to DDR2, providing higher bandwidth, higher clock frequencies, and lower operating voltages.

- DDR4 SDRAM: a later generation offering greater data transfer bandwidth, higher densities, higher clock frequencies, and lower power per bit, commonly used in higher-performance and server applications.

These DRAM types differ in transfer speed, bandwidth, power consumption, and compatibility, and they have evolved toward higher performance and lower power consumption.

DRAM storage cell

A DRAM storage cell is formed by a capacitor and an access transistor. Each memory cell contains a capacitor that stores charge representing a bit and a transistor that controls read and write access. The presence of charge on the capacitor represents a logical 1; the absence of charge represents a logical 0. Because the capacitor leaks charge over time, the stored data must be periodically refreshed, which is why this memory is called dynamic RAM.

How DRAM stores data

DRAM stores data by accumulating and discharging charge on the capacitor in each cell. During a write operation, the access transistor is activated to place charge on the capacitor corresponding to a 0 or 1. During a read operation, the transistor connects the capacitor to the sense amplifier so the stored charge can be detected.

Because capacitors leak charge, DRAM requires periodic refresh cycles to restore the charge levels and preserve data integrity. A DRAM chip is organized as a grid of rows and columns; refresh typically proceeds by activating rows and reading and rewriting their contents.

Compared with other memories such as SRAM, DRAM has slower access times due to leakage and the need for refresh, but it offers advantages in density and power-per-bit, which is why it is widely used as main system memory.