Summary

InP meets 6G requirements. Heterogeneous integration is essential to mature InP and combine all components into a complete system.

Future generations of mobile communication

Each decade brings a new mobile generation. User numbers and per-user wireless data consumption have grown dramatically. Initially, messaging was the primary use case; today we are in the 5th generation (5G) with more than a billion human and machine-to-machine connections and peak data rates around 10 Gbit/s. 5G is also an inflection point because, in addition to more connections and higher speeds, it must support new use cases such as autonomous driving and holographic presence. This trend continues toward 6G, expected around 2030, with projected peak data rates beyond 100 Gbit/s, extreme coverage, and ubiquitous connectivity, according to Michael Peeters, imec VP of connectivity R&D.

InP delivers power and efficiency at high frequencies

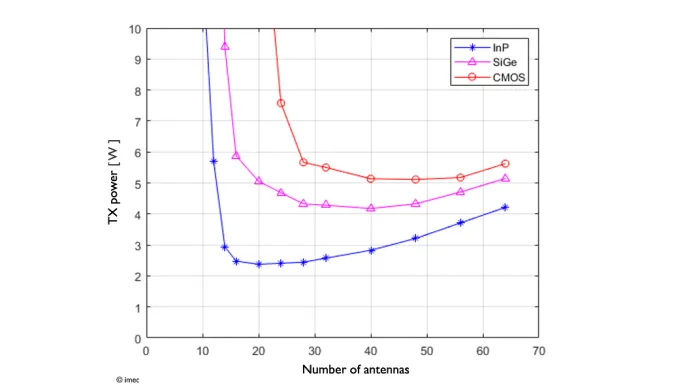

To reach very high data rates, the telecom industry is moving to higher frequencies. The 6G vision targets frequencies above 100 GHz, starting with the D-band near 140 GHz. Michael Peeters explains that the main challenge above 100 GHz is generating sufficient power with acceptable efficiency. For CMOS and SiGe amplifiers, saturated output power in the D-band is typically below 15 dBm, and efficiency is often under 10%. That is low because popular modulation schemes such as 64-QAM require operation several dB below saturation. Efficiency also degrades faster than linearly as output power decreases. Indium phosphide (InP) outperforms in this frequency range, offering output power above 20 dBm and efficiencies in the 20% to 30% range. InP can provide the required performance at these high frequencies, particularly when area is constrained and only a limited number of antennas can be accommodated. InP can cut power consumption in half while halving footprint compared with alternatives.

InP uses half the power and half the area. From Claude Desset et al., GlobeCom workshop 2021.

Maturing InP technology

Creating transistors capable of high-frequency operation, such as InP HBTs (heterojunction bipolar transistors), requires both a mature, cost-effective InP technology and a method to integrate InP-based components with silicon-based components into a complete system. For both challenges, heterogeneous integration of III-V materials like InP with CMOS is key. Calibration, control, beamforming, and converters still require CMOS.

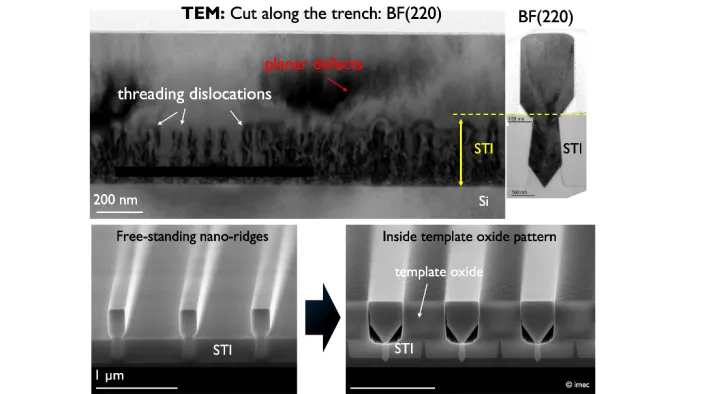

Today, InP technology relies on small substrate wafers (<6 inches), lab-style processes such as electron-beam lithography, and gold-based contacts that are incompatible with CMOS. The fragility of InP is a prominent challenge. imec is exploring techniques to transfer III-V materials to more economical, robust substrates such as silicon. Because of large lattice mismatch, directly growing InP on silicon typically introduces defects, mainly threading dislocations and planar defects. These defects cause leakage currents that significantly degrade device performance or cause reliability issues because traps can capture and release carriers at high RF frequencies.

Nanoridge engineering captures defects in InP grown on silicon

To address defects arising from direct growth of InP on silicon, imec proposed a technique called nanoridge engineering. The approach relies on selective growth of III-V materials in pre-patterned structures or trenches in silicon. These high aspect-ratio trenches effectively trap defects at the narrow bottom and allow high-quality, low-defect-rate material to grow above the trench. The overgrown nanoridges broaden at the top and form a solid foundation for device stacks. By reducing spacing between nanoridges, they can merge to form a local III-V material plate.

“Recently, imec demonstrated InGaAs box-shaped nanoridges that effectively trap threading dislocations in the trench. Nanoridges were successfully grown both independently and as guided templates. We are now combining InGaAs nanoridge engineering with insights from earlier InGaP/GaAs nanoridge HBT demonstrations to develop heterostructure stacks required for 140 GHz applications. To address the speed, efficiency, and output power challenges of next-generation wireless high-data-rate systems, we envision using InP HBTs on a 300 mm silicon wafer platform,” said Nadine Collaert, imec senior project leader for RF projects.

InGaAs nanoridge engineering.

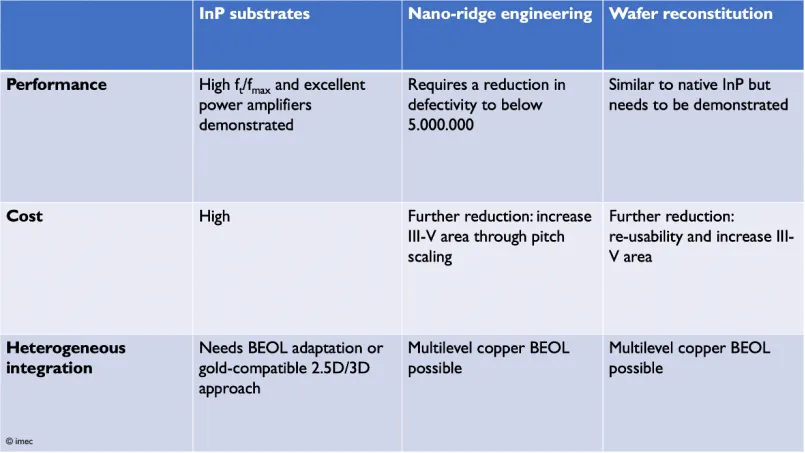

Besides direct growth methods such as nanoridge engineering, InP can be integrated onto silicon via wafer reconstitution approaches that still use small high-quality InP substrates as starting material. In such processes, high-quality InP substrates are diced into unpatterned tiles. These tiles are then attached to silicon wafers, planarized, and processed in a fab. Direct growth and wafer reconstitution options each have trade-offs in performance, cost, and heterogeneous integration potential.

Advanced comparison of integrating InP on silicon versus native InP substrates.

System-level co-integration approaches

Maturing cost-effective InP technology via direct growth or wafer reconstitution is only part of the challenge. Resulting components must be integrated into a complete system that combines III-V and CMOS building blocks, such as InP HBTs for power amplifiers and CMOS for beamforming transceivers. This need introduces a range of integration challenges. imec investigates monolithic (2D) integration of III-V devices with silicon devices on the same plane, as well as 2.5D and 3D integration technologies to achieve heterogeneous integration.

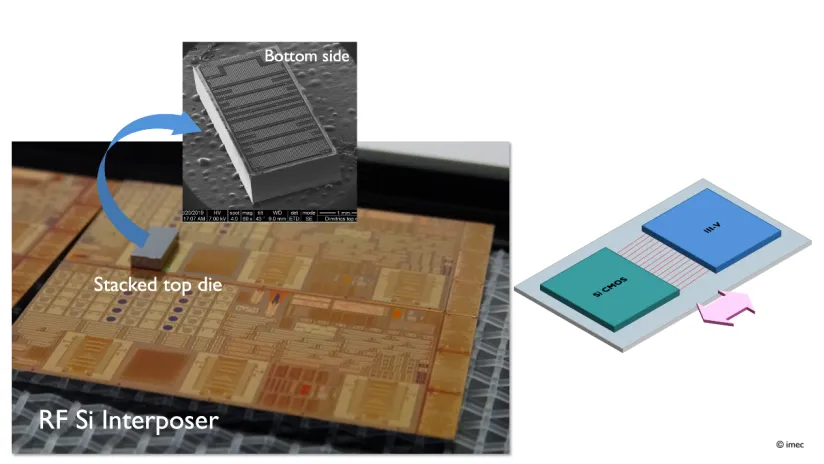

Printed circuit boards remain state-of-the-art for many applications and are being optimized for higher frequencies through reduced spacing, material selection, and layout improvements. 2.5D integration uses a silicon interposer (a chip or layer with lithographically defined connections, potentially including through-silicon vias) to communicate between III-V and silicon dies. “This technology has been optimized for high-speed digital applications but requires further work for RF use cases. Specifically, we are evaluating different dielectric materials and metal thicknesses to achieve low-loss interconnects. We need high-resistivity silicon substrates or thick dielectric layers to isolate metal layers from lossy substrates, and we also need very thick redistribution layers (RDLs) and additional metal layers to reduce metal loss. We will also consider integration of high-quality passive components in some cases,” Nadine Collaert explained.

Top view: RF interposer with Si stack and top mold, X. Sun et al., ECTC 2022.

2.5D and 3D technologies as enablers for heterogeneous integration

Why pursue 3D integration? Nadine Collaert: “As frequency increases, wavelength decreases and antenna array area scales down accordingly. However, above 100 GHz, antenna pitch becomes smaller than front-end circuit pitch, and it is hard to further reduce the area of millimeter-wave radio chips. The antenna array area sets constraints, and to accommodate everything under the antenna we need to explore advanced heterogeneous integration in the third dimension.”

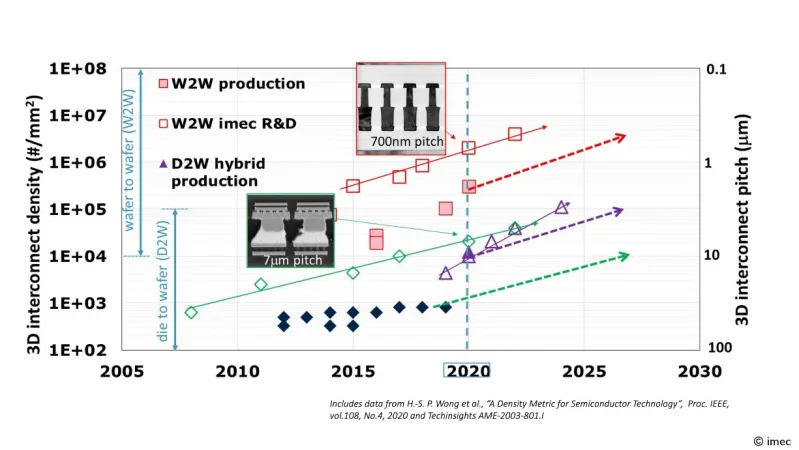

Over the past decade, there has been major progress in 3D interconnects. For wafer-scale options (wafer-to-wafer, die-to-wafer), efforts focus on reducing interconnect pitch. With wafer-to-wafer bonding or hybrid bonding, pitches below 1 μm are achievable and can be pushed toward 500 nm or below. The trend toward smaller pitch also applies to die-to-wafer bonding and die stacking using microbumps.

Roadmap for 3D interconnect technology. From Eric Beyne's ISSCC 2021 talk, “3D system integration: Technology outlook and long-term roadmap.”

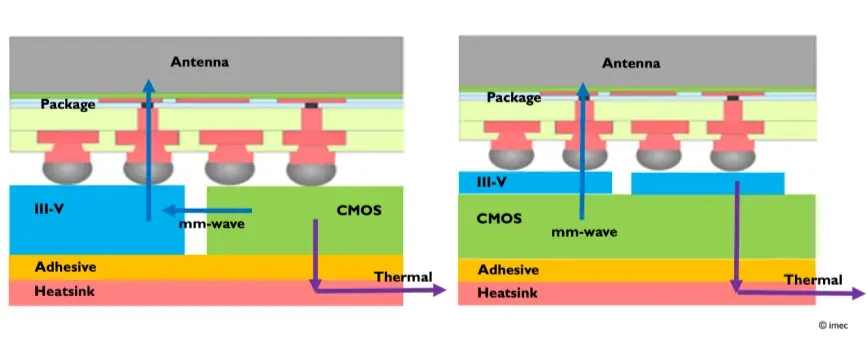

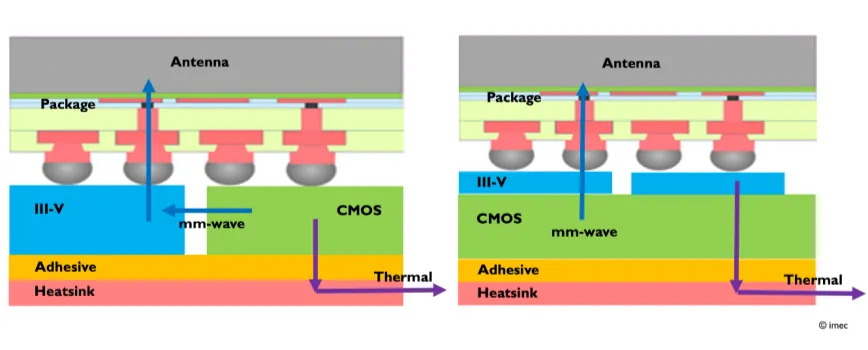

For >100 GHz applications, the two integration approaches share common challenges. Both rely on fine via or microbump pitches below 100 μm. Both must accommodate a large number of connections for routing RF, DC, IF, and digital signals. Trace and spatial dimensions need to be far smaller than 50 μm, preferably in the 5–10 μm range. Differences exist: in 2/2.5D integration, III-V dies are placed next to CMOS chips, improving thermal management because both dies can contact a heatsink directly. The downside is that some applications may require relaxing area constraints in one dimension, and this architecture only enables 1D beam control. In contrast, 3D integration allows all chips and circuits to be placed underneath the antenna and enables 2D beam control, steering signals over a hemisphere. 2D beam control is necessary for 5G and beyond to minimize penetration loss and extend coverage at the required high frequencies. Thermal management is more challenging in 3D. 3D integration is also more complex and introduces unique processing challenges.

(Left) 2/2.5D integration uses a silicon interposer to connect III-V and silicon chips. (Right) 3D integration stacks III-V chips on silicon and connects them to antennas; in this case antennas are also integrated in the silicon interposer.

System technology co-optimization leads the way

The choice of integration and packaging ultimately depends on the use case or application. “Because there are many options, imec launched a systems technology co-optimization (STCO) program to guide technology choices even at the system level. The STCO approach takes inputs from architecture and application constraints while considering signal loss, bandwidth, thermal dissipation, mechanical stability, and cost. We must trade off all these parameters to design and manufacture sixth-generation devices,” Michael Peeters concluded.