Introduction

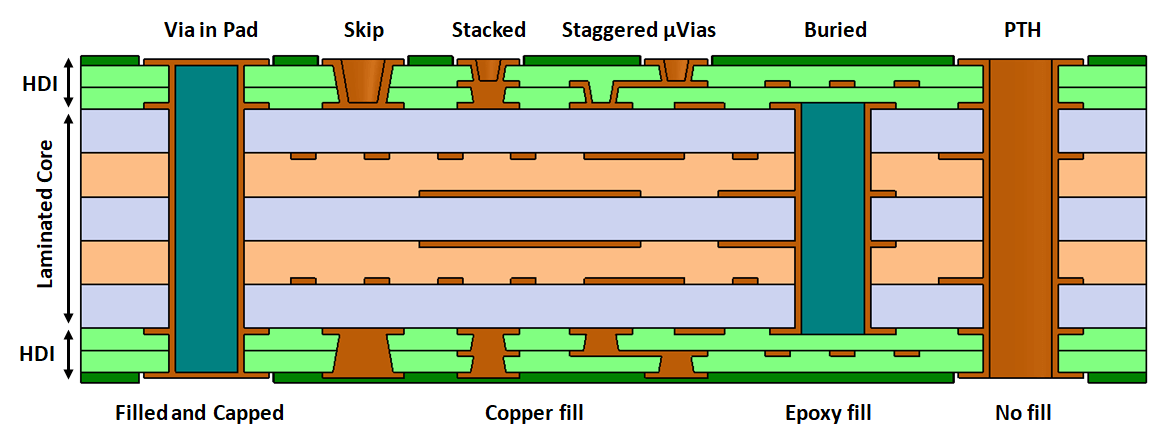

Blind vias play a crucial role in modern printed circuit board (PCB) designs, particularly in high-density interconnect (HDI) applications where space constraints demand efficient layer connectivity. These vias connect an outer layer to one or more inner layers without penetrating the entire board thickness, enabling denser routing and improved signal integrity. Proper layout and rigorous testing are essential to mitigate manufacturing challenges such as drilling accuracy and plating uniformity. In PCB quality control, blind via inspection ensures structural integrity and electrical performance under operational stresses. This article explores blind via layout principles and testing methods, drawing from factory-driven practices to enhance PCB reliability testing. Electric engineers benefit from these insights to optimize designs for production scalability.

What Are Blind Vias and Why Do They Matter

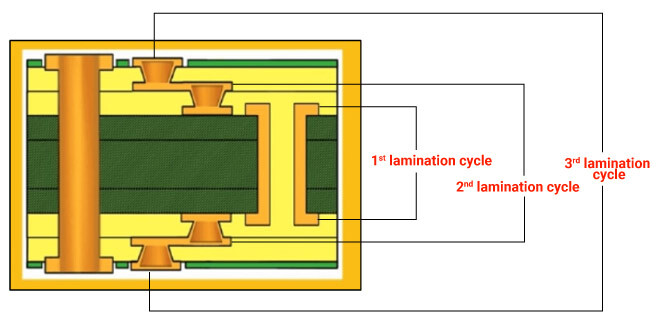

Blind vias differ from through-hole vias by terminating at an inner layer, which conserves surface real estate for components and traces. They are fabricated using sequential lamination processes, where specific layers are drilled and plated before stacking additional cores. This approach supports advanced multilayer boards used in telecommunications, computing, and automotive electronics. However, their partial depth introduces complexities in depth control and void formation during plating. Effective blind via testing methods verify connectivity and detect defects early in manufacturing testing. Ultimately, mastering blind via layout directly impacts PCB reliability testing outcomes, reducing field failures in high-stakes applications.

The relevance of blind vias grows with shrinking component pitches and faster signal speeds. Factory experience shows that poor layout can lead to higher scrap rates due to misalignment or inadequate annular rings. Standards like IPC-6012E outline qualification criteria for such structures, emphasizing performance under thermal and mechanical loads. Engineers must balance density gains against reliability risks, such as electromigration in high-current paths. PCB quality control protocols integrate blind via inspection to maintain class 3 compliance for critical systems. Prioritizing these elements ensures boards meet end-user expectations for longevity.

Related Reading: Unlocking PCB Density: A Beginner's Guide to Blind Vias

Technical Principles of Blind Via Layout

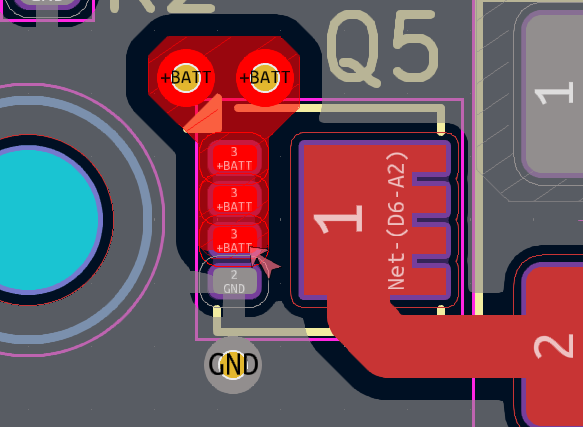

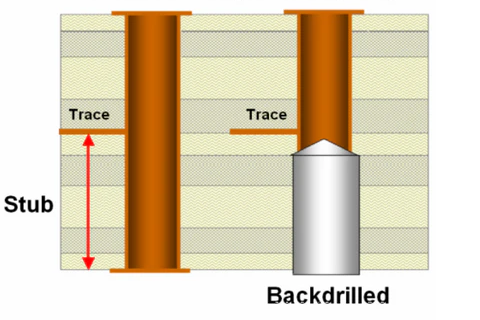

Blind via layout begins with precise drill depth control, achieved through mechanical, laser, or controlled depth drilling techniques tailored to board thickness. Laser ablation excels for microvias under 150 micrometers, offering superior accuracy in resin dielectrics while minimizing heat-affected zones. Placement strategies avoid stacking vias in adjacent layers to prevent drill breakout and ensure plating uniformity. Aspect ratios, defined as via depth to diameter, influence reliability; tighter ratios reduce plating voids but demand advanced process controls. Factory alignment uses fiducials and panel-level registration to position vias relative to traces and pads.

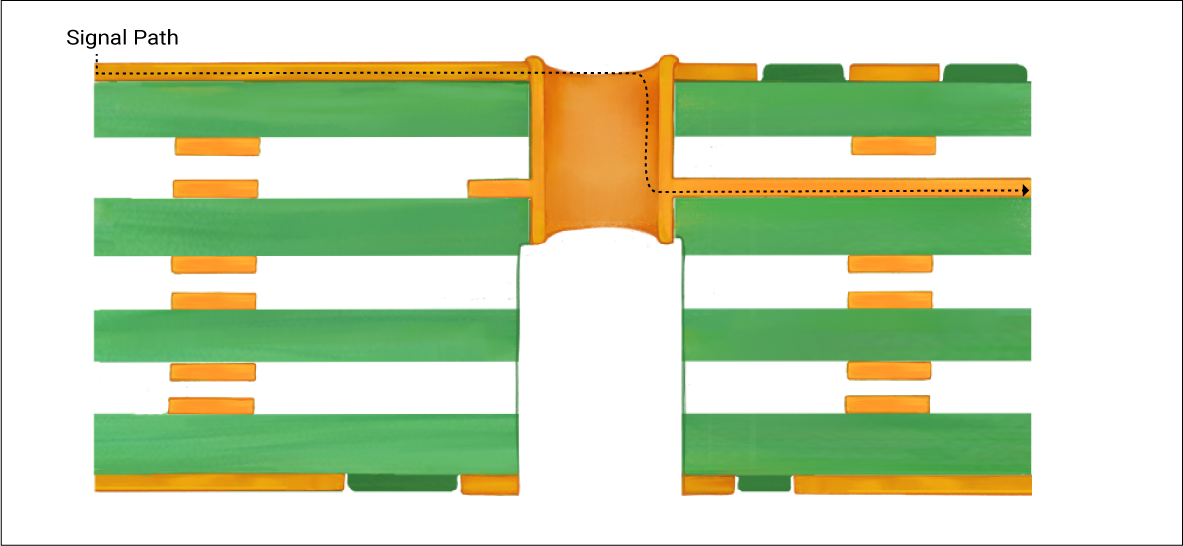

Annular ring dimensions provide mechanical support and prevent cracking during lamination pressure. IPC guidelines recommend pad diameters exceeding the finished via by specific margins to accommodate plating buildup. Signal integrity considerations include via stub minimization, as blind vias inherently shorten stubs compared to through vias. Thermal expansion mismatches between copper and dielectric materials stress via barrels, necessitating layout buffers near bend areas. These principles guide engineers in creating robust designs that withstand fabrication variances.

In multilayer stacks, blind via sequencing follows build-up sequences, where core 1-2 vias differ from core 2-3. This staggered approach optimizes yield by isolating process windows per stack-up. Electrical modeling simulates impedance discontinuities at via transitions. Layout tools enforce design rules for clearance to adjacent features, preventing shorts post-plating.

Manufacturing Challenges in Blind Via Production

Fabrication of blind vias involves sequential processes that amplify defect risks compared to standard through vias. Drilling from one side requires exact depth targeting, often verified by pilot holes or etch-back methods. Electroless copper seeding followed by electrolytic plating fills the barrel, but air entrapment can cause voids detectable only post-lamination. Solder mask application over blind via openings protects against contamination while allowing inspection access. Factory data highlights via bottom roughness as a common issue affecting adhesion.

Lamination cycles apply heat and pressure, potentially causing via barrel cracks if resin flow is uneven. Post-lamination planarization ensures flatness for subsequent imaging. These steps demand tight process controls to align with IPC-A-600K acceptability criteria for class 2 and 3 boards.

Blind Via Testing Methods for Quality Assurance

Blind via testing methods encompass visual, electrical, and advanced imaging techniques integrated into PCB quality control workflows. Automated optical inspection (AOI) scans surface openings for size, alignment, and plating coverage, flagging anomalies like under-etch or bridging. X-ray inspection reveals internal barrel quality, detecting voids, cracks, or misalignment invisible from the top. Electrical continuity tests use flying probes to measure resistance across nets, identifying opens or high-resistance paths early.

For deeper analysis, time-domain reflectometry (TDR) assesses impedance profiles and stub lengths in high-speed designs. Cross-sectioning provides destructive verification, polishing samples to inspect plating thickness and interface integrity. These manufacturing testing approaches scale from coupon samples to full panels.

Reliability-focused PCB reliability testing subjects via chains to thermal cycling, monitoring resistance changes per IPC-TM-650 methods. A rise exceeding defined thresholds indicates fatigue failure. Vibration and shock tests simulate end-use conditions, ensuring via robustness.

- AOI: Purpose — Surface defect detection; Strengths — High speed, non-contact; Limitations — Surface only.

- X-ray: Purpose — Internal structure; Strengths — Non-destructive, volumetric; Limitations — Lower resolution for fine features.

- Electrical Continuity: Purpose — Functionality check; Strengths — Net-level verification; Limitations — Misses latent defects.

- TDR: Purpose — Signal integrity; Strengths — Quantitative impedance data; Limitations — Requires access nets.

- Cross-Section: Purpose — Microstructure analysis; Strengths — Detailed plating inspection; Limitations — Destructive, sample-based.

Related Reading: Blind Vias in PCB Design: Optimizing High-Density Boards

Best Practices for Blind Via Layout and Inspection

Optimize blind via layout by distributing them evenly across the panel to minimize warpage during lamination. Use teardrop entries for trace-to-via transitions to reduce stress concentrations. Specify via fill options like conductive epoxy for high-reliability applications, enhancing thermal dissipation. Maintain dielectric thickness consistency to control capacitance. Factory best practices include design-for-manufacturability (DFM) reviews, simulating stack-up interactions.

In blind via inspection, combine inline AOI with 100% electrical test for class 3 boards. Implement statistical process control (SPC) on drill depth and plating thickness. For HDI, validate via chains on qualification vehicles before production runs. These steps align with J-STD-001 requirements for soldered assemblies.

Troubleshoot common failures like bottom cratering by adjusting desmear processes. Empty caves in filled vias stem from gas entrapment; vacuum-assisted plating mitigates this. Thermal cycle failures often trace to aspect ratio exceedance, prompting redesigns.

Ensuring Long-Term PCB Reliability Through Testing

PCB reliability testing extends beyond initial fabrication to accelerated life tests mimicking operational environments. Blind vias face electromigration and intermetallic growth under current and temperature stresses. Highly accelerated test methods (HATS) accelerate failure modes for prediction. Data logging during tests correlates layout parameters to mean time between failures (MTBF).

Integration with overall PCB quality control loops back learnings to design rules. Engineers refine via diameters and materials based on test cohorts. This iterative approach sustains high yields in volume manufacturing.

Conclusion

Blind via layout demands precision in placement, sizing, and sequencing to support dense, high-performance PCBs. Comprehensive blind via testing methods, from AOI to reliability cycling, safeguard against defects and ensure compliance with industry benchmarks. Factory-driven insights emphasize process integration for consistent outcomes. Electric engineers applying these practices achieve superior PCB quality control and manufacturing testing efficiency. Prioritizing blind via inspection ultimately delivers reliable boards ready for demanding applications.

FAQs

Q1: What are the primary blind via testing methods used in PCB quality control?

A1: Blind via testing methods include AOI for surface checks, X-ray for internal voids, and electrical continuity for functionality. TDR verifies signal integrity in high-speed nets. Cross-section analysis confirms plating quality destructively. These align with factory protocols to catch defects early, enhancing overall reliability.

Q2: How does blind via layout impact PCB reliability testing results?

A2: Optimal blind via layout minimizes stubs and stresses, improving thermal cycling performance. Even distribution prevents warpage, while adequate annular rings resist cracking. Poor layout increases failure rates in accelerated tests. Engineers use simulations to predict outcomes before fabrication.

Q3: Why is X-ray inspection critical for blind via inspection during manufacturing testing?

A3: X-ray reveals subsurface issues like barrel cracks or plating discontinuities invisible to optical methods. It supports non-destructive verification of depth control and fill quality. This technique integrates into inline PCB quality control, reducing escapes to assembly.

Q4: What role do industry standards play in blind via reliability testing?

A4: Standards like IPC-6012E define qualification tests for via performance under stress. They specify acceptance criteria for resistance changes and visual defects. Compliance ensures consistency across manufacturers, bolstering PCB reliability testing confidence.

References

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC, 2017

IPC-A-600K — Acceptability of Printed Boards. IPC, 2020

IPC-4761 — Design Guide for Protection of Printed Board Via Structures. IPC, 2020