What is an Asynchronous FIFO and Why is it Essential?

In the realm of digital integrated circuit (IC) design, particularly in large-scale ASICs and FPGAs, systems often operate with multiple independent clock domains. This multi-clock environment presents significant challenges for reliably transferring data between different sections of the circuit. An asynchronous FIFO (First-In, First-Out) serves as a critical solution, acting as a buffer or a temporary data reservoir. It effectively decouples data rates between upstream and downstream components and, more importantly, facilitates the safe and stable transfer of data across these distinct clock domains.

An asynchronous FIFO is designed to store data written under the control of one clock and then allow that data to be read out under the control of a completely different, asynchronous clock. This capability is vital because if not managed carefully, read and write operations from different clock domains could overlap unpredictably, leading to data corruption, loss, or system instability. To prevent such issues, asynchronous FIFOs incorporate sophisticated mechanisms to synchronize read and write pointers, along with status flags, ensuring that data is neither overwritten before being read nor read multiple times. Furthermore, when detecting status conditions like "full" or "empty" across clock boundaries, a pessimistic approach is adopted to account for the inherent uncertainties of cross-domain pointer values.

How Do Asynchronous FIFOs Operate?

The fundamental operations of an asynchronous FIFO revolve around writing data into its memory and reading data out, governed by distinct control signals and clocks. These operations are managed by internal pointers and status flags that prevent common data integrity issues.

Understanding the Write Operation

To write data into an asynchronous FIFO, the data to be stored is presented at the FIFO’s input. Simultaneously, a "write enable" signal is asserted. The FIFO then captures and stores this data on the next rising edge of its dedicated write clock. This process continues until a predefined stop condition is met, most commonly when the FIFO signals that it is full.

Understanding the Read Operation

Conversely, reading data from an asynchronous FIFO involves asserting a "read enable" signal. The FIFO then outputs the next available data item, which is typically sampled on the next rising edge of its dedicated read clock. This operation continues until the FIFO indicates that it has no more data available, typically by asserting an "empty" flag.

Pointers and Status Flags

The internal logic of an asynchronous FIFO relies on two primary pointers: a write pointer, which tracks the next available memory location for data to be written, and a read pointer, which points to the next memory location from which data will be read. Additionally, two crucial status flags are provided to regulate operations: an empty flag, which prevents read requests when the FIFO contains no data, and a full flag, which prevents write requests when the FIFO has reached its storage capacity.

Why is Gray Code Essential for Pointer Synchronization in FIFOs?

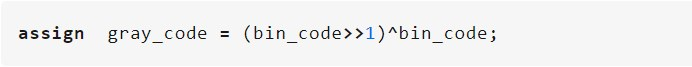

Synchronizing multi-bit counter values, such as binary read and write pointers, directly across asynchronous clock domains presents a significant challenge due to the risk of metastability. When a binary counter increments (e.g., from 7 (0111) to 8 (1000)), multiple bits can change state simultaneously. If sampled by another clock domain during this transition, the receiving domain might capture an inconsistent, intermediate value, leading to ambiguity or incorrect pointer interpretation.

Gray code offers an elegant solution to this problem. The defining characteristic of Gray code is that only a single bit changes between any two consecutive values. This property dramatically reduces the ambiguity when a multi-bit pointer value is sampled in a different clock domain. Even if metastability occurs on the single changing bit, the resulting sampled value will be either the old or the new valid Gray code, never an erroneous intermediate value.

Therefore, a standard practice in asynchronous FIFO design involves converting the binary read and write pointers into their respective Gray code equivalents. These Gray-coded pointers are then synchronized across the clock domains using robust synchronization techniques, typically a two-stage flip-flop synchronizer, which significantly mitigates the risk of metastability. The synchronized Gray-coded pointers are then used for crucial full/empty detection logic.

Gray Code for Full and Empty Detection

While Gray code resolves the simultaneous-bit-change issue, its non-sequential nature requires specific rules for detecting full and empty conditions. The process involves comparing synchronized Gray-coded pointers.