Introduction

Polytetrafluoroethylene (PTFE) printed circuit boards excel in high-frequency applications due to their low dielectric constant and minimal dissipation factor. Engineers designing for RF, microwave, and high-speed digital systems rely on PTFE PCBs to maintain signal fidelity over long traces and at elevated frequencies. Signal integrity challenges such as PTFE PCB signal loss, PTFE PCB impedance matching, and PTFE PCB crosstalk become pronounced as data rates exceed 10 Gbps or frequencies surpass 5 GHz. These issues can degrade performance, leading to bit errors, increased jitter, and reduced eye opening in receivers. Addressing them requires a deep understanding of material properties, layout techniques, and fabrication processes. This article explores these considerations, offering factory-driven insights aligned with industry standards to optimize PTFE PCB designs.

Understanding PTFE PCBs and the Importance of Signal Integrity

PTFE, known for its chemical inertness and thermal stability, serves as the core dielectric in specialized laminates for demanding environments. Unlike standard FR-4, PTFE maintains a stable dielectric constant around 2.1 to 2.5 across a broad frequency range, reducing phase distortion. Its exceptionally low loss tangent, typically below 0.0005 at microwave frequencies, directly combats PTFE PCB signal loss by minimizing energy dissipation in the dielectric. Signal integrity refers to preserving the electrical quality of signals from transmitter to receiver, encompassing amplitude, rise time, and timing accuracy. In high-speed systems, poor signal integrity manifests as overshoot, ringing, or inter-symbol interference, compromising overall system reliability. For electric engineers, mastering these aspects ensures compliance with performance specs in telecommunications, radar, and satellite applications.

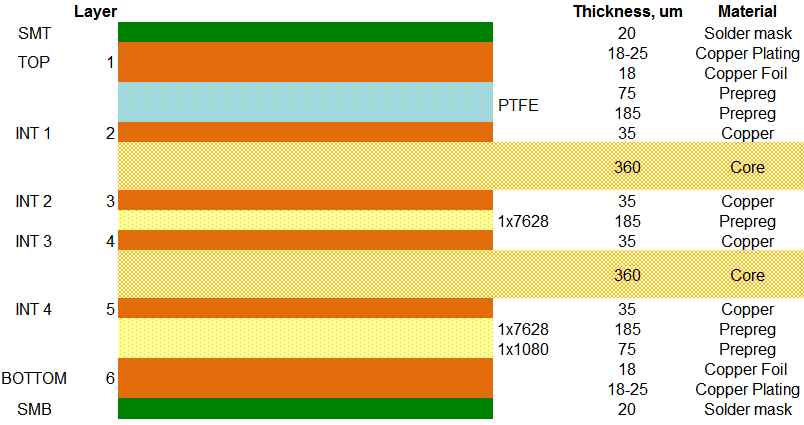

Factory processes for PTFE PCBs demand precision, including specialized etching and lamination to avoid voids that could exacerbate crosstalk. Adherence to IPC-4101 for base materials ensures consistent electrical properties, critical for repeatable signal performance. Engineers must collaborate early with fabricators to select laminates meeting these specs, as variations in filler content or glass reinforcement influence impedance stability.

Mechanisms of Signal Loss in PTFE PCBs

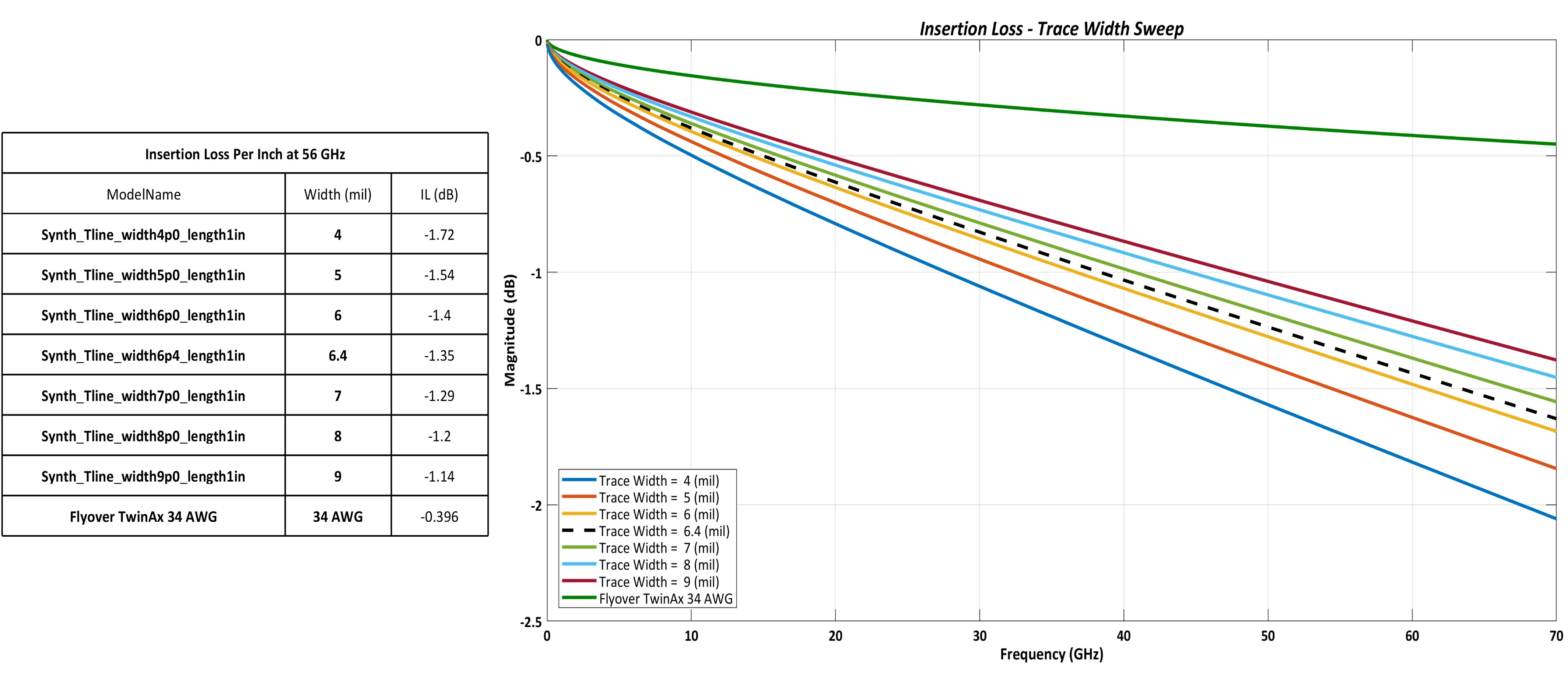

PTFE PCB signal loss arises primarily from dielectric absorption and conductor attenuation, both amplified at higher frequencies. Dielectric loss dominates in PTFE due to its low dissipation factor, where signal energy converts to heat proportional to frequency squared. Conductor loss stems from skin effect, confining current to the copper surface, and roughness scattering, which increases effective resistance. At 10 GHz and above, these combine to limit trace lengths before unacceptable attenuation occurs. Smooth, low-profile copper foils mitigate this by reducing surface area for loss mechanisms. Engineers calculate total insertion loss as the sum of these components to predict channel margins.

Material purity plays a key role; reinforced PTFE composites balance mechanical strength with low loss, though fillers slightly elevate the dissipation factor. Fabrication-induced defects like plating inconsistencies or fiber misalignment can introduce localized hotspots for loss. Testing via vector network analyzers reveals S21 parameters, guiding design iterations. Proper stackup design, with symmetric builds, prevents warpage that warps traces and alters loss profiles.

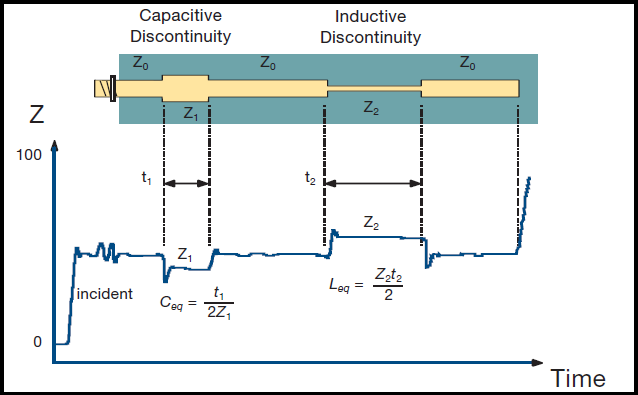

IPC-2221 provides guidelines on conductor geometries that influence loss, emphasizing uniform widths and minimal bends. Avoiding right-angle corners reduces return loss contributions, preserving signal power. In multilayer PTFE boards, via stubs act as resonators, adding periodic loss peaks; back-drilling or blind vias address this effectively.

Achieving PTFE PCB Impedance Matching

PTFE PCB impedance matching prevents reflections that distort waveforms and amplify noise. Characteristic impedance depends on trace width, dielectric height, and effective epsilon, with PTFE's low Dk enabling wider traces for the same 50-ohm target. Mismatches occur from etch tolerances, material thickness variations, or asymmetric stackups, causing voltage standing wave ratios above 1.5. Time-domain reflectometry verifies uniformity, identifying discontinuities early. Factory control of dielectric thickness to within 10% ensures predictable Z0 across the board.

Designers model microstrip or stripline configurations using field solvers, accounting for PTFE's isotropic properties. Reference planes tightly coupled to signal layers stabilize impedance, reducing sensitivity to fab variations. In high-density designs, differential pairs require even-odd mode matching for balanced performance. Prepreg selection matches core CTE, minimizing post-laminate shifts in spacing.

IPC-6012 outlines qualification tests for electrical performance, including impedance coupons that confirm design-to-fab correlation. Engineers specify test frequencies matching operational bands, ensuring margin for process drift. Routing parallel to weave direction in reinforced PTFE avoids anisotropy-induced mismatches.

Mitigating PTFE PCB Crosstalk

PTFE PCB crosstalk couples energy between adjacent traces via capacitive, inductive, or mutual mechanisms, degrading victim signals. Near-end crosstalk peaks from backward waves, while far-end affects timing at receivers. In PTFE, low Dk reduces capacitive coupling but demands wider spacing due to field fringing. Inductive crosstalk persists unless ground shielding isolates aggressors. At multi-GHz speeds, even short overlaps generate unacceptable noise.

Aggressor-victim spacing follows 3W or 5W rules, where W is trace width, proven to suppress coupling below -40 dB. Ground planes between layers provide return paths, shortening loops and attenuating fields. Differential routing cancels common-mode crosstalk effectively. Vias near bends interrupt coupling paths, but staggered placement prevents via crosstalk.

Staggered trace lengths and length tuning minimize simultaneous switching noise contributions. Factory via plating quality affects shielding; uniform coverage per IPC standards prevents pinholes that leak fields.

Best Practices for Design and Fabrication

Optimizing PTFE PCBs starts with stackup planning, alternating signal and plane layers for confinement. Simulate full channels including connectors and packages to capture end-to-end integrity. Select low-roughness copper per foil specs, as skin depth shrinks to microns at high frequencies. Minimize via count with blind/buried structures; transition stubs degrade beyond quarter-wavelength.

Fabrication demands plasma cleaning for adhesion without residue that absorbs signals. Lamination under vacuum prevents air pockets elevating local loss. Etch control to 0.001 inch tolerances holds impedance. Post-process, bake-out removes moisture, stabilizing Dk.

Assembly considerations include low-residue fluxes to avoid dielectric contamination. Thermal cycling per qualification specs verifies stability. Collaborate on DFM reviews, specifying coupons for loss, impedance, and crosstalk validation.

Troubleshooting Signal Integrity Issues

Common pitfalls include unexpected loss spikes from rough copper or voids. TDR anomalies signal etch undercuts; adjust fab parameters. Elevated crosstalk traces back to inadequate ground referencing; add stitching vias. Eye closure post-assembly points to via resonance; employ blind vias. Systematic measurements correlate sim-to-hardware, refining models.

Conclusion

PTFE PCBs offer unmatched potential for high-performance signal integrity through low-loss properties. Prioritizing PTFE PCB signal loss reduction, precise PTFE PCB impedance matching, and effective PTFE PCB crosstalk mitigation unlocks this advantage. Standards like IPC-4101, IPC-2221, and IPC-6012 guide consistent outcomes. Factory insights emphasize material control and process discipline. Engineers applying these principles deliver reliable boards for next-generation systems.

FAQs

Q1: What causes PTFE PCB signal loss at high frequencies?

A1: Dielectric dissipation from the loss tangent and conductor skin effect on rough copper primarily drive PTFE PCB signal loss. Low Df in PTFE keeps this minimal, but frequencies above 10 GHz amplify both. Smooth foils and short traces per IPC-2221 guidelines counteract this effectively. Proper stackup symmetry prevents additional fab-induced losses.

Q2: How do you ensure PTFE PCB impedance matching in multilayer designs?

A2: Calculate Z0 using trace geometry, dielectric height, and PTFE's low Dk, then verify with TDR coupons. Symmetric builds and tight plane coupling maintain tolerance. IPC-6012 qualification confirms fab accuracy. Simulate variations to build margins against etch and thickness drift.

Q3: What spacing rules minimize PTFE PCB crosstalk?

A3: Apply 3W to 5W separation between traces, with ground planes shielding layers. Stagger vias and length-match pairs to reduce simultaneous switching. These practices drop coupling below -40 dB in PTFE's field environment. Reference planes shorten inductive loops.

Q4: Why is copper foil selection critical for PTFE PCBs?

A4: Low-profile copper reduces skin effect loss at high frequencies, complementing PTFE's low Df. Rough surfaces scatter signals, increasing insertion loss. Specify per standards for high-speed integrity.

References

IPC-4101 — Specification for Base Materials for Rigid and Multilayer Printed Boards. IPC

IPC-2221 — Generic Standard on Printed Board Design. IPC

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC