Yesterday we covered output ripple voltage of boost DC-DC converters. This article explains how switching noise at the output of a boost power supply is generated and describes design techniques to reduce that high-frequency noise.

Introduction

Switching DC-DC converters produce ripple at the switching frequency and its harmonics. In addition, switching action generates high-frequency noise that can reach hundreds of MHz. These high-frequency components can cause problems in downstream circuitry. In buck converters some high-frequency noise appears at the input and can couple to the output; in boost converters, however, fast voltage and current transients at the output node create significant high-frequency noise at the output.

This article series examines mechanisms that generate high-frequency noise in boost DC-DC converters and presents practical techniques to reduce it.

How a Boost DC-DC Converter Operates

In a boost DC-DC converter, when the low-side switch conducts the inductor current increases and energy is stored in the inductor. When the low-side switch turns off, the stored energy is released and the inductor generates a voltage that raises the switch node above the input, producing an output voltage greater than the input. Fast voltage and current transitions during switching cause high-frequency oscillations that can propagate and radiate through the output path and cause malfunction in the load.

Detailed Turn-off Behavior of the Low-side Switch

When the low-side MOSFET is fully on, the drain-to-source resistance is RDSON and the drain voltage equals RDSON times the inductor current. When the MOSFET gate drive begins to turn off, the drain-source resistance increases and the drain voltage rises. The MOSFET has an output capacitance (COSS). Part of the inductor current is used to charge COSS during the drain voltage rise. Conduction losses through the MOSFET resistance and the charge injected into COSS cause energy loss while the drain voltage continues to rise.

When the switch node voltage VSW exceeds the output voltage, the high-side rectifier diode becomes forward biased. Even if the forward voltage VF is exceeded, the diode does not conduct immediately because of diode conduction delay. The switch node can rise above the sum of VOUT + VF for several nanoseconds. After the diode's forward conduction delay, the diode conducts and the inductor current begins charging the output capacitor.

Output Capacitor and Wiring Inductance

Because of the rectifier diode conduction delay, the elevated VSW is applied to the output capacitor and quickly charges it due to the large potential difference. Prior to this, the output capacitor had been discharging to supply the load; after diode conduction it is rapidly charged by the inductor current. The capacitor current therefore reverses in nanoseconds. Even though the equivalent series inductance (ESL) of output capacitors is only a few nH to tens of nH, a rapid current change ΔI over a short time ΔT generates a voltage spike ΔV = ΔI × L / ΔT across the capacitor. As a result, the output capacitor experiences a high-voltage spike immediately after the rectifier diode begins conducting.

Low-side Switch Output Capacitance and Ringing

As COSS is charged to a level comparable to the spike on the output capacitor, energy stored in COSS is released into the output capacitor and into loop inductance, storing energy in the magnetic field of the inductance. When COSS discharges back toward VOUT, the voltage difference disappears and the magnetic energy in the loop inductance reaches a peak. Energy then transfers back and forth between COSS and the loop inductance, producing oscillation. Strictly speaking, the resonant inductance is the sum of the ESL and the inductance of the current loop, and the resonance frequency FZ is

FZ = 1 / (2π√(L × COSS)).

With loop inductance on the order of a few nH and COSS in the tens to hundreds of pF, this resonance typically falls in the tens to hundreds of MHz range. Ringing at the switch node and at the output capacitor generates high-frequency noise that can propagate on the power output and cause misbehavior in the load.

Behavior When the Low-side Switch Turns On

Just before the low-side switch turns on, the output voltage plus VF is applied to the low-side drain and the inductor current flows through the rectifier diode. As the low-side switch turns on, inductor current transfers from the high-side diode to the low-side switch and the switch node voltage VSW falls toward ground, reverse-biasing the rectifier diode. Because the diode had current flowing, charge carriers remain in the junction, so the diode does not stop conducting immediately when reverse-biased; a brief reverse current flows. This reverse recovery current causes a rapid change of current in the output loop.

When the reverse recovery current ends, the diode becomes reverse-biased and the junction depletion region restores, behaving as a smaller capacitance. In synchronous rectification, the high-side FET includes a parasitic diode and COSS formed by the depletion region, the MOSFET structure, and gate capacitance. The charging currents associated with reverse recovery or charging COSS drive an LC resonance formed by the high-side capacitance and loop inductance, producing high-frequency noise sourced by the reverse-flowing current.

Methods to Suppress High-Frequency Noise in Boost Converters

Practical approaches to reduce high-frequency noise include: reducing resonant energy and loop inductance, increasing conduction speed and minimizing reverse recovery current, minimizing inductance in the output loop, reducing loop area through component placement and PCB patterning, and adding LC filtering since resonance cannot be completely eliminated.

Reduce Resonant Energy and Inductance

Lowering the energy that drives ringing during low-side switch transitions reduces high-frequency noise. Resonance occurs when energy transfers between inductance and capacitance, so reducing either the inductance or the capacitance in the output loop reduces LC resonance. Reducing the loop inductance reduces stored magnetic energy and therefore lowers the amplitude of LC ringing and the generated high-frequency noise.

Increase Switching Speed and Minimize Reverse Recovery Current

To reduce the energy that causes ringing when the low-side switch turns off, reduce overshoot at the switch node VSW. To shorten high-side conduction delay, choose diodes with low conduction delay.

To reduce ringing energy when the low-side switch turns on, minimize reverse recovery current. For low output voltages with diode rectification, use Schottky barrier diodes. Unlike PN-junction silicon diodes, Schottky diodes do not use minority-carrier storage and therefore have negligible reverse recovery current; their VF is also lower, improving efficiency. However, Schottky diodes exhibit higher reverse leakage current than silicon diodes, which can raise concerns about thermal runaway at high output voltages and elevated temperatures. When output voltages reach several hundred volts and Schottky diodes cannot be used due to reverse-voltage and thermal concerns, fast-recovery silicon diodes are a good alternative because they have reduced reverse recovery current compared to standard silicon diodes. While their VF is higher, at high output voltages this has limited impact on overall efficiency.

When using synchronous rectification, the high-side FETs include parasitic diodes that cannot be replaced with better diodes. During dead time current flows through the parasitic diode, but its diode characteristics are similar to PN-junction silicon diodes and are not ideal. In synchronous designs, minimize dead time and control gate timing so the current through the parasitic diode is as small as possible, reducing conduction delay and reverse recovery effects.

Minimize Inductance in the Output Loop

When the high-side switch conducts, a fast pulse of current charges the output capacitor. The ESL of the output capacitor produces a voltage spike and stores magnetic energy that becomes the source of resonance. Choosing output capacitors with low ESL reduces the peak of the pulse voltage and the stored energy, thereby reducing resonance and high-frequency noise. However, boost converters require high-voltage, high-capacitance capacitors, which are often physically large and have larger ESL. One solution is to parallel N capacitors each with 1/N of the total capacitance instead of a single large capacitor. Smaller capacitors have lower ESL, and paralleling N of them further reduces ESL approximately by 1/N. This approach increases component count and cost, which must be considered.

Additionally, adding small-value ceramic capacitors can lower the effective ESL in the output loop. The fast current pulses into the output capacitor last only a few to tens of ns. If the pulse current is a few amps, the total charge may be on the order of 100 nC, so even sub-microfarad capacitors with low ESL can absorb that charge without large voltage excursions. For many designs, placing a small ceramic capacitor around 0.1 μF close between the high-side output node and the low-side ground node, with the distance between them minimized, avoids the larger ESL of the main output capacitor and reduces loop inductance significantly.

Minimize Output Loop Area by Component Placement and PCB Layout

The ESL of the output capacitor is often the dominant contributor to loop inductance, and paralleling small ceramics reduces that. PCB trace layout also contributes inductance because the output loop itself forms a conductive loop. Minimize the routing length between components to reduce trace inductance. Loop inductance is proportional to loop area, so minimize the loop area when placing components. Widening traces that form the loop can also reduce the effective loop area by filling the interior of the loop, further reducing inductance.

Resonant currents in the output loop generate changing magnetic fields in the surrounding space. The radiated field strength is also proportional to the loop area. Reducing the loop area decreases both the magnitude of emitted noise and the EMI radiated into space, so minimizing loop area is a crucial noise mitigation measure.

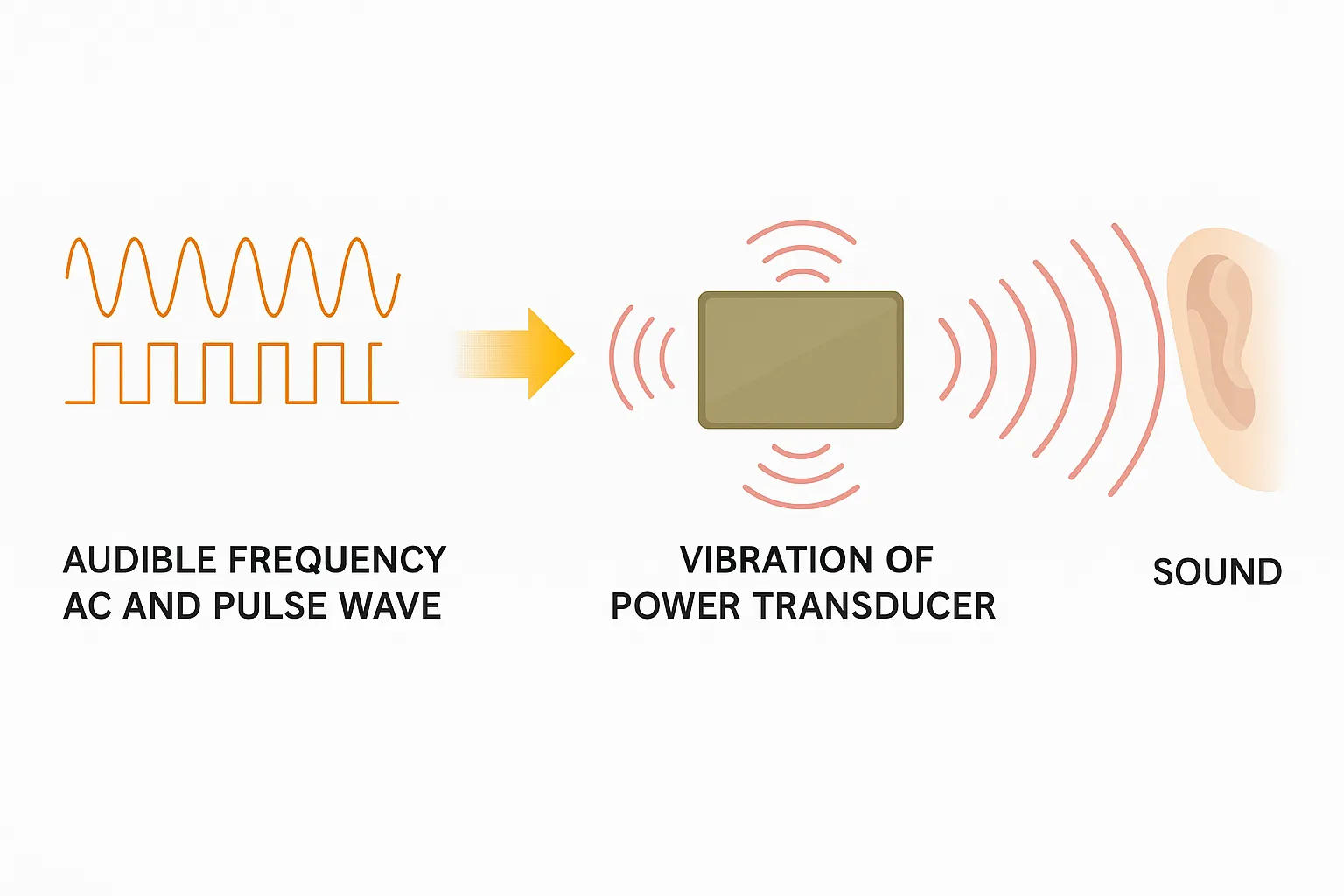

Add LC Filtering Because Resonance Cannot Be Eliminated

Because COSS and output loop inductance cannot be reduced to zero and switching edges are getting faster, high-frequency noise cannot be fully eliminated at the source. A practical method to prevent high-frequency noise from reaching the load is to add an LC low-pass filter on the power output. Such filters often use ferrite beads that present resistive impedance at high frequencies to dissipate HF energy as heat, together with small-value ceramic capacitors (for example, on the order of 1000 pF) that have low ESL at hundreds of MHz. Ferrite beads are particularly effective because their high-frequency impedance is largely resistive and converts HF noise into heat, making them effective noise suppression components.