IEDM is the largest international conference on semiconductor device technologies and process technology. This report summarizes notable presentations beyond memory, covering next-generation CMOS, techniques for integrating devices into multilayer interconnect processes, in-sensor computing, wide-bandgap devices, and image sensors. Several prominent talks focused on next-generation CMOS; these are grouped into complementary FETs, 2D materials, and multilayer interconnect topics.

Stacking complementary FETs to halve silicon area (CFET)

The first topic in next-generation CMOS logic is the complementary FET (CFET). CMOS logic requires at least two transistors: one n-channel MOSFET and one p-channel MOSFET. The simplest logic gate, the inverter, consists of one n-channel and one p-channel MOSFET, which together occupy the area of two transistors. CFET stacks these two transistor types in three dimensions. In principle, CMOS logic can be achieved using the silicon area of a single FET, effectively halving silicon area compared with conventional CMOS. However, the fabrication process is complex and presents major challenges.

At IEDM 2023, CFET development advanced significantly. TSMC and Intel presented monolithically stacked CMOS circuits with lower- and upper-layer FETs. TSMC demonstrated a CFET prototype that monolithically stacks an n-channel FET atop a p-channel FET. All FETs used a nanosheet structure, with a gate pitch of 48 nm. The fabricated yield exceeded 90%, and the on/off ratio exceeded six orders of magnitude.

Intel designed a CFET prototype that monolithically stacks three n-channel FETs above three p-channel FETs. All FETs used a nanoribbon structure (structurally similar to nanosheets). A CMOS inverter prototype with a 60 nm gate pitch was fabricated and its operation confirmed.

2D materials forming GAA nanosheet channels

Another promising candidate for next-generation CMOS logic transistors uses two-dimensional (2D) materials, specifically transition metal dichalcogenides (TMDs), as the channel material. As MOSFET channel lengths scale down, short-channel effects become a major concern, causing threshold-voltage reduction and increased variability. One mitigation is to thin the channel. TMDs readily form monolayers and can, in principle, provide the thinnest possible channels.

TMD channels were initially considered for scaling planar MOSFETs by removing the need for fin structures. Recently, using TMDs as channel materials for gate-all-around (GAA) structures has gained traction. Candidate materials include molybdenum disulfide (MoS2), tungsten disulfide (WS2), and tungsten diselenide (WSe2).

Research consortia including TSMC developed an n-channel FET with a nanosheet structure where the channel material is a monolayer of MoS2. The gate length was 40 nm. The device exhibited a relatively high threshold voltage of about 1 V (normally-off operation), an on current of roughly 370 μA/μm (Vds ≈ 1.0 V), and an on/off ratio of 10^8. A joint imec-Intel team fabricated prototype n-channel and p-channel MOSFETs using candidate 2D channel materials on 300 mm wafers, evaluating MoS2, WS2, and WSe2. MoS2 monolayers were suitable for n-channel FETs, while multi-layer WSe2 fit p-channel FETs.

Another consortium including TSMC developed 2D-material transistors whose current-voltage characteristics matched those of conventional n-channel and p-channel FETs. MoS2 (an n-channel material) and WSe2 (a p-channel material) were grown on sapphire and transferred chip-by-chip onto silicon wafers. Intel also prototyped GAA-structured 2D-channel FETs and achieved relatively high mobilities for both n-channel and p-channel devices.

Graphene, ruthenium, and tungsten as Cu interconnect alternatives

Multilevel interconnects are a critical enabling technology for scaling CMOS logic. There is concern that the resistivity of copper multilayer interconnects will increase rapidly with scaling, so research into copper alternatives is active. Candidate materials include graphene, ruthenium (Ru), and tungsten (W).

TSMC reported experiments using graphene, a sheet-like carbon allotrope, for multilayer interconnects. When comparing resistances of interconnect prototypes of varying widths with copper interconnects, graphene interconnects narrower than 15 nm exhibited lower resistivity than copper interconnects. Graphene contact resistivity was also found to be four orders of magnitude lower than copper. Intercalating metal ions into graphene can improve its interconnect electrical properties, making graphene a promising material for next-generation interconnects.

imec fabricated Ru two-level fine-pitch interconnect prototypes with high aspect ratios (AR) of 6 to 8 and pitches from 18 nm to 26 nm, using semi-damascene and fully self-aligned vias. For AR=6, Ru lines with a width of 10 nm (corresponding to an 18–20 nm pitch) showed lower resistance than modeled Cu lines at AR=2.

Applied Materials developed a low-resistance interconnect architecture that leverages W. It targets technology nodes of roughly 2 nm and above, using W liners, W gap fill, and WCMP (chemical mechanical polishing) as core process technologies.

Embedding memory and other elements in the BEOL

An unconventional approach studied at the conference was embedding memory and other elements into the back-end-of-line (BEOL) interconnect process. Since multilayer interconnects sit above CMOS logic, integrating components in the BEOL does not increase silicon area in theory, offering a way to increase memory and device density.

A joint group from Stanford University and other universities presented design guidelines for embedding oxide semiconductor (OS) gain-unit transistor-type memory elements into multilayer interconnect processes. They selected indium tin oxide (ITO) FETs as the OS components and compared OS/Si hybrid units with OS/OS gain units.

imec developed MRAM technology that reduces spin-orbit torque (SOT) layers and magnetic tunnel junction (MTJ) pillars to comparable dimensions. The approach claims up to a threefold reduction in power consumption versus conventional technology, a rewrite-cycle lifetime up to 10^15, and reduced cell area.

A team at UCLA demonstrated integration of voltage-controlled MRAM and CMOS peripheral circuits. MRAM switching time was extremely short, 0.7 ns at 1.8 V. The prototype chip achieved an average read access time of 8.5 ns and a write endurance of 10^11 cycles.

In-sensor computing

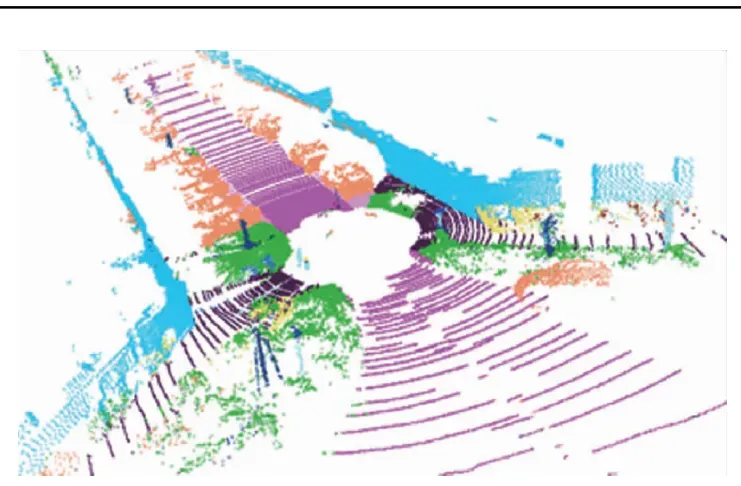

In-sensor computing, which embeds computation into sensors, was another focus. A joint group including Macronix demonstrated an intelligent image sensor based on 3D monolithic integration. Using 20 nm node FinFET technology, a DRAM-like storage layer was monolithically stacked above the CMOS circuit layer, with an additional layer of phototransistor arrays made from the 2D material MoS2 stacked on top. The phototransistor array layout was 5 × 5.

A joint group from Xidian University and Westlake University designed an optoelectronic neuron composed of a phototransistor and a threshold switch for spiking neural networks, performing compressed encoding of continuous-time sensor signals (phototransduction signals).

Integrating GaN power transistors and CMOS drivers on silicon wafers

There is active work on integrating GaN-based HEMTs, a wide-bandgap compound semiconductor, on silicon wafers. Intel integrated GaN power transistors and CMOS drivers on 300 mm silicon wafers. The CMOS drivers combined GaN enhancement-mode n-channel MOSHEMTs and Si p-channel MOSFETs. The GaN layer used Si (111) wafers. For SiMOSFETs, another Si wafer with a (100) orientation was bonded and thinned to leave a thin (100) layer used as the channel.

CEA-Leti developed AlN/GaN/Si MIS-HEMTs for Ka-band power amplifiers, compatible with 200 mm Si CMOS processes. By optimizing the SiN gate dielectric, prototypes achieved ft = 81 GHz and fmax = 173 GHz. At 28 GHz, the power-added efficiency (PAE) reached 41% at 20 V, assuming performance comparable to GaN/SiC devices.

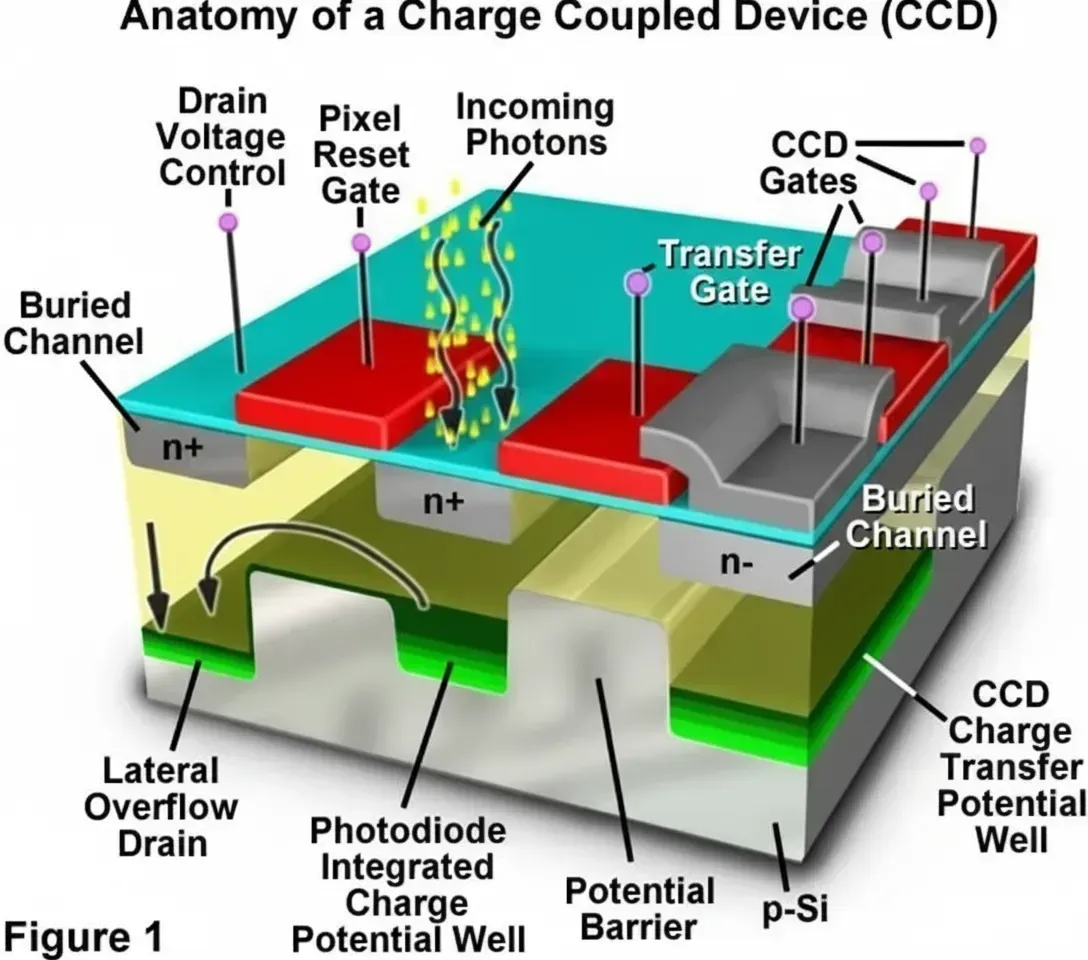

64-megapixel CMOS image sensor with 0.5 μm pixels

Notable image sensor results included increased pixel counts, reduced pixel sizes, lower noise, and improved autofocus performance. Samsung demonstrated a 64-megapixel high-resolution CMOS image sensor with small pixels measuring 0.5 μm square. Three silicon chips were stacked using copper electrode hybrid bonding, connecting a photodiode and readout circuitry for each pixel. Compared with conventional designs, random telegraph signal (RTS) noise was reduced by 85% and floating diffusion (FD) conversion gain increased by 67%.

OmniVision Technologies developed an HDR global shutter CMOS image sensor with a 2.2 μm pixel pitch by bonding two silicon wafers. Fixed pattern noise (FPN) was 1.2 e- rms and temporal noise was 3.8 e- rms.

Canon demonstrated a dual-pixel cross CMOS image sensor prototype where a pair of photodiodes are rotated by 90 degrees. Full-direction phase-detection autofocus was implemented, achieving autofocus at illuminance as low as 0.007 lux.