Full-frame CCD

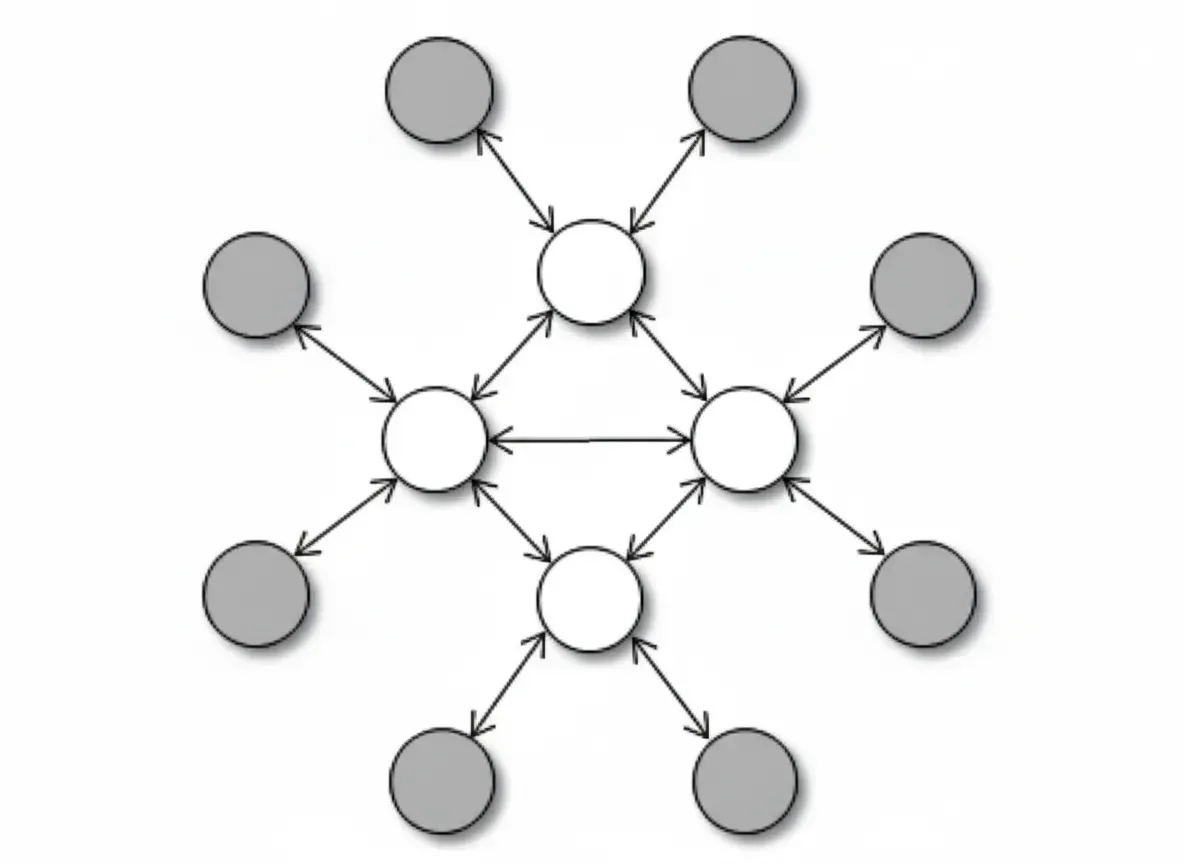

The semiconductor region can function both as a photodetector and as a charge-transfer device. In a full-frame CCD, pixel sites convert incident photons into charge during integration. After integration, the charge packets are shifted vertically through the pixel array into a horizontal transfer register.

CCD pixel data are obtained by applying carefully timed clock signals. These clock signals sequentially create potential wells and barriers in the device's charge-transfer structure. In a full-frame CCD, the control voltages must be applied to regions that also serve as the photodetector, so the gate electrodes are made from transparent polysilicon.

Full-frame CCDs are relatively simple to manufacture and allow the entire CCD surface to be photosensitive. This maximizes the number of pixels that can be placed in a given silicon area and maximizes the light-sensitive portion of each pixel that actually converts photons into electrons.

A major limitation is the need for a mechanical shutter or a synchronized, short-duration light source such as a strobe. The photosensitive area of a CCD remains active regardless of when a readout is initiated. Without a mechanical shutter to block incident light after the end of the exposure period, charge packets generated during the intentional integration period can be corrupted by light arriving during readout.

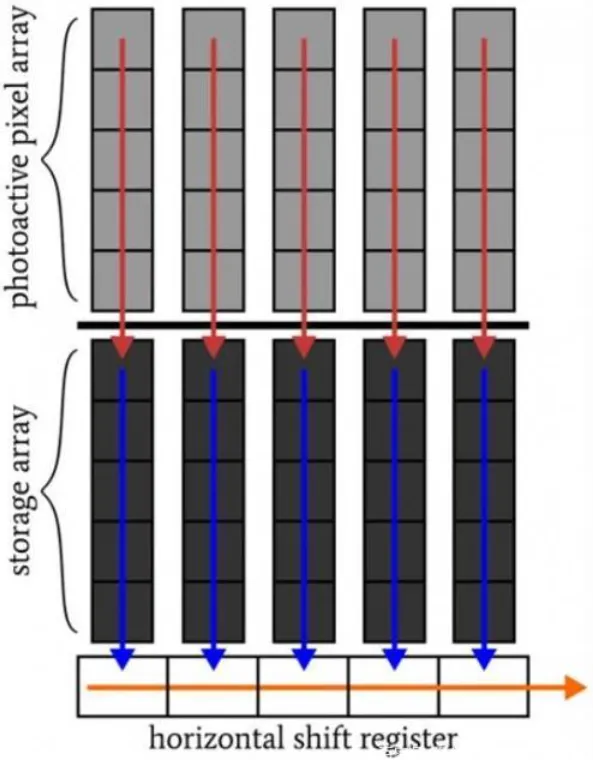

Basic architecture of a full-frame CCD

Frame-transfer (FT) CCD

To avoid mechanical shutters, many systems prefer electronic exposure control. Mechanical shutters add complexity, cost, potential failure modes, and additional power consumption that is undesirable in battery-powered applications.

A frame-transfer CCD preserves some of the advantages of a full-frame CCD while largely eliminating the need for a shutter. The approach splits the CCD into two equal areas: an active photosensitive imaging array and a shielded storage array. After integration, the charge packets from all pixels are rapidly transferred into the storage array and then read out from the storage area. While the storage locations are being read, the active pixels can accumulate charge for the next frame, enabling higher frame rates than a full-frame CCD.

The FT architecture does not completely eliminate smear since vertical transfer is fast but not instantaneous. Light reaching the sensor during vertical transfer can alter image information. The main drawbacks of FT designs are increased die area and cost, because essentially a full-frame sensor is used with half the pixels available for imaging.

Frame-transfer CCD adds a storage array to the full-frame architecture

Interline-transfer (IT) CCD

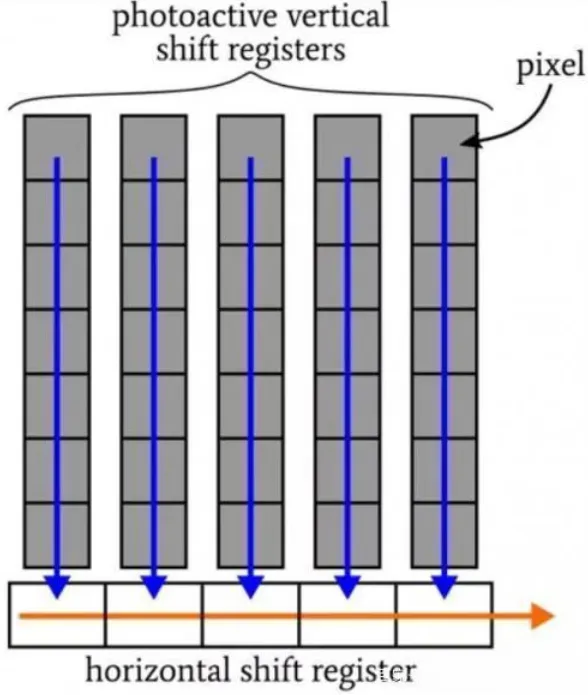

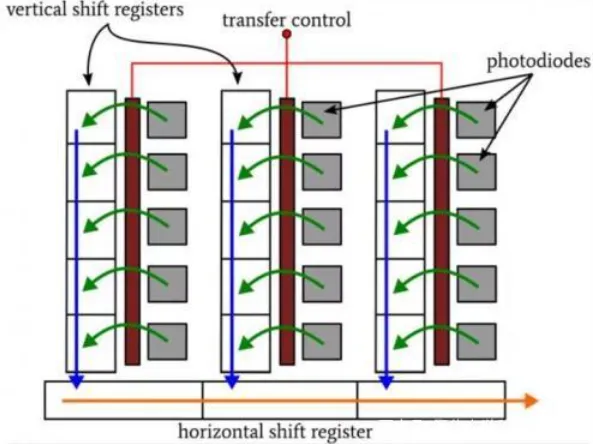

To reduce smear to negligible levels, charge must be transferred rapidly into a storage region. Interline-transfer CCDs accomplish this by providing a storage and transfer region adjacent to each photosensitive site. At the end of exposure, each charge packet is simultaneously transferred into non-photosensitive vertical shift registers.

Interline CCDs can implement an electronic shutter with minimal smear and, like frame-transfer devices, can continue integrating while readout occurs, maintaining high frame-rate capability. Some smear can still occur if photogenerated charge leaks from the photosensitive columns into adjacent vertical registers during readout. If high frame rate is not required, this can be avoided by delaying integration until readout is complete.

Interline CCDs avoid the large storage area needed for frame-transfer designs, but they introduce reduced fill factor: each pixel is partly occupied by the photodiode and partly by vertical transfer structures, so a portion of each pixel is insensitive to light. This loss of sensitivity is typically mitigated by adding microlenses that concentrate incident light onto the photosensitive area, although microlenses introduce their own set of engineering challenges.

In the interline-transfer architecture, storage and vertical-transfer regions are located between photosensitive columns.

Conclusion

This article summarized the primary architectural trade-offs involved when designing CCD image sensors. Full-frame CCDs are straightforward and remain suitable for systems that do not require high frame rates and can tolerate a mechanical shutter or strobed illumination. Frame-transfer and interline-transfer CCDs offer important advantages for many applications, particularly where higher frame rates or shutterless operation are required.