Introduction

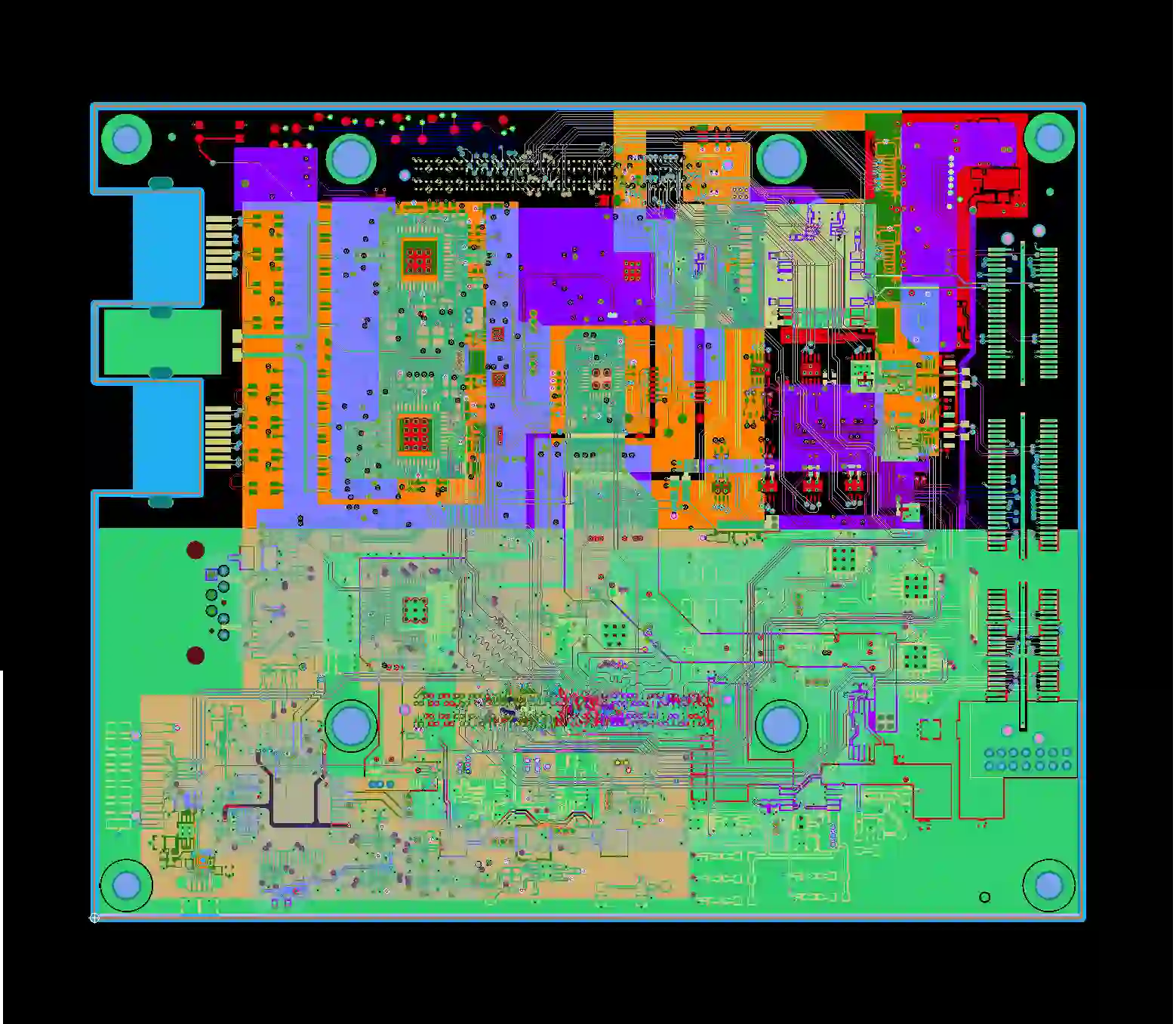

In the landscape of modern electronics, multilayer HDI (High-Density Interconnect) PCBs serve as the backbone for high-performance computing, advanced telecommunications, and mission-critical control modules. As layer counts escalate from 4 to 10+, the sensitivity of the manufacturing process increases exponentially—particularly regarding via-in-pad geometry, sequential lamination stack-up, and registration accuracy. As a seasoned engineer, I have found that the majority of production bottlenecks are not rooted in fundamental design flaws, but in a disconnect between design intent and the physical constraints of the fabrication process. This article explores the most common Engineering Queries (EQs) in multilayer HDI projects and outlines how proactive DFM (Design for Manufacturing) alignment can transform your production efficiency and first-pass yield.

Factory teams frequently observe that most engineering queries are not caused by fundamental design errors but by incomplete alignment between design intent and manufacturable constraints. This makes DFM review a critical step for multilayer HDI boards.

Why Engineering Queries Are the Quality Gate for High-Layer HDI PCBs

Engineering queries, often called EQs, are clarification requests raised during CAM or DFM review before production begins. For 4 to 10 layer HDI PCB designs, EQs typically focus on via structures, layer stack definitions, impedance control requirements, and fabrication tolerances. These questions are essential because HDI structures involve microvias and sequential lamination steps that require precise manufacturing alignment.

Without proper clarification, small ambiguities in design data can lead to incorrect stack execution or drilling strategy. This may result in yield loss, signal integrity deviation, or assembly failure. Therefore, EQ resolution is a core part of ensuring manufacturability in HDI PCB production.

Common EQ Types for Multilayer HDI PCB

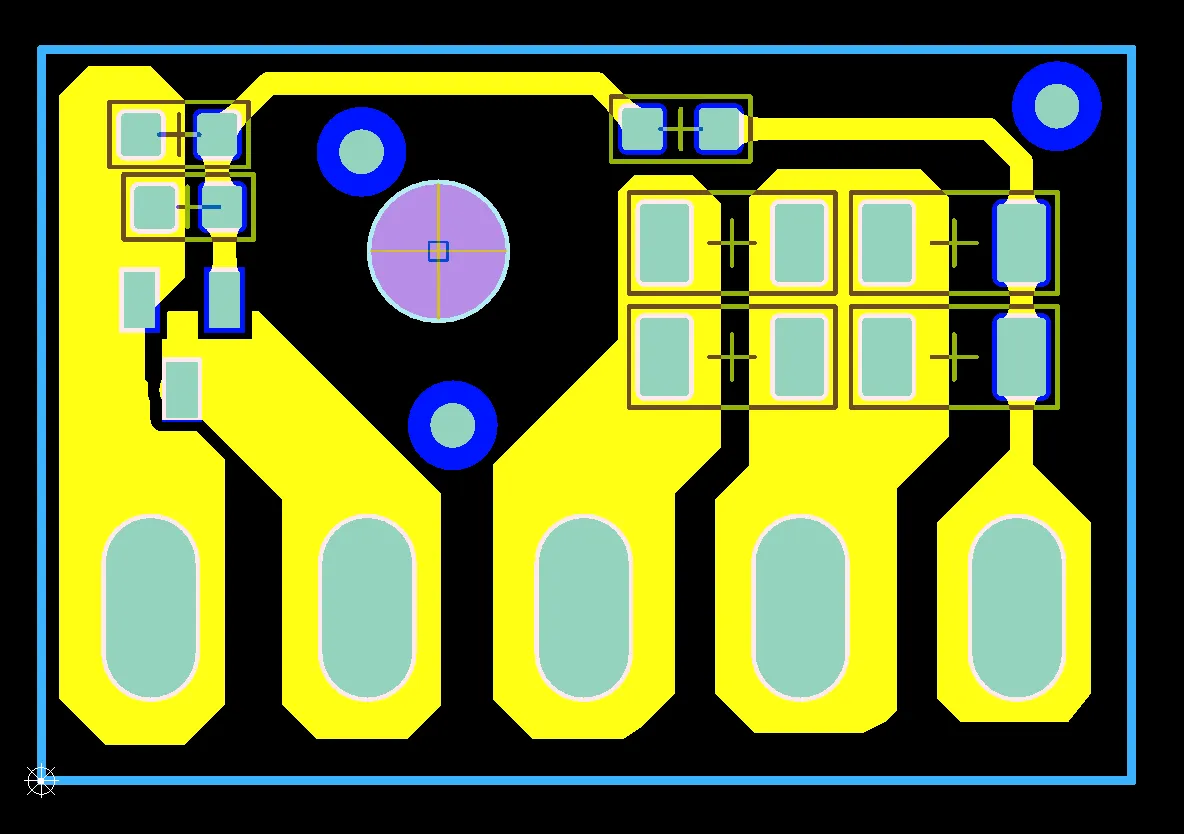

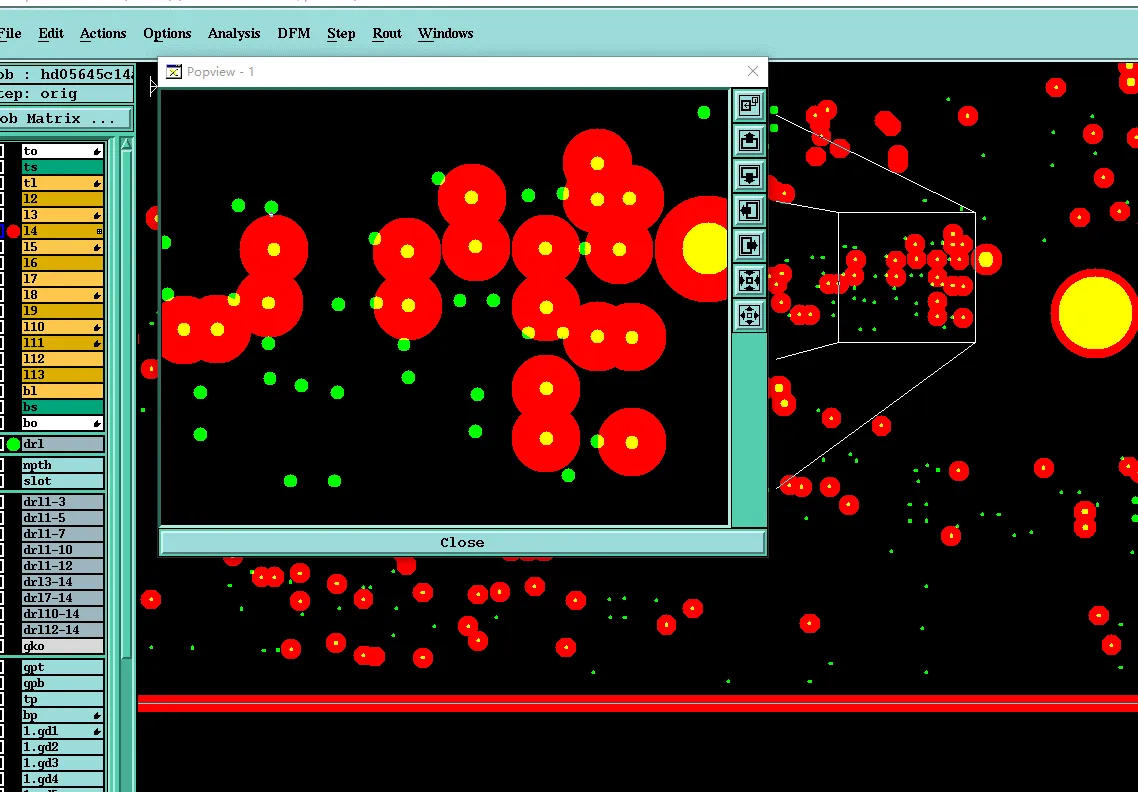

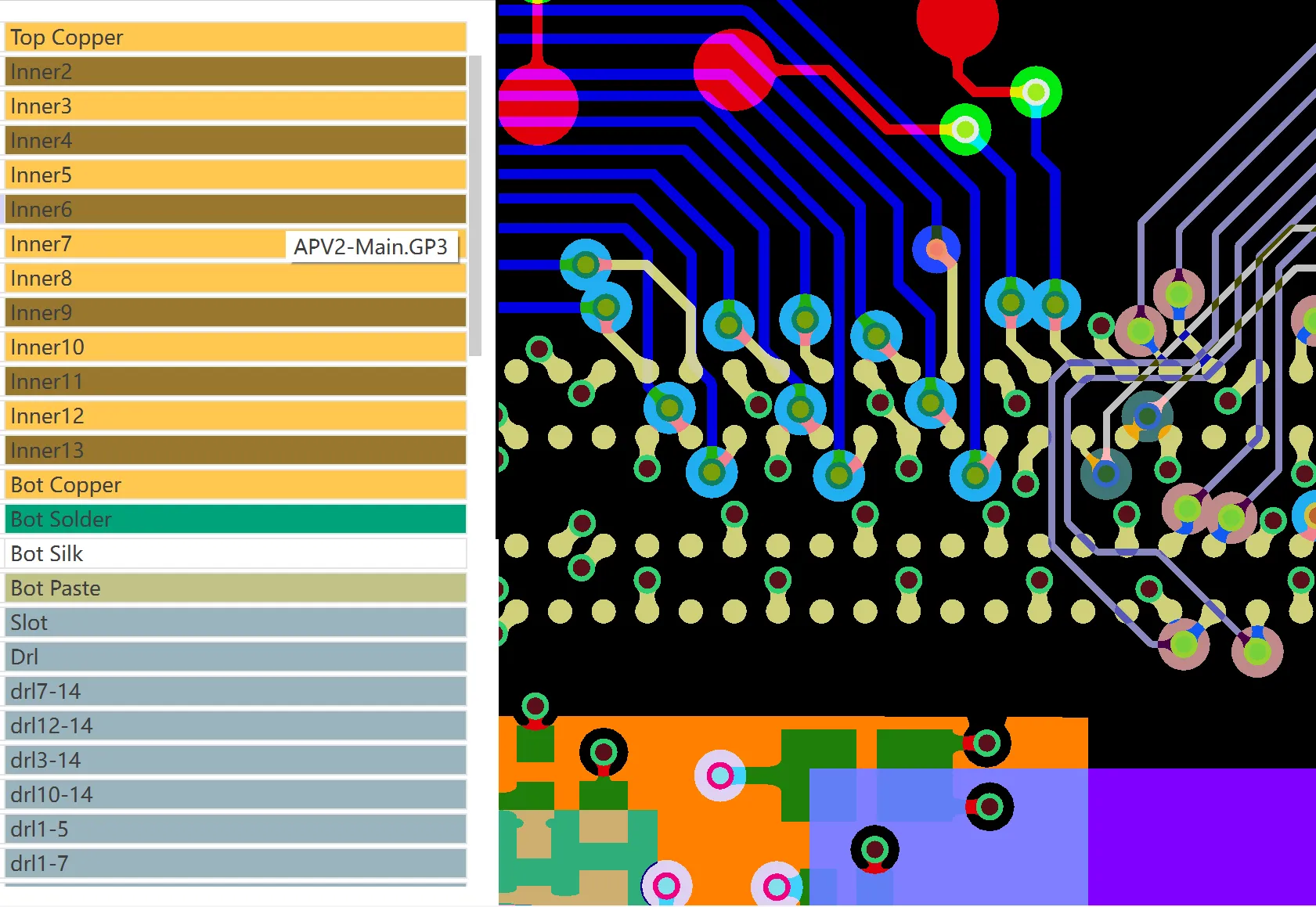

Via structure definition is one of the most frequent engineering queries in 4 to 10 layer HDI PCB manufacturing. Designers may use blind vias, buried vias, and microvias across multiple sequential lamination stages, but the fabrication intent is sometimes unclear in Gerber or ODB data. During DFM review, CAM engineers often request confirmation of via stack combinations and drilling sequences. If not clarified, it can lead to incorrect via build up or non manufacturable stack transitions.

Layer registration and annular ring requirements generate frequent EQs in higher-count multilayer HDI boards. With more lamination steps in 6 Layer HDI PCB, 8 Layer HDI PCB, and 10 Layer HDI PCB compared to 4 Layer HDI PCB, cumulative registration tolerances become critical. Root causes include insufficient capture pad sizes, missing alignment fiducials, or inconsistent annular rings on inner layers. The DFM check highlights potential breakout or shorts in Gerber and drill data. Unresolved, misregistration risks via-to-pad misalignment that may only surface after assembly and functional testing.

Impedance control clarification is also frequently raised for 4 to 10 layer HDI PCB projects. Signal layers in HDI structures are tightly coupled with reference planes, and small stack deviations can affect impedance targets. Engineers typically flag missing dielectric thickness or unclear reference plane assignments during review. If not clarified, it may lead to signal integrity degradation in high speed applications.

Why HDI Constraints Demand Clarification

Most EQs in 4 to 10 layer HDI PCB projects originate from incomplete stack up definition or missing fabrication constraints in design files. Unlike standard PCBs, HDI boards require sequential build up processes that depend heavily on exact layer pairing and via sequencing. If design documentation does not explicitly define these parameters, engineering teams must raise queries to avoid fabrication risk.

Another key reason is the gap between design software output and real manufacturing capability. Some CAD tools allow complex via and routing combinations that may not be directly manufacturable without adjustments. This leads to CAM teams identifying inconsistencies during pre production validation and requesting clarification before proceeding.

DFM Best Practices for Faster HDI Turnaround

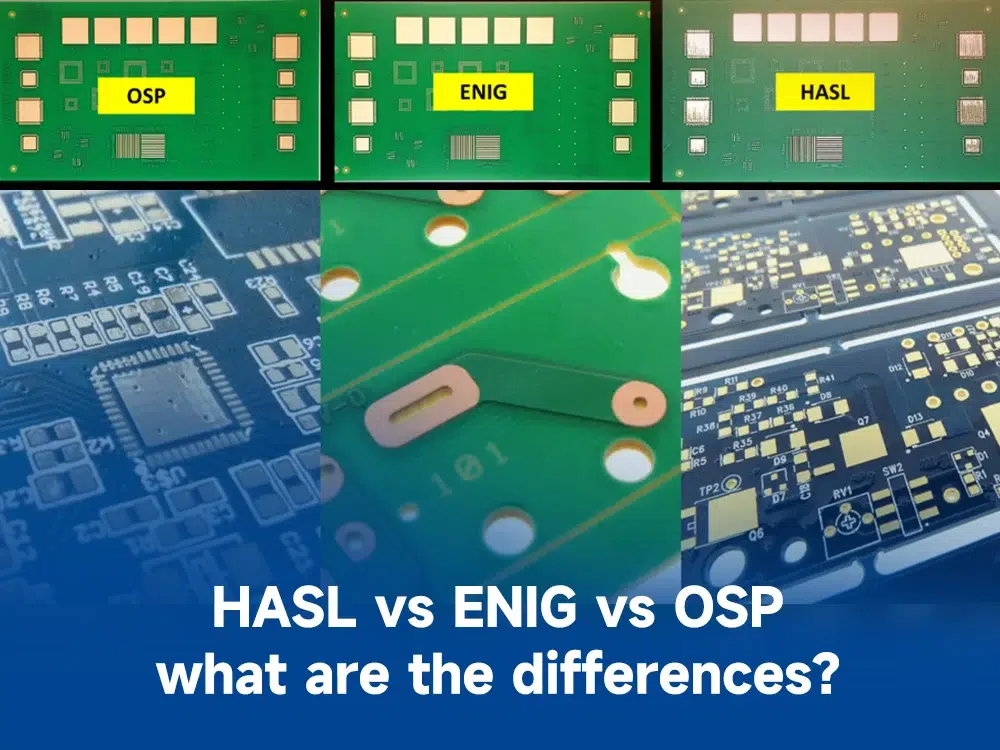

To reduce engineering queries in 4 to 10 layer HDI PCB manufacturing, the most effective approach is to provide a complete and explicit stack up definition, including dielectric thickness, copper weight, and via structures. Clear documentation of blind, buried, and microvia combinations helps eliminate ambiguity during CAM review.

Another important practice is early DFM alignment between design teams and fabrication engineers. By validating impedance requirements and layer pairing logic before finalizing the layout, many potential EQs can be avoided. This reduces iteration cycles and improves first pass yield.

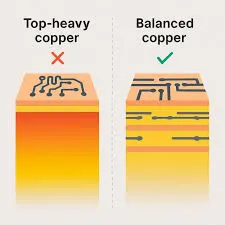

It is also recommended to maintain balanced copper distribution and avoid unnecessary asymmetry in high layer count HDI designs. This helps reduce warpage risk and improves lamination stability during manufacturing.

Conclusion

4 to 10 layer HDI PCB designs introduce higher manufacturing complexity due to dense interconnect structures and sequential build up processes. Most engineering queries arise from missing clarity in stack definition, via structure intent, or impedance requirements rather than fundamental design flaws.

By improving design documentation and aligning early with fabrication constraints, EQ frequency can be significantly reduced, leading to smoother production flow and higher manufacturing reliability.

FAQs

Q1: Why do 4 to 10 layer HDI PCB designs generate more engineering queries?

A1: Because HDI structures involve complex via stacking and sequential lamination, small design ambiguities require clarification. These details are critical for manufacturability and cannot be assumed during production.

Q2: What is the most common EQ in HDI PCB fabrication?

A2: Via structure definition, especially blind and buried via combinations, is the most common EQ. CAM engineers often need confirmation of stack sequences to ensure manufacturability.

Q3: How does stack up design affect EQ frequency?

A3: Incomplete or inconsistent stack up data leads directly to engineering queries. Clear dielectric and copper definitions significantly reduce clarification requests during CAM review.

Q4: What is the best way to reduce HDI PCB EQs?

A4: Providing complete stack up details, defining via structures clearly, and aligning with fabrication capabilities early in the design stage are the most effective methods to reduce EQs.

Reference

IPC 2221B Generic Standard on Printed Board Design. IPC 2003

IPC 6012E Qualification and Performance Specification for Rigid Printed Boards. IPC 2017

IPC 6016 Qualification and Performance Specification for High Density Interconnect Printed Boards. IPC 2013