Introduction

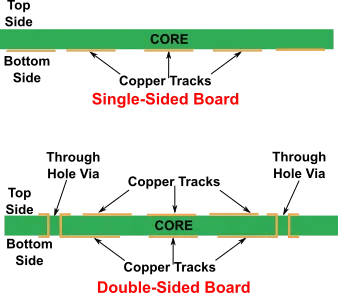

In actual production, 1 layer FR4 PCB and 2 layer FR4 PCB form the core of countless electronic assemblies ranging from consumer devices to industrial controls. Factory teams frequently observe that these seemingly simple boards still generate a steady stream of engineering queries during the initial DFM review phase. Even with standard FR4 material and basic layer counts, small discrepancies in copper layout, hole definitions, or mask design can require clarification before fabrication proceeds. These queries help align the designer's intent with the practical realities of etching, drilling, and lamination processes used every day on the shop floor. Addressing them early keeps lead times short and supports consistent first-pass yields without unnecessary rework.

What Are Engineering Queries and Why They Matter for 1 Layer FR4 PCB and 2 Layer FR4 PCB

Engineering Queries, or EQ, are targeted clarification requests sent by the manufacturer to the designer when design files contain ambiguities that could affect manufacturability or performance. For 1 layer FR4 PCB and 2 layer FR4 PCB these queries focus on elements such as copper distribution, hole attributes, and mask registration that directly influence standard production flows. They matter because even basic boards are produced in high volumes where unresolved issues quickly multiply into yield loss or assembly problems. In practice, factory engineering teams use EQ to bridge the gap between CAD output and actual process capabilities before committing material to the line. Timely resolution ensures the finished boards meet both electrical and mechanical expectations while minimizing schedule impact.

Common EQ Types for 1 Layer FR4 PCB and 2 Layer FR4 PCB

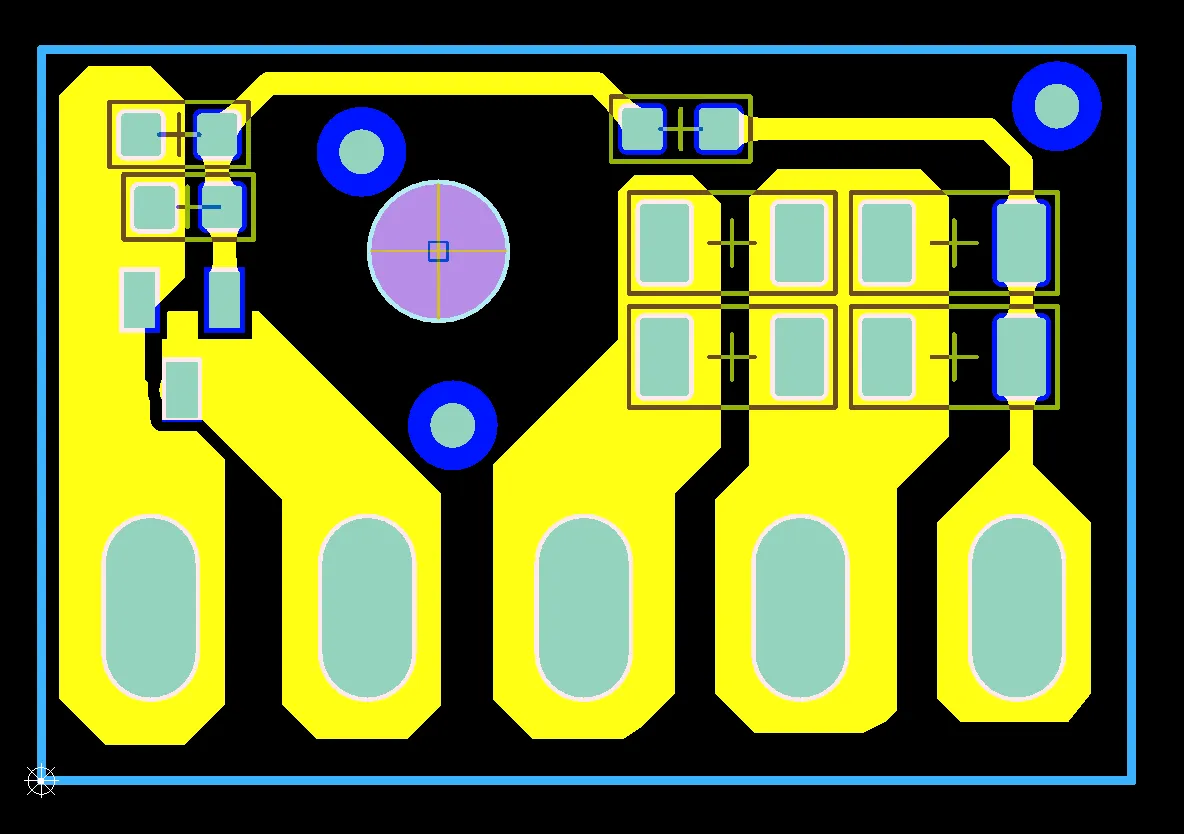

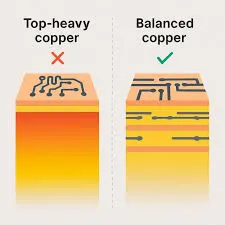

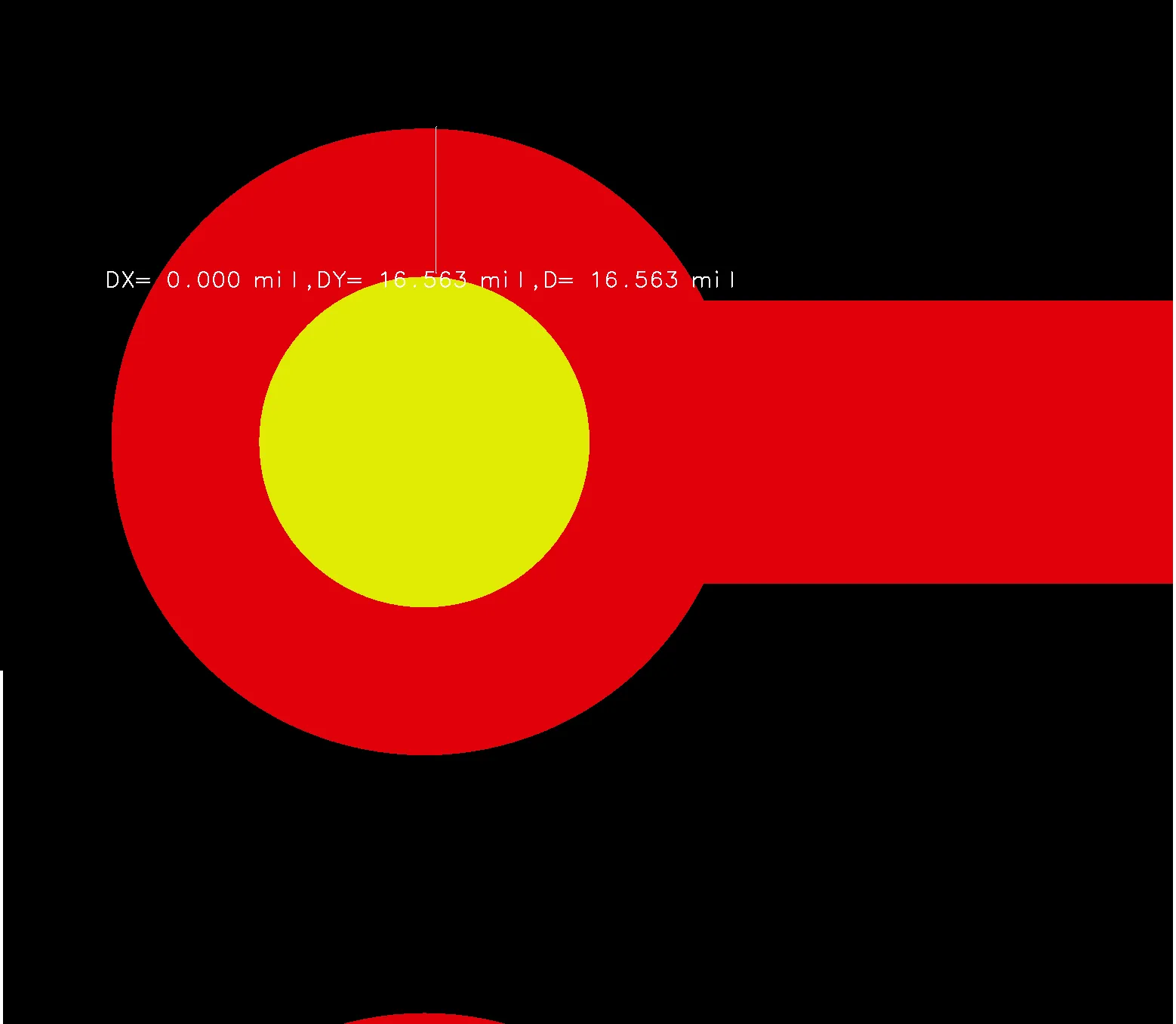

Copper Imbalance and Distribution Clarification

Copper imbalance between layers in 2 layer FR4 PCB designs appears regularly as an engineering query during file review. It happens when copper density on one side differs markedly from the opposite side, often because routing is concentrated on a single layer without compensating pours on the other. The DFM check or CAM analysis flags the imbalance through area calculations and requests confirmation of the designer's intent for thermal and mechanical stability. If left unaddressed the risk includes board warpage during lamination or reflow soldering that leads to component misalignment and potential solder joint failures. For 1 layer FR4 PCB the same principle applies to overall copper distribution relative to the board outline, though without interlayer interaction. Factory experience shows that confirming balance requirements early prevents downstream handling and assembly complications.

Annular Ring Minimum Requirement Confirmation

Insufficient annular ring on component pads and vias is another frequent EQ for both 1 layer FR4 PCB and 2 layer FR4 PCB. Designers sometimes choose pad diameters that leave too little copper extension around the drilled hole once tolerances for drill wander and registration are considered. During engineering review the CAM software automatically measures annular ring values and generates a clarification request when minimum thresholds are approached. Without resolution the defect risk includes pad breakout, reduced solder joint strength, or open circuits after thermal stress or mechanical handling. On 1 layer boards the issue mainly affects soldering reliability while on 2 layer boards it also impacts via integrity. Production teams routinely note that a quick confirmation or minor pad adjustment resolves the concern before panels are etched.

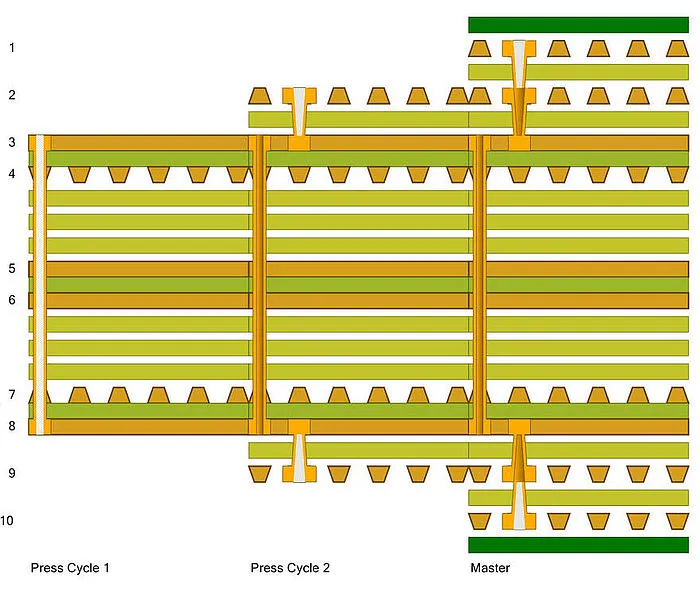

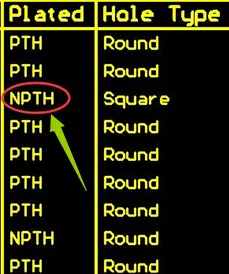

Plated vs Non Plated Hole Attribute Verification

Ambiguous hole attributes distinguishing plated from non-plated holes trigger repeated EQ especially on 2 layer FR4 PCB. The root cause is typically incomplete notation in the Excellon drill file or missing fabrication notes that fail to specify which holes require plating. Engineering review cross-checks drill attributes against the layer stackup and issues a clarification to avoid incorrect processing. If not clarified non-plated holes may receive copper or plated holes may remain open resulting in electrical shorts or assembly mismatches. Even on 1 layer FR4 PCB where plating is not applied the same file clarity prevents misinterpretation of through-hole features. Clear attribute labeling in the original files eliminates most of these queries at the CAM stage.

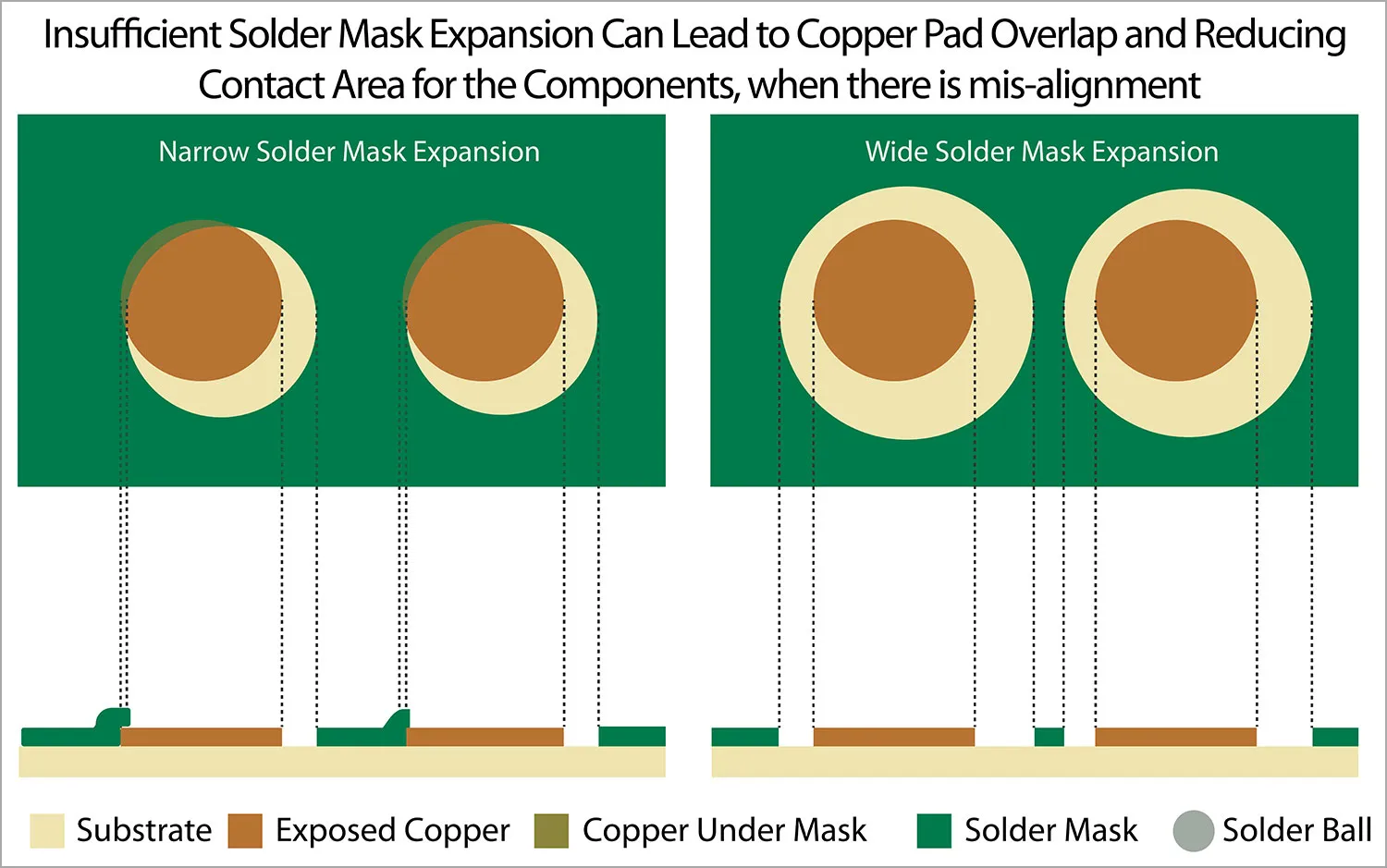

Solder Mask Clearance and Registration Alignment

Solder mask clearance and registration mismatches prompt many EQ across both 1 layer FR4 PCB and 2 layer FR4 PCB. These occur when the mask expansion or opening sizes in the design do not align with the manufacturer's standard application tolerances for FR4 substrates. The DFM review simulates mask-to-copper alignment and flags potential solder bridges or exposed trace risks. Unresolved problems can cause solder shorts during assembly or long-term corrosion from unprotected copper. Such issues are common when default CAD settings are retained without reference to actual production parameters. Confirming the preferred mask type and clearance values during review keeps the process on track.

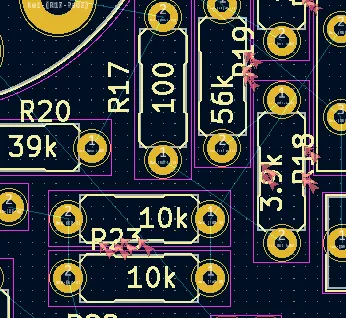

Silkscreen to Pad Clearance Compliance

Silkscreen legend placement that overlaps pads or violates clearance rules generates frequent clarification requests. The design often places text or markings too close to copper features without accounting for printing registration tolerances. CAM overlay analysis detects the conflict and requests adjustment or approval to protect solderable surfaces. If ignored the result can include ink contamination on pads, reduced solderability, or legibility problems during assembly. This EQ type appears consistently on both 1 layer and 2 layer FR4 boards in standard production runs. Providing silkscreen rules that match factory capabilities removes the need for last-minute changes.

Why These EQ Occur During File Review

These engineering queries surface during file review because Gerber, drill, and fabrication data must be converted into machine-specific instructions that match the factory's equipment capabilities for standard FR4 processing. Designers frequently apply general industry rules that do not account for the exact etching tolerances, drill wander, or lamination parameters used in daily production. The CAM engineering team performs a full DFM analysis that evaluates yield impact, panelization efficiency, and compliance with internal process windows. For 1 layer FR4 PCB and 2 layer FR4 PCB the review also verifies that copper distribution and hole definitions support reliable single- or double-sided flows. Most EQ originate from minor but critical oversights that are simple to correct once identified. The review process exists precisely to catch these before material is committed and production begins.

Practical Solutions and Best Practices to Minimize EQ

Designers can reduce engineering queries by strictly following the manufacturer's DFM guidelines for 1 layer and 2 layer FR4 PCB before file submission. Adding copper pours where needed on 2 layer boards helps achieve balanced distribution and limits warpage risk during lamination. Clearly labeling plated versus non-plated holes in the drill file and including a concise fabrication drawing with all tolerances and notes prevents attribute confusion. Running a self-check against the provided DFM rules for annular ring, mask clearance, and silkscreen spacing catches most issues internally. Specifying panelization preferences and fiducial locations at the design stage further streamlines the review. In our production experience these preparatory steps dramatically lower EQ volume and shorten the time from order to delivery.

Engaging the manufacturer early for any non-standard feature also ensures expectations remain aligned throughout the standard FR4 workflow.

Conclusion

Although 1 layer FR4 PCB and 2 layer FR4 PCB are the most common and straightforward configurations in electronics manufacturing they still benefit greatly from proactive attention to the details that trigger engineering queries. Understanding the typical DFM concerns around copper balance, annular rings, hole attributes, mask clearance, and silkscreen placement allows designers to submit cleaner files from the outset. Factory insights confirm that these small preventive steps translate into higher yields, shorter lead times, and more reliable finished boards. By treating EQ as an opportunity for clear communication rather than an obstacle, both design and production teams achieve smoother transitions from prototype to volume. Mastering these fundamentals remains essential as demand for basic FR4 boards continues to grow across all sectors.

FAQs

Q1: What is the most common reason for copper imbalance EQ on 2 layer FR4 PCB?

A1: Copper imbalance usually results from uneven routing density between the two layers without compensating copper pours on the lighter side. During DFM review the CAM system calculates area differences and flags the risk of warpage. Confirming the designer's balance intent allows the factory to proceed with confidence. Simple pour adjustments at the design stage eliminate this query in most cases.

Q2: Why does annular ring specification still matter for 1 layer FR4 PCB even without plating?

A2: Adequate annular ring ensures strong mechanical attachment and reliable solder joints on single-sided boards. Insufficient rings can cause pad lifting or cracking under soldering heat or mechanical stress. The engineering check verifies the dimension against production tolerances. Following recommended minimums from the DFM guide avoids clarification requests.

Q3: How can designers prevent solder mask related EQ on basic FR4 boards?

A3: Designers should use the manufacturer's specified mask expansion and clearance values rather than default CAD settings. These parameters are verified during CAM simulation for alignment accuracy. Matching the design to actual production tolerances prevents solder bridges or exposed copper. Early confirmation of mask type further reduces the need for queries.

Q4: Does providing panelization information help reduce EQ for 1 layer and 2 layer FR4 PCB?

A4: Yes, specifying routing method, v-score or tab locations, and fiducials allows the factory to optimize panel layout for yield and handling. Without these details the review team must request clarification to avoid inefficient panelization. Clear notes in the fabrication drawing streamline the process. This practice is especially valuable for volume orders of standard FR4 boards.

Q5: What is the quickest way to avoid hole attribute confusion in 2 layer FR4 files?

A5: Explicitly define plated and non-plated holes in both the drill file legend and fabrication drawing. Inconsistent or missing labels force the CAM engineer to pause for confirmation. Using the manufacturer's preferred format eliminates ambiguity. A short note on the drawing confirming plating requirements is usually sufficient.

References

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC, 2017

IPC-A-600 — Acceptability of Printed Boards. IPC, 2020

IPC-2221 — Generic Standard on Printed Board Design. IPC, 2018