Introduction

Augmented reality glasses represent a convergence of compact electronics, demanding precise power delivery to sustain immersive experiences. Power management ICs serve as the backbone, handling voltage regulation, conversion, and monitoring in space-constrained designs. Electric engineers face unique challenges here, balancing efficiency with thermal limits on small printed circuit boards. Battery life directly impacts user adoption, making selection of voltage regulators, DC-DC converters, battery chargers, and power monitoring circuits critical. This guide explores these components systematically, offering practical insights for integration into AR glasses prototypes and production boards. By prioritizing efficiency, engineers can optimize system performance without compromising form factor.

Understanding Power Management ICs in AR Glasses

Power management ICs encompass integrated circuits designed to control power flow from batteries to various subsystems in wearable devices. In AR glasses, these ICs must support multiple rails for processors, displays, sensors, and wireless modules, often from a single lithium-polymer cell. Voltage regulators maintain stable outputs despite load transients, while DC-DC converters step up or down voltages with minimal losses. Battery chargers ensure safe recharging cycles, and power monitoring tracks consumption for dynamic adjustments. Efficiency becomes paramount, as heat dissipation is limited by the device's slim profile and skin-contact constraints.

The relevance stems from AR glasses' always-on nature, where power draw fluctuates between idle sensor polling and high-resolution rendering. Poorly selected power management ICs lead to reduced battery autonomy, thermal throttling, or electromagnetic interference affecting display quality. Engineers must evaluate quiescent current, which dominates in low-duty cycles, alongside peak load capabilities. Standards like JEDEC J-STD-020 guide handling during assembly to prevent moisture-related failures in these sensitive components. Integration on PCBs requires careful consideration of pad layouts and via stitching to manage current densities effectively.

Core Technical Principles of Key Components

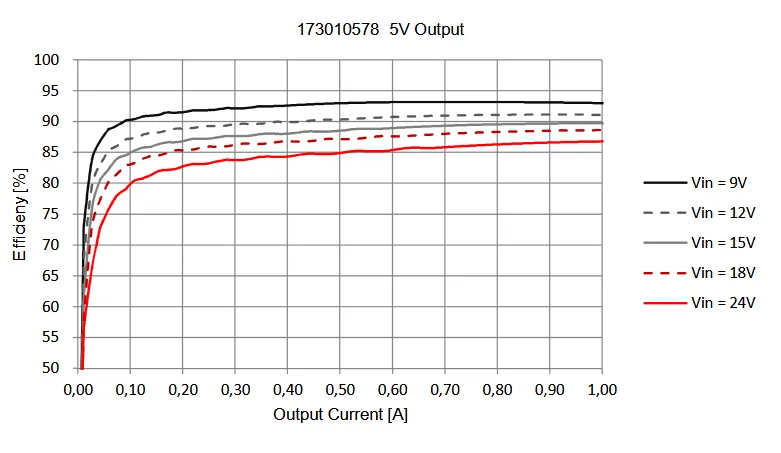

Voltage regulators, particularly low-dropout (LDO) types, provide clean, low-noise power for analog sections like image sensors in AR glasses. LDOs excel in applications needing high power supply rejection ratio (PSRR) to filter switching noise, though they trade off efficiency for simplicity. DC-DC converters, using buck or boost topologies, achieve higher efficiency by switching at high frequencies, reducing conduction losses. In AR designs, synchronous rectification minimizes body diode drops, crucial for extending runtime from compact batteries. Selection hinges on switching frequency versus inductor size, as higher frequencies shrink passives but increase gate drive losses.

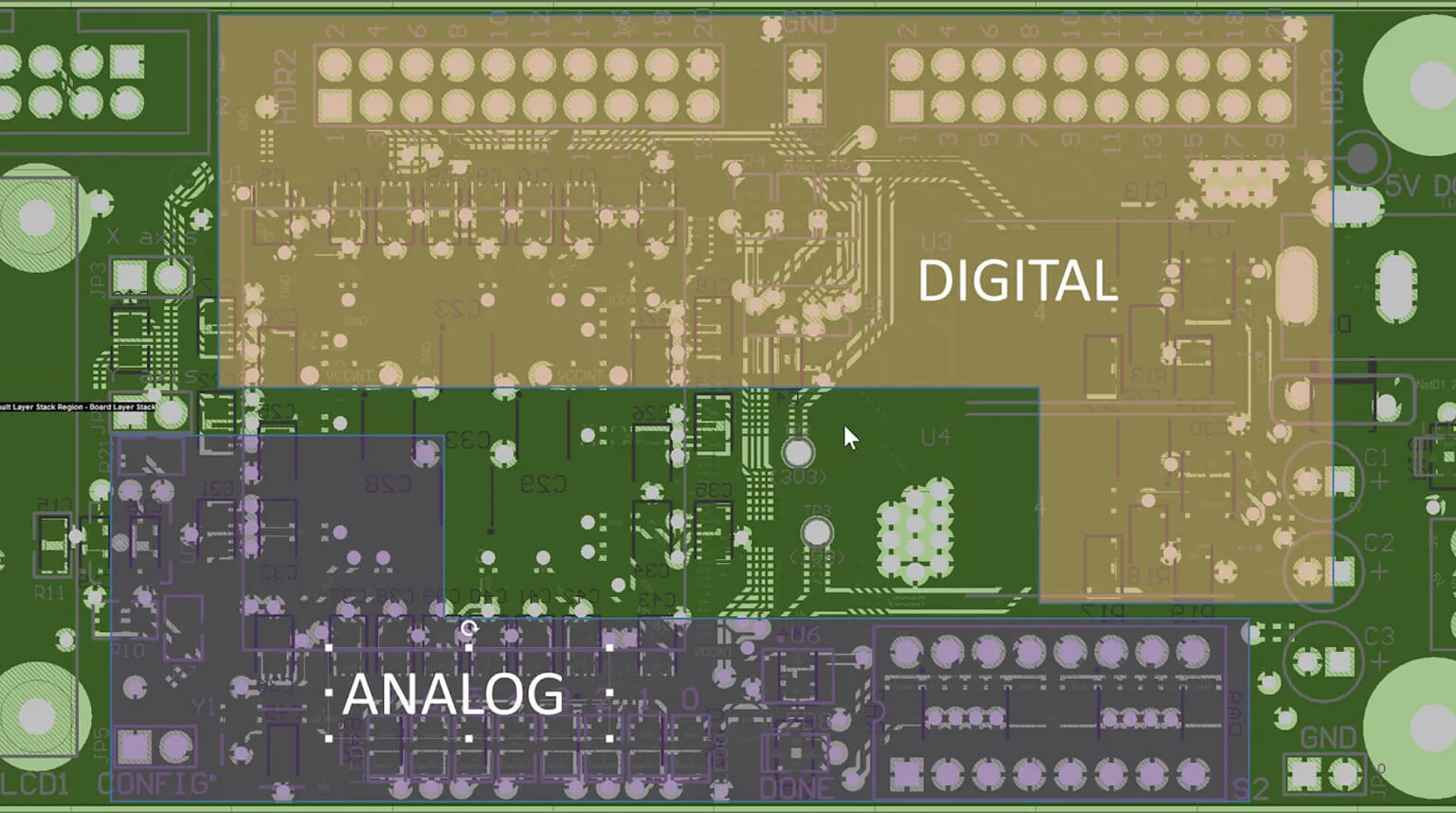

Battery chargers implement constant current/constant voltage (CC/CV) profiles to protect cells from overcharge, integrating protection against overvoltage and overtemperature. Power monitoring circuits, often via coulomb counters or shunt resistors, enable state-of-charge estimation and fuel gauging. Efficiency in these blocks relies on low offset sense amplifiers and adaptive algorithms that adjust based on load profiles. Engineers should model transient responses using SPICE simulations to predict ripple effects on sensitive nodes. PCB layout influences these principles, with ground planes splitting to isolate analog and digital domains per IPC guidelines.

Thermal management ties into these mechanisms, as power losses manifest as heat in dense AR boards. Junction temperatures must stay below ratings, often necessitating exposed pads for heat spreading. Converters with spread-spectrum modulation reduce EMI, aiding compliance in wearable bands.

Selection Criteria for Power Management ICs

Engineers selecting power management ICs for AR glasses prioritize efficiency across the load range, targeting minimal losses at both light and heavy loads. Quiescent current below microamp levels suits standby modes, while output current capacity matches subsystem peaks, like display drivers drawing hundreds of milliamps. Package options, such as wafer-level chip-scale (WLCSP) or quad flat no-lead (QFN), minimize footprint, but demand robust soldering per JEDEC standards to avoid delamination. Integration level varies: highly integrated PMICs combine regulators, converters, and chargers in one chip, simplifying board real estate but risking single-point failures.

Voltage regulator choice depends on noise budgets; LDOs suit audio or RF, while DC-DC handle digital cores. For battery chargers, support for USB power delivery or wireless input enhances versatility. Power monitoring accuracy, often within 1-5% error bands, informs software power gating. Evaluate bill-of-materials cost against performance, as passives like inductors dominate in switching designs. Datasheets reveal figures of merit like load regulation and line transient response, essential for AR's dynamic profiles.

Size constraints in AR glasses favor ICs with integrated features, reducing external components. Efficiency curves guide trade-offs, as boost converters enable single-cell operation for multi-rail systems.

Best Practices for PCB Integration

Integrate power management ICs on AR glasses PCBs by dedicating zones for power sections, away from high-speed signals to curb crosstalk. Use wide traces or copper pours for high-current paths, calculating widths via IPC-2221 formulas to limit voltage drops. Decoupling capacitors, placed within millimeters of pins, stabilize inputs and filter outputs, with values tuned to loop bandwidth. For DC-DC converters, position inductors near switches, orienting them to minimize magnetic coupling. Ground vias surround ICs, tying to solid planes for return paths.

Battery charger placement near the cell minimizes trace resistance, incorporating thermistors for temperature compensation. Power monitoring shunts require Kelvin connections to preserve accuracy. Thermal vias under exposed pads wick heat to inner layers or chassis. Solder paste volume and reflow profiles follow J-STD-020 to ensure void-free joints, preventing hotspots. Prototype testing involves scopes for ripple and thermal cameras for hotspots.

Firmware calibration of power monitoring enhances precision, adjusting for aging effects. Compliance testing verifies efficiency under real workloads, iterating layouts as needed.

Troubleshooting Common Power Issues in AR Designs

Overheating often traces to inadequate airflow or undersized heatsinking in enclosed AR frames, addressed by selecting low-RDS(on) FETs in converters. Excessive ripple corrupts sensor data, fixed by adding LC filters or phase interleaving multiple rails. Battery runtime shortfalls stem from inaccurate fuel gauges, resolved via characterization over discharge cycles. Voltage droops during transients signal insufficient phase margin, tuned via compensation networks.

EMI failures arise from poor shielding; ferrite beads and snubbers suppress conducted noise. Debug with current probes to isolate high-draw subsystems. PCB warpage post-assembly stresses PMIC solder joints, mitigated by balanced copper distribution per IPC standards. Systematic logging of power states aids root-cause analysis.

Conclusion

Power management ICs define the viability of AR glasses, demanding a holistic approach to voltage regulators, DC-DC converters, battery chargers, and power monitoring. Efficiency drives selection, intertwined with PCB integration practices for optimal performance. Engineers benefit from standards-guided designs, ensuring reliability in compact form factors. Prioritizing these elements extends battery life and enhances user experience. Future iterations will leverage even denser integration, but fundamentals remain key.

FAQs

Q1: What role do voltage regulators play in power management ICs for AR glasses?

A1: Voltage regulators stabilize supply rails for noise-sensitive components like displays and IMUs in AR glasses. LDO types offer superior PSRR for analog circuits, while switching variants prioritize efficiency. Selection focuses on dropout voltage and thermal resistance to fit compact PCBs. Proper decoupling prevents oscillations, ensuring clean power delivery.

Q2: How do DC-DC converters improve efficiency in AR wearable power systems?

A2: DC-DC converters achieve high efficiency through pulse-width modulation, outperforming linear regulators in battery-powered AR glasses. Buck topologies step down voltages for processors, boosts handle display backlights. Engineers optimize inductor selection and switching frequency to balance size and EMI. This extends runtime significantly under varying loads.

Q3: Why is power monitoring essential in battery chargers for AR devices?

A3: Power monitoring in battery chargers tracks charge cycles and state-of-health, preventing over-discharge in AR glasses. Integrated coulomb counters provide real-time data for software alerts. Accuracy relies on low-offset sensing, aiding predictive maintenance. This feature optimizes charging efficiency and prolongs cell life in wearables.

Q4: What factors affect efficiency of power management ICs in AR glasses?

A4: Efficiency in power management ICs depends on load conditions, quiescent current, and topology in AR glasses. Synchronous designs reduce losses, while adaptive modes handle transients. PCB parasitics influence overall performance, requiring minimized loop areas. Testing across profiles ensures peak operation without thermal issues.

References

JEDEC J-STD-020E — Moisture/Reflow Sensitivity Classification. JEDEC, 2014

IPC-2221B — Generic Standard on Printed Board Design. IPC, 2012

IPC-A-600K — Acceptability of Printed Boards. IPC, 2020