Introduction

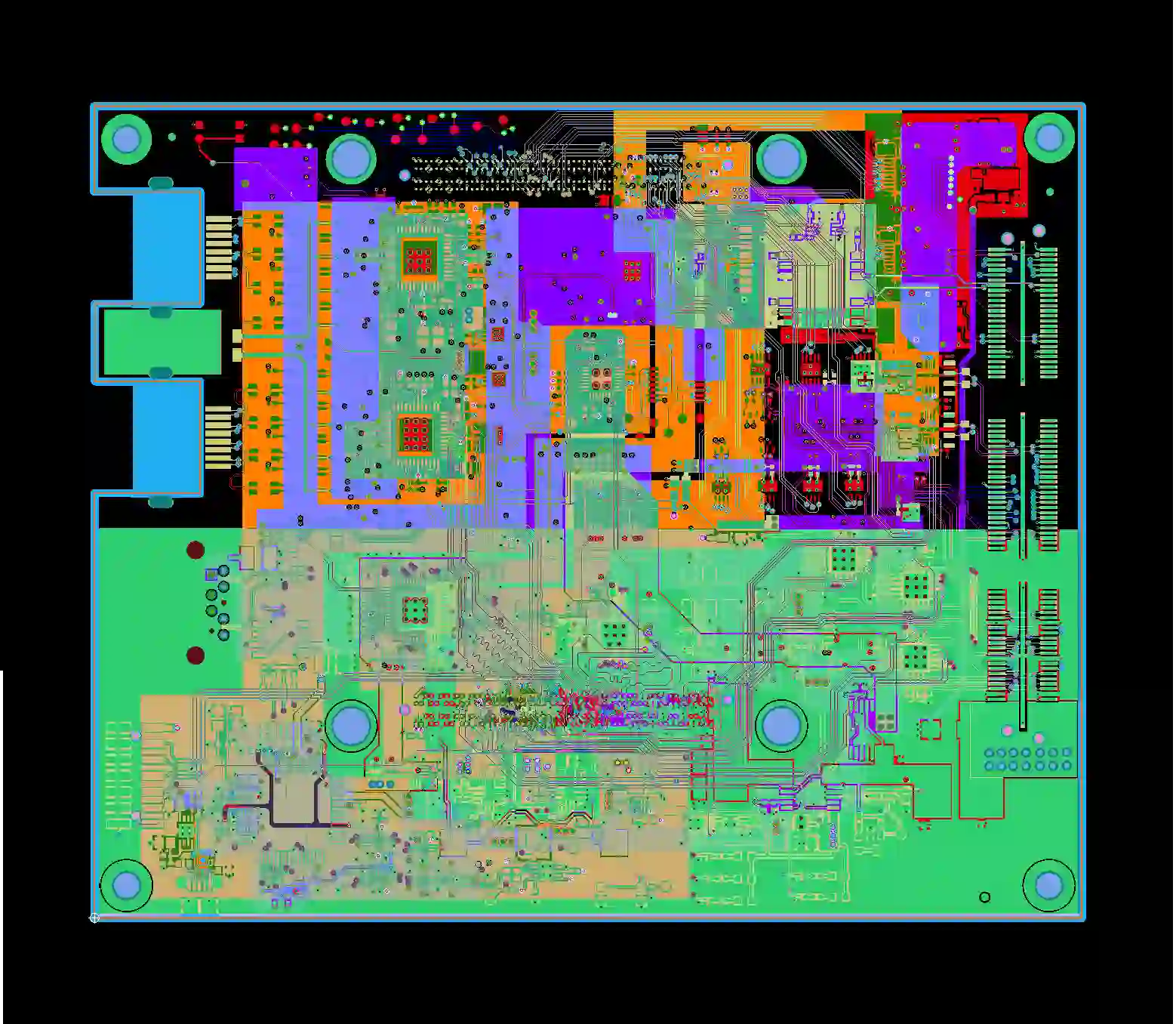

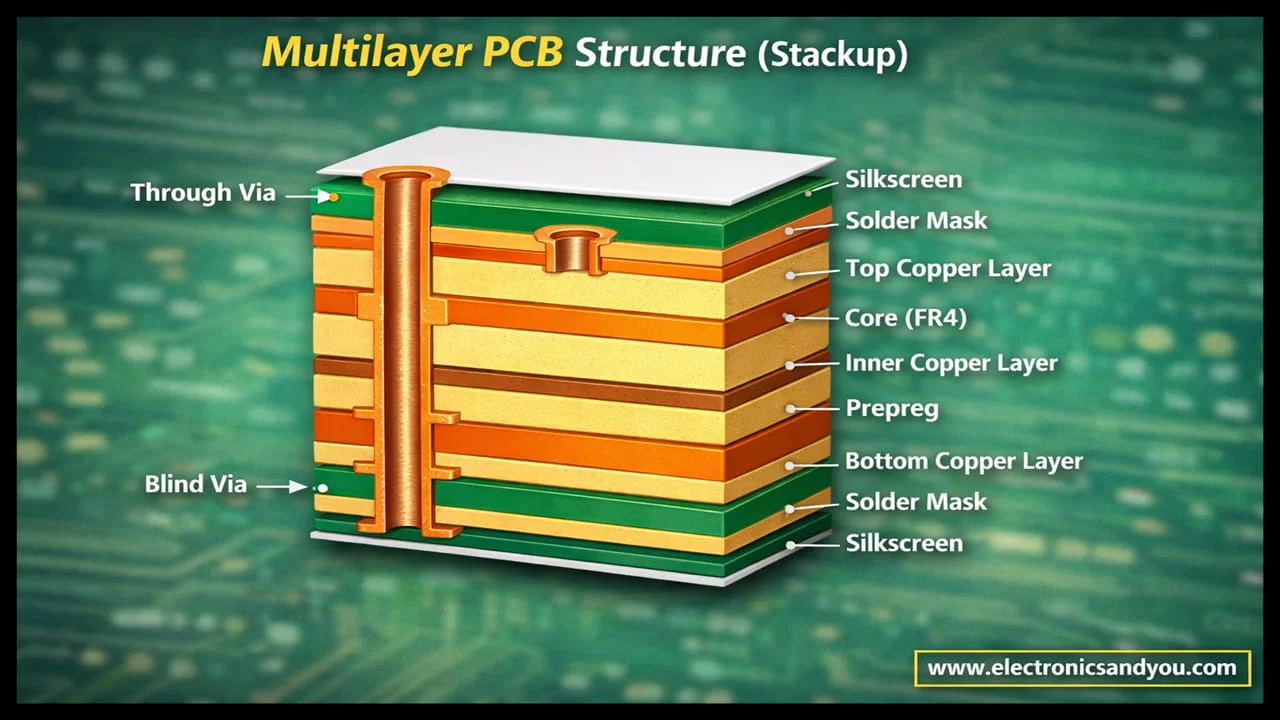

In practical production environments, multilayer FR4 PCB supports complex electronic systems where signal integrity and power stability are critical. Compared to simpler board types, multilayer structures involve more process steps such as sequential lamination and precision drilling. These added complexities increase the likelihood of engineering queries during DFM review. Even small inconsistencies in stackup symmetry or via design can lead to manufacturing risks. Addressing these concerns early ensures smoother production and higher yield.

What Are Engineering Queries and Why They Matter

Engineering queries are clarification requests raised by manufacturers when design data contains uncertainties that may affect production quality. In multilayer PCB fabrication, these queries often focus on structural balance, drilling feasibility, and electrical performance. Because multilayer boards rely on tight process tolerances, unresolved issues can quickly lead to defects such as warpage or poor signal integrity. EQ serves as a communication bridge between design intent and real manufacturing capability. Timely responses help maintain schedule and ensure consistent product performance.

Common EQ Types in Multilayer FR4 PCB

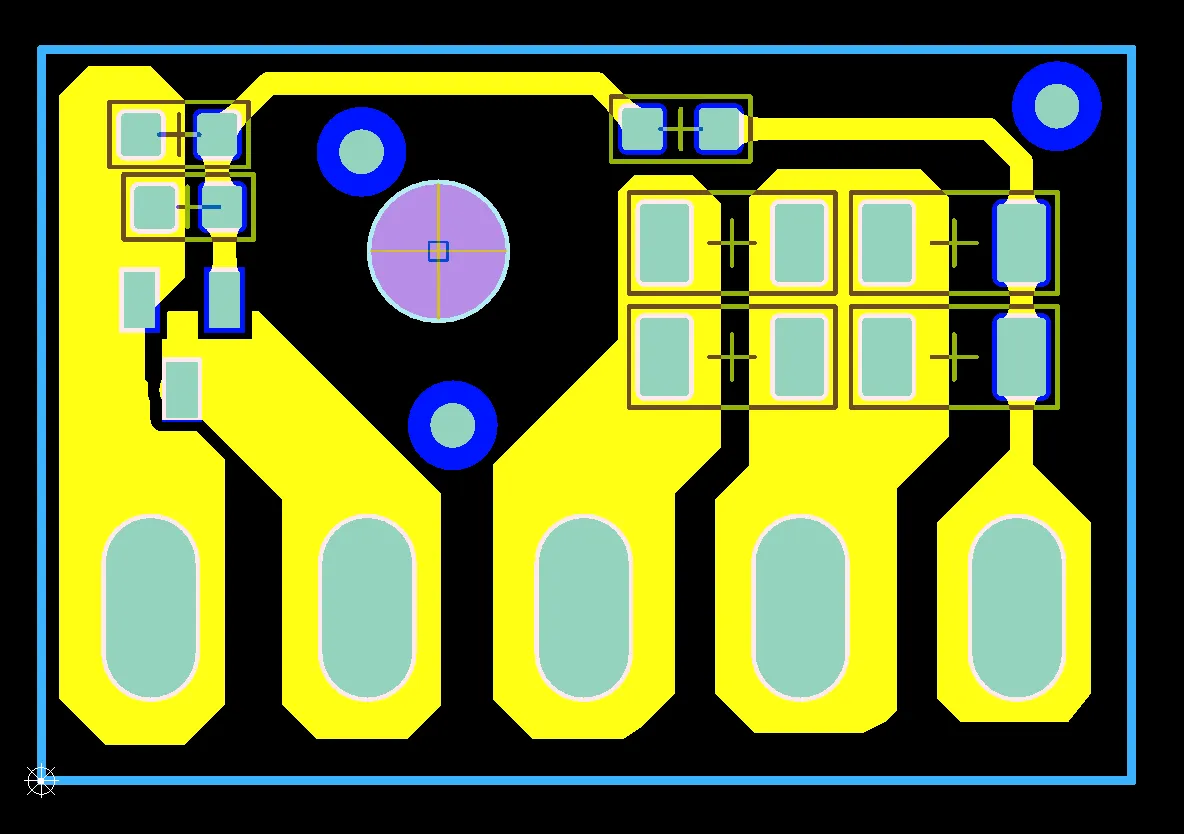

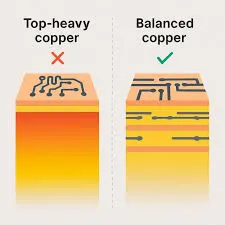

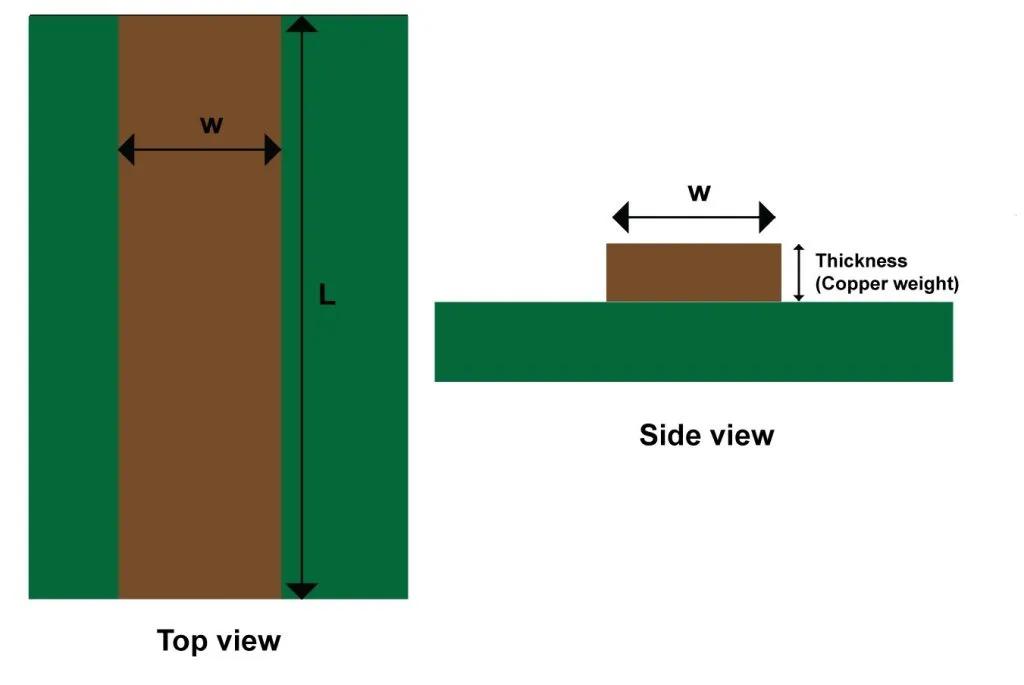

Copper imbalance across layers is one of the most common issues identified during engineering review. It usually occurs when routing density or copper pours are unevenly distributed throughout the stackup. CAM analysis evaluates copper ratios on each layer and flags asymmetry that may cause warpage. If not corrected, the board may deform during lamination or soldering processes. Ensuring symmetrical copper distribution improves mechanical stability and reduces production risk.

Via aspect ratio and plating uniformity are also frequent concerns in multilayer designs. As board thickness increases, maintaining consistent copper deposition inside vias becomes more challenging. Engineering review tools analyze the relationship between hole depth and diameter to ensure it stays within process limits. If the ratio is too high, defects such as voids or cracks may occur. Proper via design and clear plating specifications help avoid these issues.

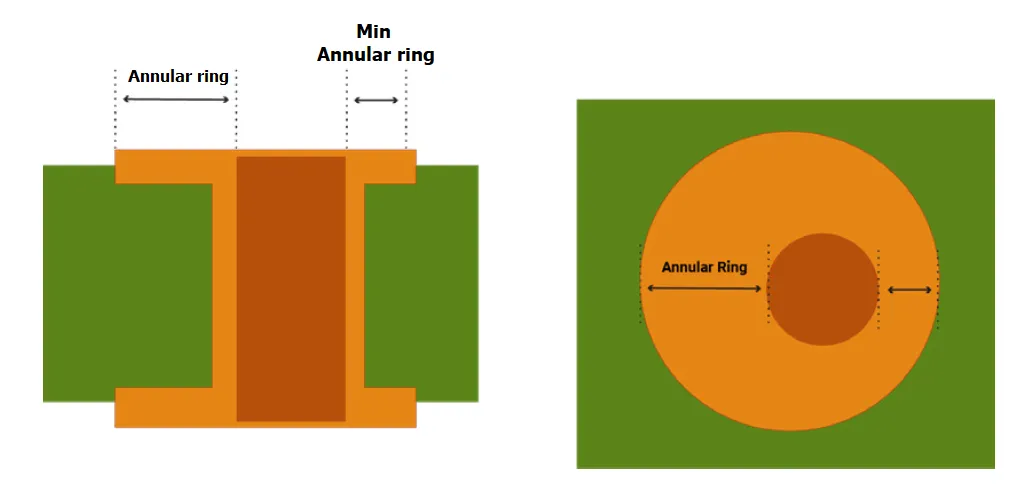

Layer-to-layer registration tolerance is another key source of engineering queries. Misalignment can result from cumulative shifts during multiple lamination cycles. DFM simulation evaluates how well all layers align within acceptable tolerances. Poor registration may lead to reduced annular rings or electrical shorts. Including proper fiducials and realistic spacing rules minimizes this risk.

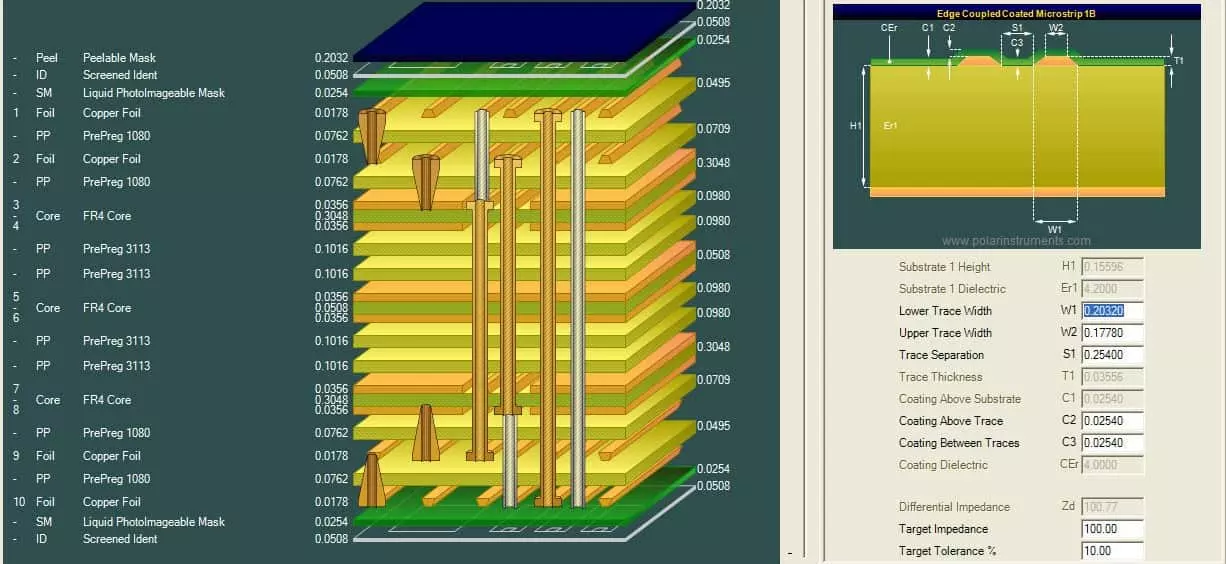

Impedance control inconsistencies often trigger clarification requests during review. These occur when design parameters do not match the manufacturer’s material properties or stackup configurations. Engineering teams compare requested impedance values with real production capabilities. Any mismatch can impact signal performance and lead to failure in testing. Accurate stackup definition ensures reliable impedance control.

Annular ring sizing issues are also commonly identified in multilayer PCB designs. These problems arise when pad dimensions do not account for drilling tolerances and alignment variation. CAM systems calculate effective annular ring values after processing adjustments. Insufficient margins may cause pad breakout or weak connections. Designing with layer-specific pad rules helps maintain reliability.

Why These Issues Occur During DFM Review

Engineering queries arise because design files must be translated into precise manufacturing instructions. Designers often apply general rules that do not fully reflect real production constraints. Multilayer fabrication involves cumulative effects such as drill deviation and material variation. DFM analysis evaluates these risks before production begins. Identifying issues at this stage prevents defects and costly delays.

Best Practices to Reduce Engineering Queries

Reducing engineering queries starts with aligning design data to manufacturer capabilities. Maintaining copper symmetry across layers helps control warpage. Clearly defining via structures and plating requirements avoids ambiguity. Providing accurate stackup details ensures impedance consistency. Running internal DFM checks before submission can catch most issues early. These practices significantly improve first-pass success rates.

Conclusion

Multilayer FR4 PCB designs introduce additional complexity that often leads to engineering queries during manufacturing review. By understanding common DFM concerns such as copper balance, via plating, and layer alignment, designers can improve design quality from the start. Early optimization reduces production risks and enhances overall reliability. Treating EQ as part of the design improvement process leads to better collaboration and more efficient manufacturing outcomes.

FAQs

Q1: Why is copper balance important in multilayer PCB?

A1: Copper imbalance can cause board warpage during lamination and soldering. Symmetrical distribution ensures mechanical stability and consistent flatness. It also reduces stress on vias and components.

Q2: What causes via plating issues?

A2: High aspect ratios make it difficult to achieve uniform plating inside vias. This can lead to voids or weak connections. Proper via sizing and plating specs help prevent these problems.

Q3: How can layer registration issues be avoided?

A3: Designers should follow manufacturer tolerance guidelines and include proper fiducials. Adequate spacing and realistic alignment assumptions improve accuracy. This reduces the risk of misalignment during lamination.

Q4: Why does impedance mismatch happen?

A4: Impedance mismatch occurs when design parameters do not align with actual material properties. Differences in dielectric constants or stackup can affect signal performance. Confirming these values with the manufacturer solves the issue.

Q5: How to prevent annular ring problems?

A5: Use pad sizes that consider drilling and alignment tolerances. Avoid applying the same rules across all layers. This ensures sufficient annular ring after manufacturing adjustments.

References

IPC-6012E — Qualification and Performance Specification for Rigid Printed Boards. IPC, 2017

IPC-A-600 — Acceptability of Printed Boards. IPC, 2020

IPC-2221 — Generic Standard on Printed Board Design. IPC, 2018