Introduction

Railway signaling systems rely on printed circuit boards (PCBs) to process critical data for safe train operations. These PCBs must withstand harsh environments while ensuring fail-safe performance to prevent accidents. EN 50129 establishes the framework for safety-related electronic systems in railway signaling, demanding rigorous design and verification processes. Compliance with EN 50129 PCB standards directly impacts system reliability and regulatory approval. Electric engineers designing these PCBs need to integrate safety from the initial concept through to deployment. This guide explores the core requirements and practical approaches for achieving EN 50129 compliance in railway standards PCB development.

What Is EN 50129 and Why It Matters for Railway Signaling PCBs

EN 50129 defines safety requirements for electronic systems used in railway communication, signaling, and processing. It applies to subsystems and equipment that perform safety functions, specifying how to demonstrate safety integrity throughout the product lifecycle. This CENELEC standard builds on broader functional safety principles, assigning Safety Integrity Levels (SIL) from SIL 0 to SIL 4 based on risk reduction needs. For PCBs, EN 50129 PCB compliance ensures hardware contributes to overall system safety by minimizing failure probabilities. Without adherence, signaling systems risk non-compliance, leading to project delays or safety certification failures. Engineers must prioritize these railway standards PCB guidelines to support mission-critical applications like trackside controllers and interlocking systems.

The relevance stems from the high stakes in railway operations, where a single PCB failure could cascade into catastrophic events. EN 50129 mandates a structured safety case, documenting evidence of fault tolerance and diagnostic coverage. This matters for PCB designers because signaling electronics face extreme vibrations, temperature swings, and electromagnetic interference. Proper design reduces common-mode failures and enhances diagnostic capabilities. Ultimately, EN 50129 integration fosters trust in PCB certification railway processes, enabling seamless integration into larger signaling networks.

Safety Integrity Levels (SIL) in EN 50129

Safety Integrity Levels quantify the reliability required for safety functions under EN 50129. SIL 1 offers basic fault tolerance, while SIL 4 demands the highest probabilistic safety targets, often exceeding 10^-9 dangerous failure probability per hour. PCB designs for higher SIL applications incorporate redundancy, such as dual power rails or duplicated signal paths, to achieve necessary diagnostic coverage. Engineers calculate SIL targets during hazard analysis, ensuring hardware architecture aligns with system-level goals. This level-based approach guides material choices and layout strategies for railway standards PCB reliability.

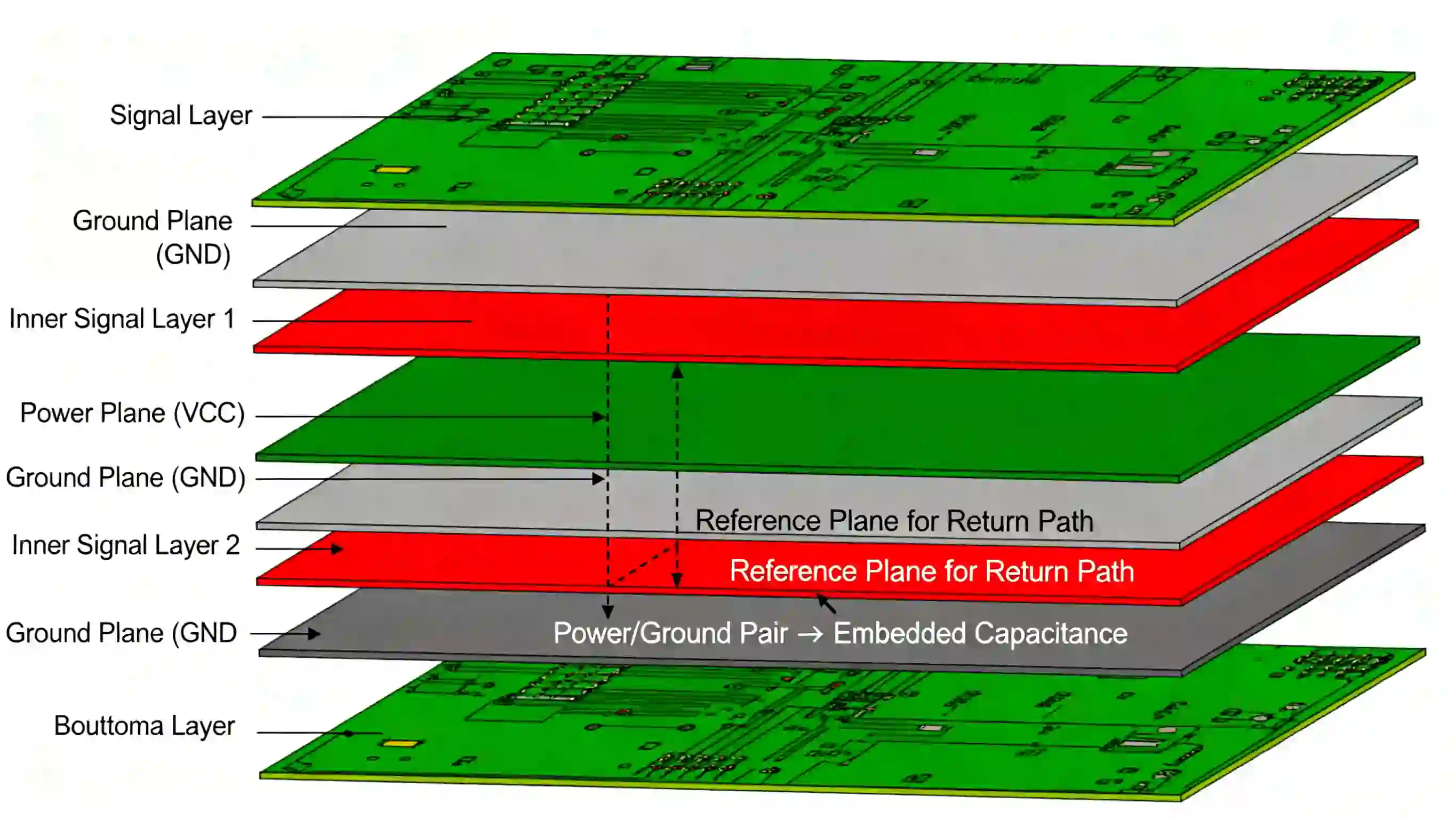

EN 50129 links SIL assignment to the safety lifecycle, from concept to decommissioning. For PCBs, this means verifying that random hardware failures remain below thresholds through proven components and stress testing. Architectural constraints, like 1oo2D (one out of two with diagnostics), influence multilayer stackups and partitioning. Failure to meet SIL via poor design compromises the entire signaling chain. Thus, electric engineers use SIL metrics to prioritize fault-avoidance techniques early in the design phase.

Key Technical Principles for PCB Design Under EN 50129

EN 50129 emphasizes a safety lifecycle covering specification, design, implementation, verification, and validation. For PCBs, this translates to systematic risk assessment and evidence collection in a safety case report. Hardware must demonstrate both systematic and random fault management, with techniques like diversity in components to avoid common failures. Fault Tree Analysis and Failure Modes and Effects Analysis (FMEA) identify single-point failures in PCB layouts. These principles ensure CENELEC standards alignment, particularly for signaling where downtime is unacceptable.

Hardware safety integrity requires probabilistic calculations for failure rates, often referencing IEC 61508 for methodologies. PCBs contribute through low failure rate materials and robust interconnections. Diagnostic coverage, such as built-in self-tests via boundary scan, detects latent faults before they propagate. Environmental robustness addresses mechanical stresses per railway conditions, using reinforced vias and anchor points. Compliance verification involves independent assessment, confirming design meets declared SIL.

EN 50129 mandates independence levels for development, verification, and assessment, scaling with SIL. Higher SIL PCBs demand separation of safety-critical and non-critical sections via guard traces or moats. Insulation coordination prevents arc-over under high voltages, with creepage and clearance distances calculated per application. These mechanisms collectively lower the Probability of Failure on Demand (PFD) or Failure per Hour (PFH).

PCB Design Best Practices for EN 50129 Compliance

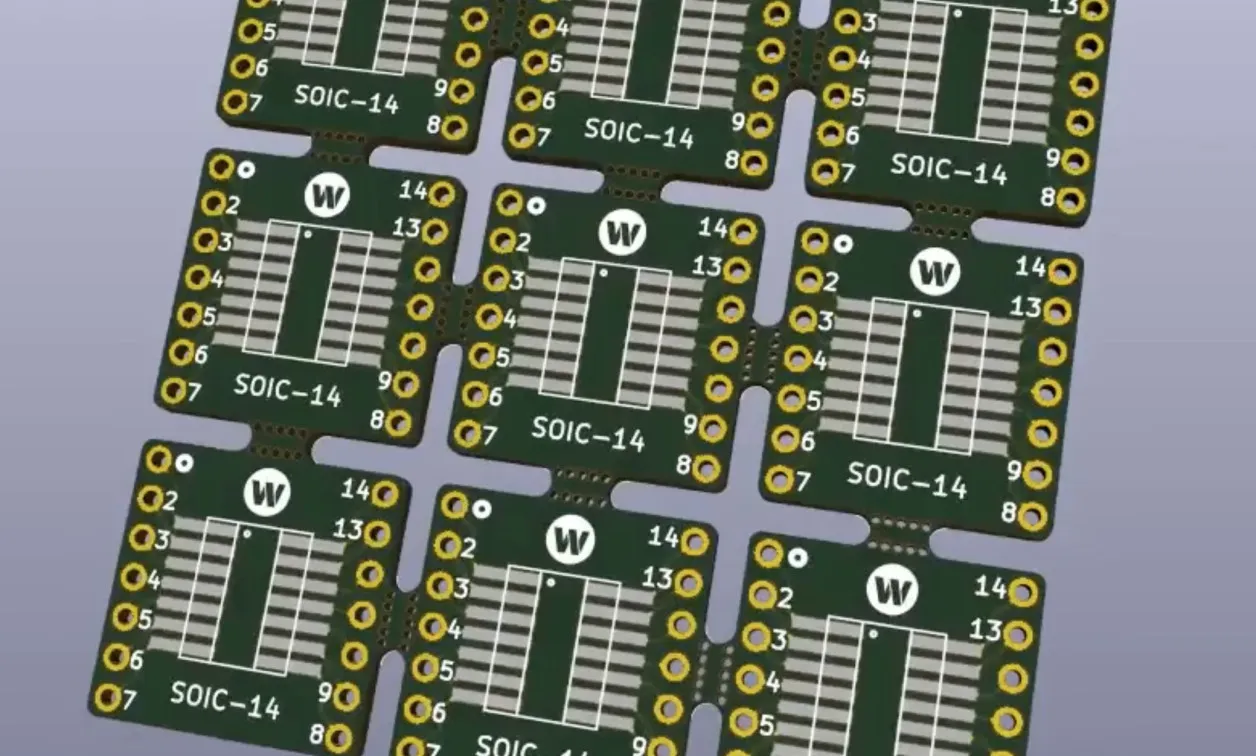

Start with a thorough requirements capture, mapping PCB functions to SIL targets. Use multilayer boards for signal integrity and power distribution, grouping safety-critical logic to minimize crosstalk. Track widths must handle peak currents without electromigration, while spacings ensure voltage withstand under humidity. Partitioning isolates analog, digital, and power domains, reducing noise coupling. FMEA during schematic review flags potential shorts or opens early.

Material selection focuses on high glass transition temperature laminates for thermal stability, avoiding delamination in vibration-heavy environments. Controlled impedance traces maintain signal quality over long runs common in signaling PCBs. Incorporate redundancy like parallel vias and duplicated grounds for fault tolerance. Thermal vias and copper pours manage heat from power components, preventing hotspots that degrade reliability.

Electromagnetic compatibility demands ground planes and filtering to suppress emissions. Shielding cans over sensitive areas block interference from trackside sources. Mechanical design includes edge bevels and mounting holes positioned for shock absorption. Solder mask and silkscreen enhance durability against abrasion.

Assembly processes align with IPC-6012 for qualification, ensuring vias and pads meet performance specs. Post-fabrication, environmental testing simulates railway conditions, verifying warpage and solder joint integrity. Traceability from design to production supports safety case documentation.

For higher SIL, employ diverse architectures, such as mixing FPGA and ASIC for logic. Built-in diagnostics, like CRC checks on data buses, boost coverage above 90 percent. Iterative design reviews with cross-functional teams refine compliance.

The Certification Process for Railway PCBs

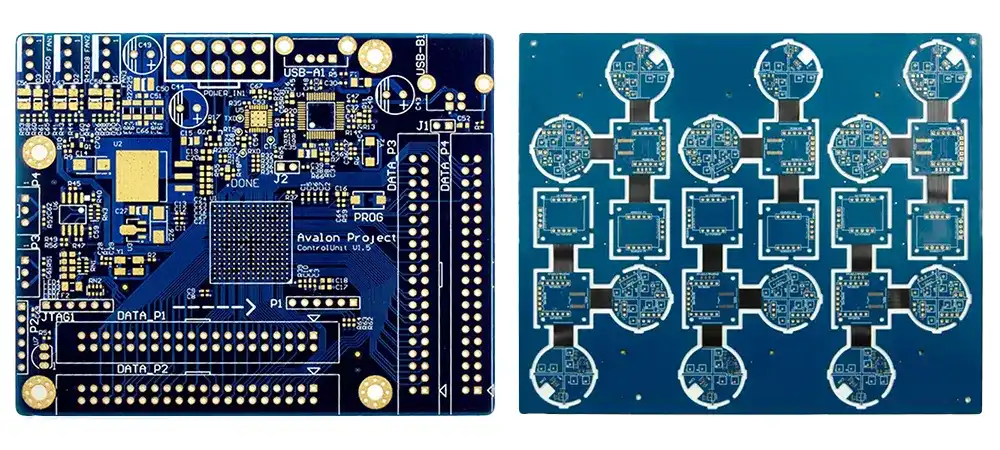

Achieving PCB certification railway approval begins with a safety plan outlining lifecycle activities. Independent assessors review the safety case, including hardware schematics and FMEA results. Prototypes undergo qualification tests per IPC standards, confirming electrical, thermal, and mechanical performance. SIL verification involves software-hardware integration tests demonstrating fault detection.

Documentation includes bill of materials with failure rate data, layout files, and test reports. Third-party notification bodies audit processes for EN 50129 PCB compliance. Revisions require re-assessment if changes affect safety functions. This rigorous path ensures PCBs meet CENELEC standards for deployment.

Conclusion

EN 50129 sets the benchmark for railway signaling PCB safety, demanding integrated design for fault tolerance and reliability. Key practices like redundancy, FMEA, and lifecycle management directly support SIL targets. Electric engineers benefit from early standards alignment, reducing risks and certification hurdles. Robust PCBs enable dependable signaling systems, safeguarding passengers and operations. Prioritizing these railway standards PCB principles yields compliant, long-life designs.

FAQs

Q1: What does EN 50129 PCB compliance entail for railway signaling?

A1: EN 50129 PCB compliance requires demonstrating hardware safety integrity through lifecycle processes, FMEA, and SIL-aligned architecture. Designers implement redundancy and diagnostics to manage faults, with verification via testing and independent assessment. This ensures PCBs contribute to system-level safety in harsh railway environments, aligning with CENELEC standards for reliable operation.

Q2: How does IEC 61508 relate to railway standards PCB design?

A2: IEC 61508 provides the functional safety foundation for EN 50129, defining SIL metrics and probabilistic failure targets. For PCBs, it guides hardware fault modeling and diagnostic coverage calculations. Railway engineers apply its principles to select low-failure-rate components and architectures, ensuring compliance during certification. This integration streamlines PCB certification railway processes.

Q3: What are common PCB design challenges in achieving CENELEC standards compliance?

A3: Challenges include balancing density with creepage distances, managing thermal loads under vibration, and verifying EMC in signaling systems. Solutions involve multilayer partitioning, high-reliability materials, and rigorous FMEA. Testing per IPC guidelines confirms robustness, helping engineers meet EN 50129 requirements without compromising performance.

Q4: Why is redundancy critical for high-SIL railway PCBs?

A4: Redundancy in high-SIL PCBs, like 1oo2 configurations, detects and mitigates single failures, achieving required PFD or PFH. It diversifies paths for safety functions, enhancing diagnostic coverage per EN 50129. This practice is essential for railway standards PCB reliability, preventing unsafe states in signaling applications.

References

IEC 61508 - Functional safety of electrical/electronic/programmable electronic safety-related systems. IEC, 2010

IPC-6012E - Qualification and Performance Specification for Rigid Printed Boards. IPC, 2015

IPC-A-600K - Acceptability of Printed Boards. IPC, 2020

J-STD-001H - Requirements for Soldered Electrical and Electronic Assemblies. IPC, 2018