How DRAM Stores and Reads Data

Technical overview of single-transistor DRAM cell operation—store, write, read and refresh—plus practical notes and a DRAM vs SRAM comparison on density, speed, and cost.

Technical overview of single-transistor DRAM cell operation—store, write, read and refresh—plus practical notes and a DRAM vs SRAM comparison on density, speed, and cost.

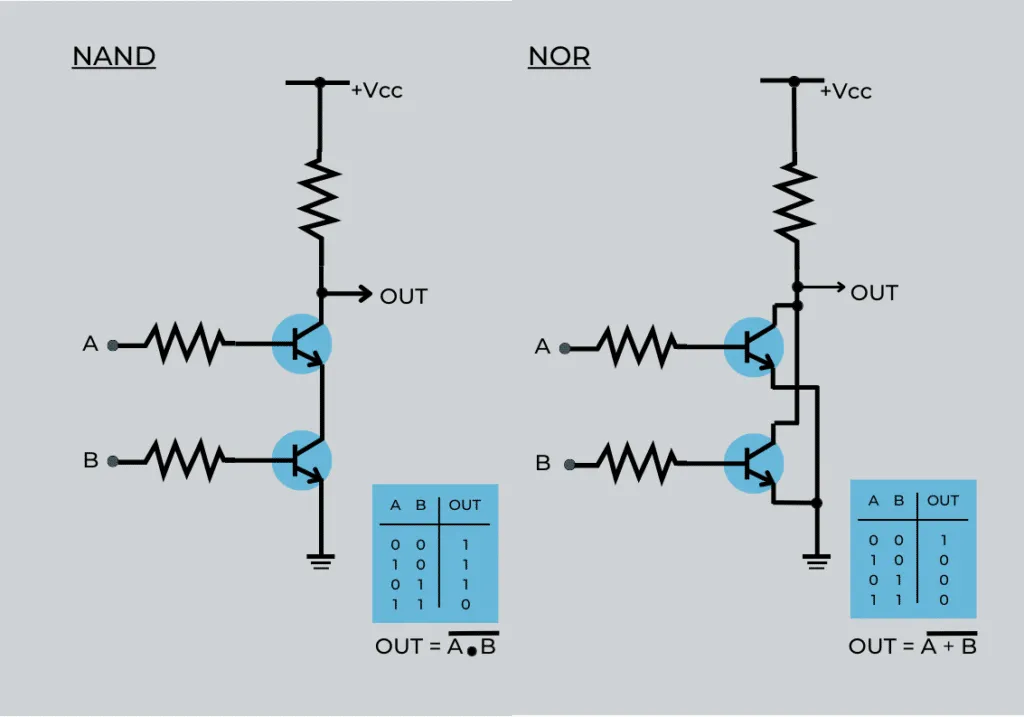

Technical guide to flash memory interfaces and reference circuits, covering NAND flash operation, SPI/NOR wiring, debugging practices, and a concise 3D XPoint overview.

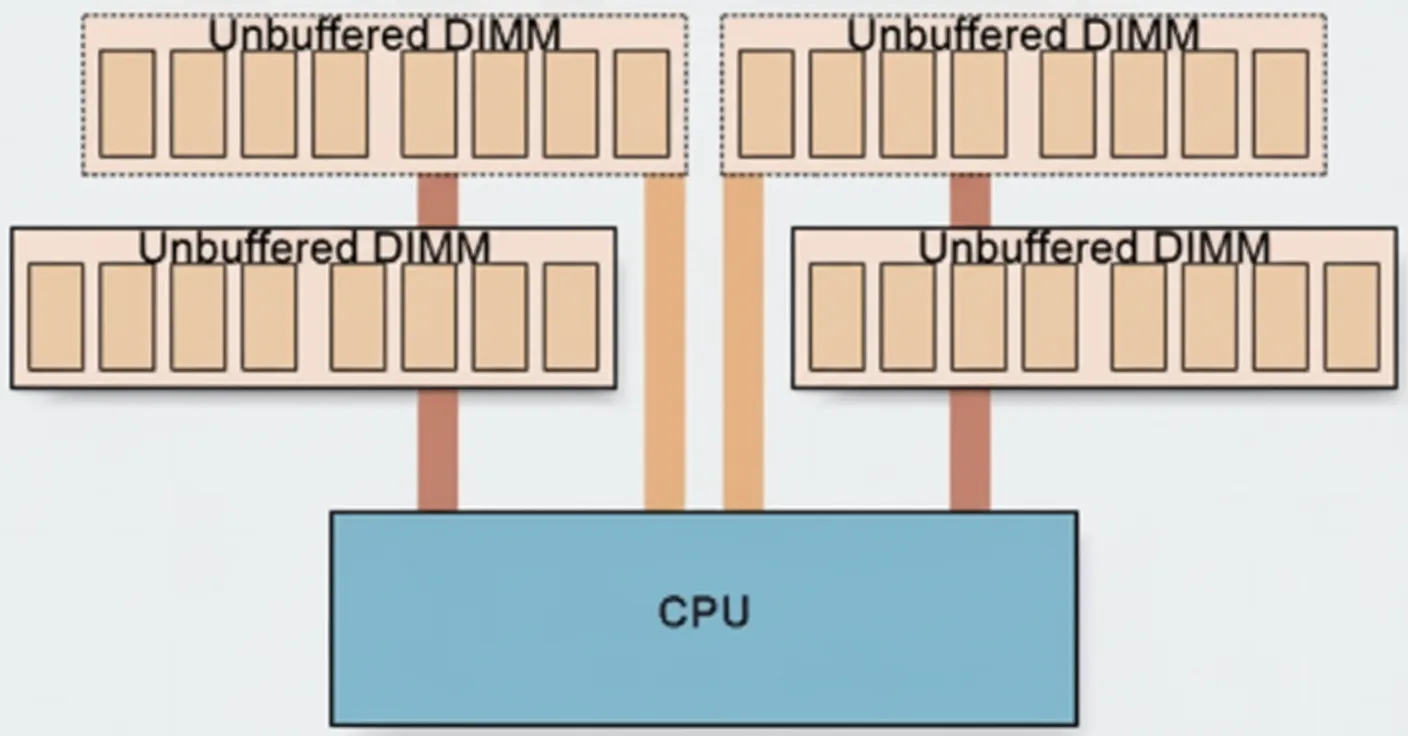

Technical overview of DDR4 advancements, highlighting POD termination, bank-group architecture and point-to-point topology compared with DDR3 for higher speed and lower voltage.

Device teardown finds SK Hynix parts: H58GG6MK6GX037 12GB LPDDR5 DRAM and HN8T25DEHKX077 512GB UFS 3.1, both marked CS and likely entering production around 2021.

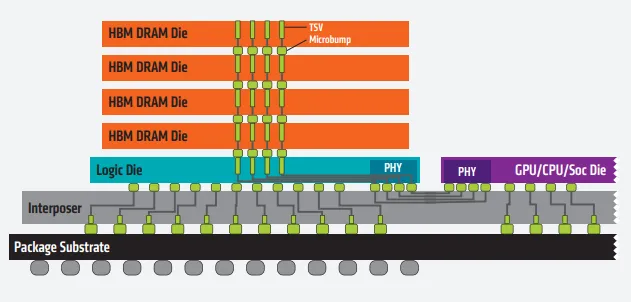

Technical overview of DDR DRAM and HBM standards to guide SoC designers in selecting memory technologies for performance, power, and bandwidth trade-offs.

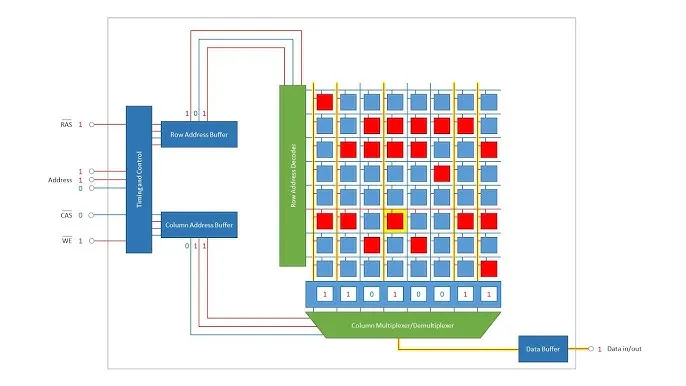

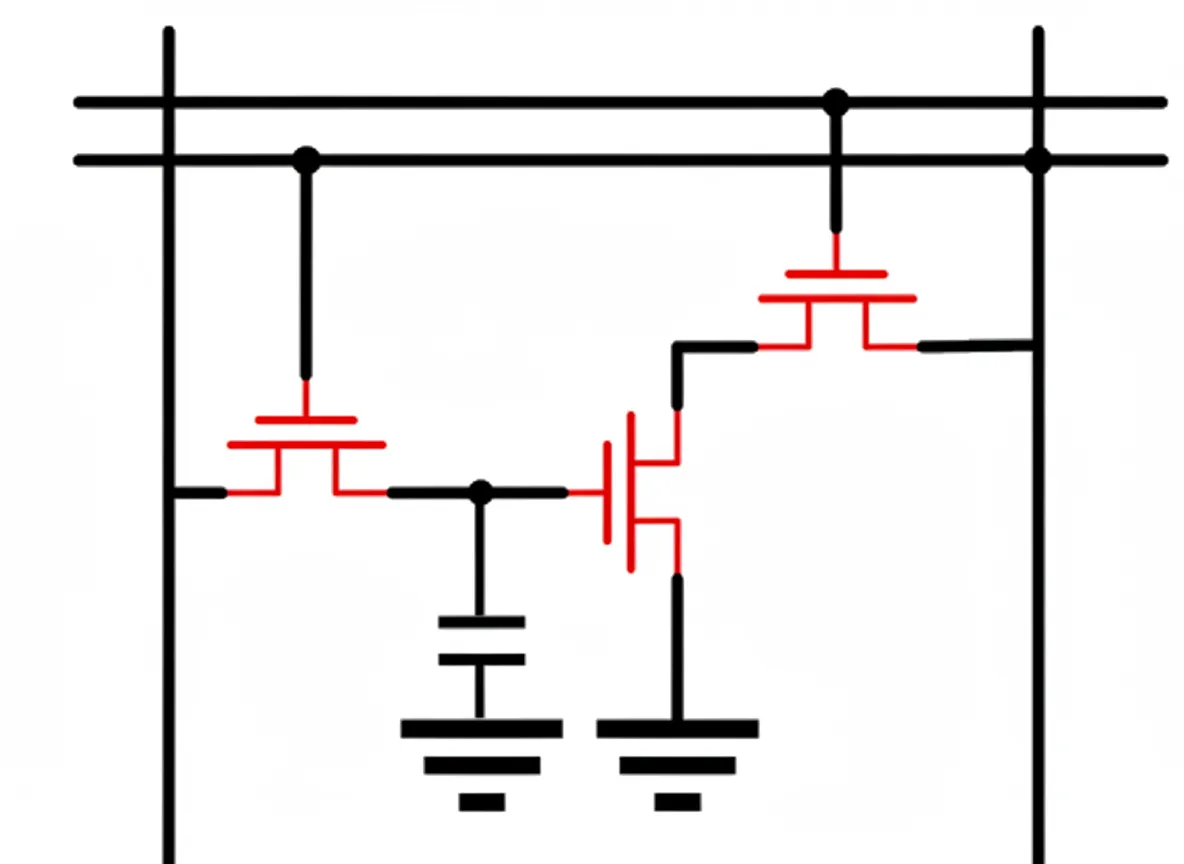

Overview of DRAM types, storage cell structure, and data handling, covering SDRAM/DDR generations, capacitor–transistor cells, and refresh cycles.

Comparison of DDR4 3200 and DDR4 3600 memory: frequency, theoretical bandwidth, performance impact across workloads, and implications of mixing modules for stability.

Analysis of AI storage requirements for large models, detailing Huawei's OceanStor A310 and FusionCube A3000 solutions, scalability, performance, and deployment challenges.

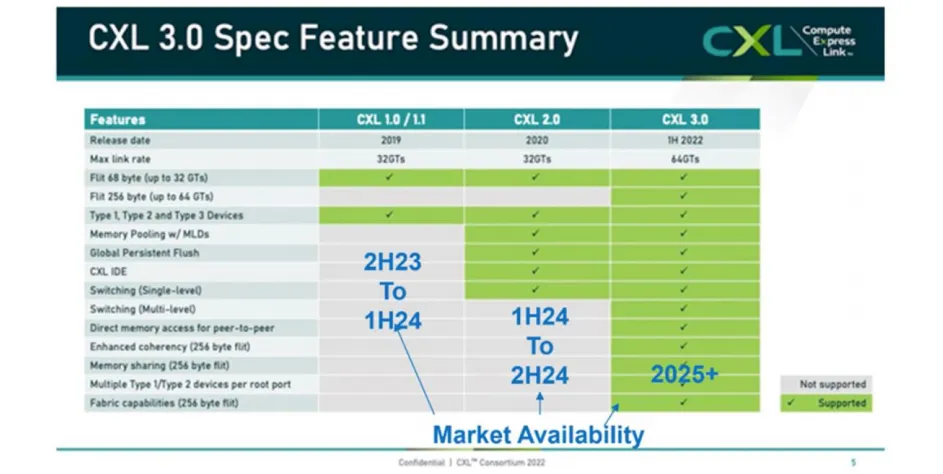

Technical overview of Rambus product portfolio, DDR5 vs DDR4 performance gains, and CXL adoption, covering memory interface chips, IP, security, and acquisitions.

Technical comparison of NAND Flash and NOR Flash memory covering architecture, interfaces, performance, endurance, SPI NAND, applications, and guidance for selecting flash.

Technical overview of OTP and MTP non-volatile memory, comparing eFuse and anti-fuse mechanisms, programmability, security, and application trade-offs.

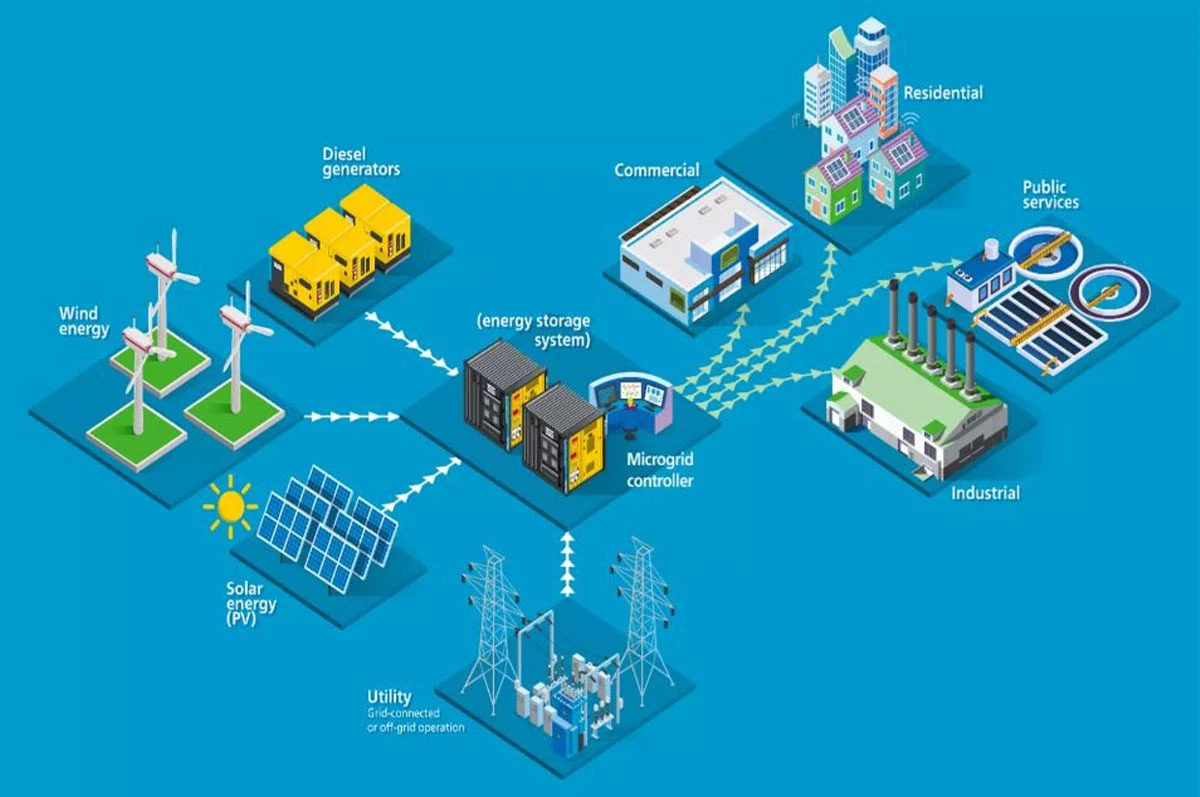

Technical summary of C&I energy storage design: battery selection, BMS/EMS roles, PCS converter functions, modular intelligent architectures, and refined control requirements.