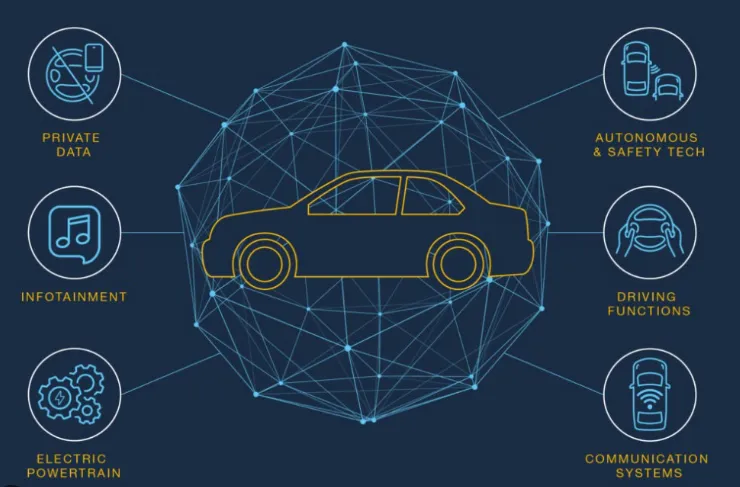

Four Cybersecurity Threats to Automotive Image Sensors

Technical overview of automotive image sensors cybersecurity: threats (counterfeit, tampering, bypass, eavesdropping), mitigations and regulatory measures UN?R155, ISO 21434.

Memory & Storage Technology forms a cornerstone of modern electronics, encompassing the hardware and methodologies that enable data retention, retrieval, and management in devices ranging from smartphones to enterprise servers. This category delves into the intricate world of memory types such as DRAM, SRAM, and NAND flash, alongside storage solutions like solid-state drives and hard disk drives. By exploring these elements, readers gain a deeper understanding of how they integrate into printed circuit boards and larger systems, influencing performance, reliability, and efficiency in everyday applications. Professionals and enthusiasts alike will find valuable resources here, including detailed guides on selecting the right memory modules for specific projects, tutorials for implementing storage interfaces like PCIe and SATA, and insights into optimizing data throughput in embedded systems. Best practices for error correction, data security, and thermal management are highlighted, drawing from real-world scenarios in industries such as automotive electronics, cloud computing, and IoT deployments. These articles address common challenges, such as mitigating data corruption in high-vibration environments or scaling storage for big data analytics, providing actionable knowledge that bridges theory and practice. As technology evolves, staying informed on advancements like 3D NAND architecture and emerging non-volatile memory options becomes essential for innovation. The content in this category equips you with the tools to navigate these developments, whether designing compact wearables or robust data centers. Reading through the diverse topics offers a comprehensive view of how memory and storage underpin the digital age, fostering better decision-making and technical proficiency in your work.

Technical overview of automotive image sensors cybersecurity: threats (counterfeit, tampering, bypass, eavesdropping), mitigations and regulatory measures UN?R155, ISO 21434.

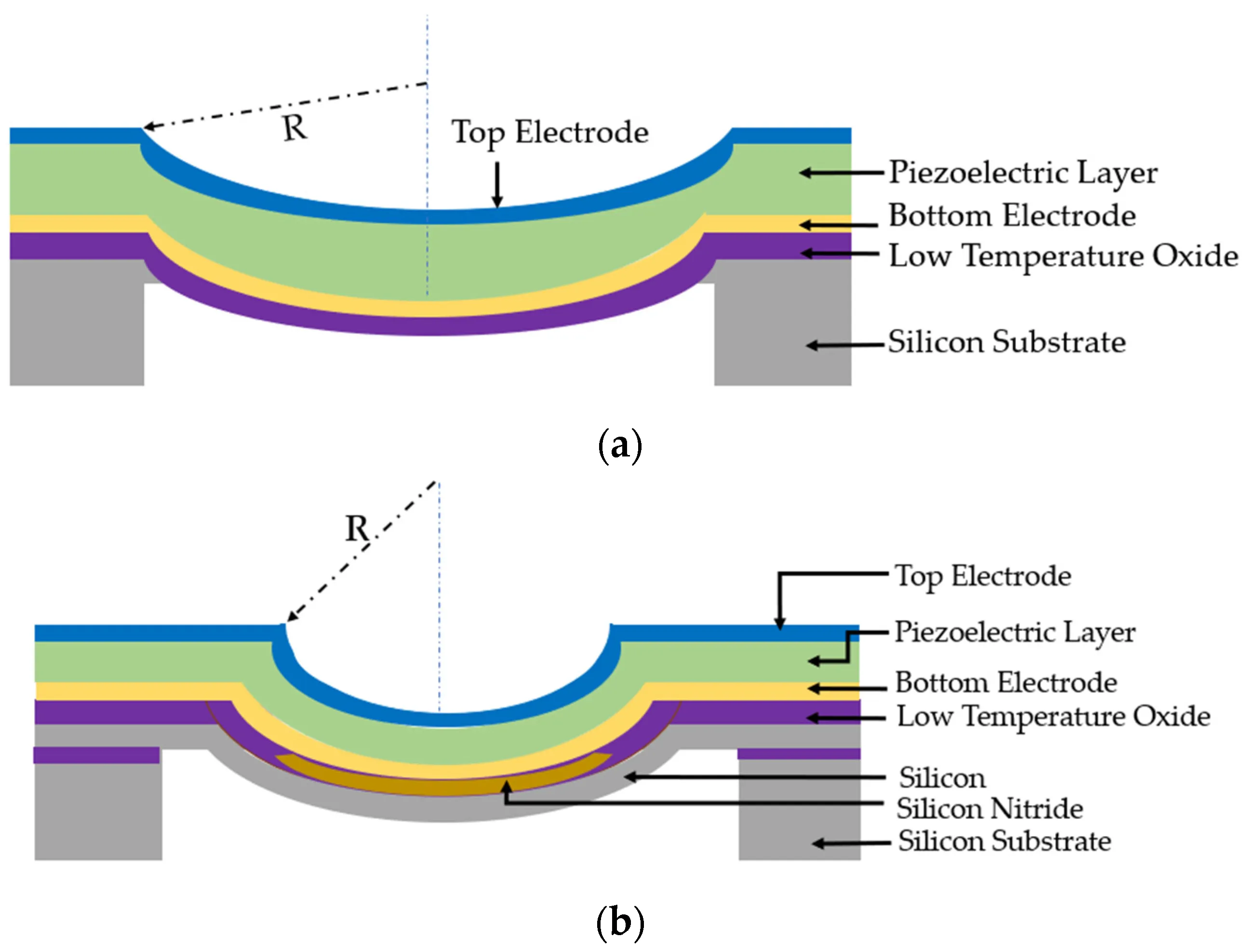

Tapered cantilever cluster design that achieves ~1% wafer-level frequency control for PMUTs, improving uniformity and easing process requirements for high-yield manufacturing.

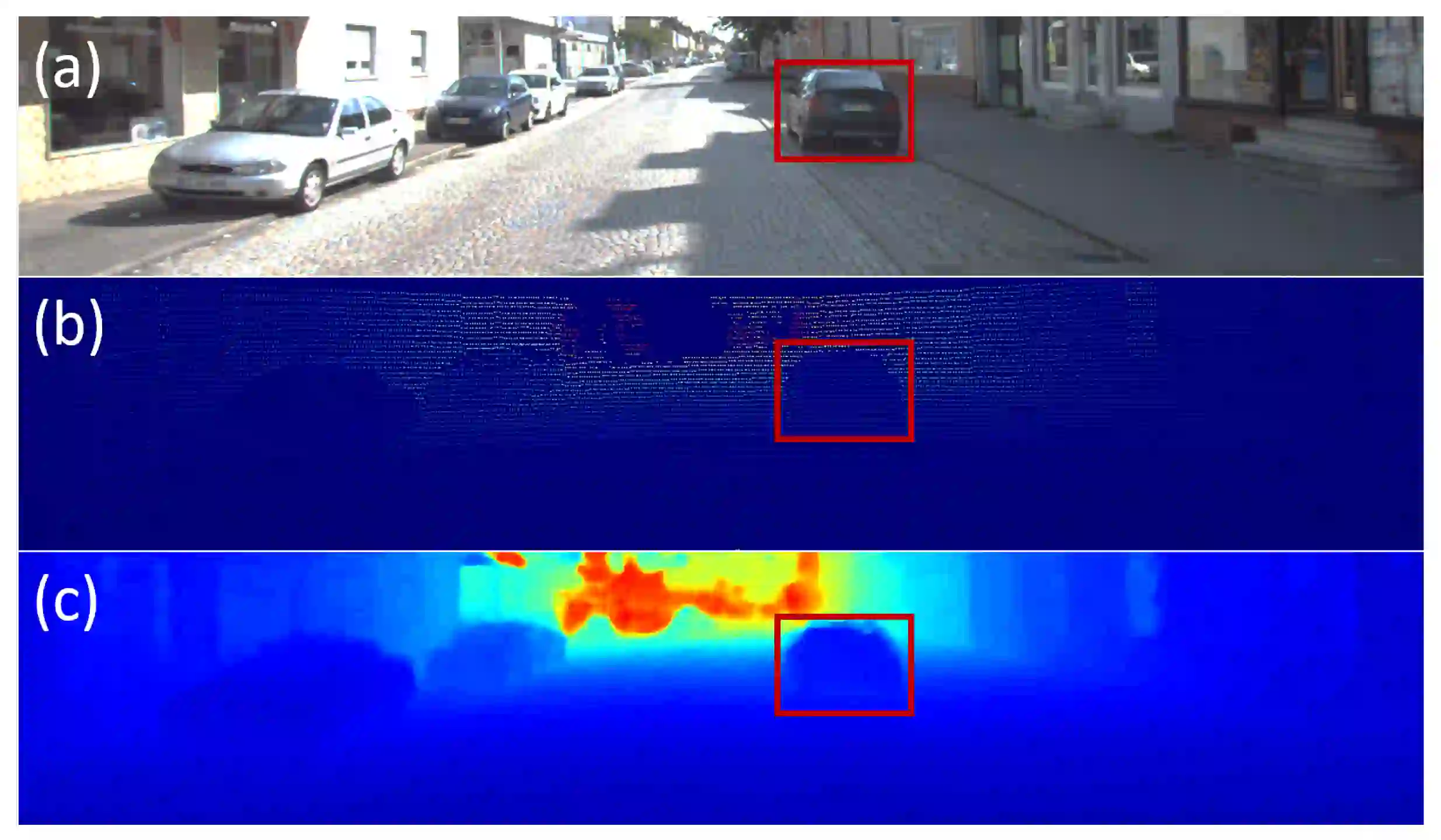

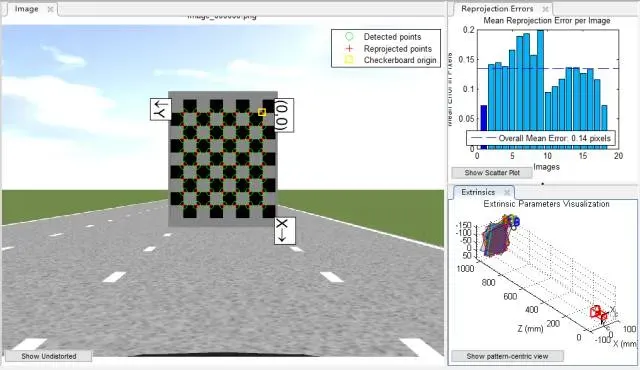

Automatic online LiDAR-camera extrinsic calibration using a learned calibration flow to form accurate 2D–3D correspondences and robust EPnP/RANSAC pose estimation.

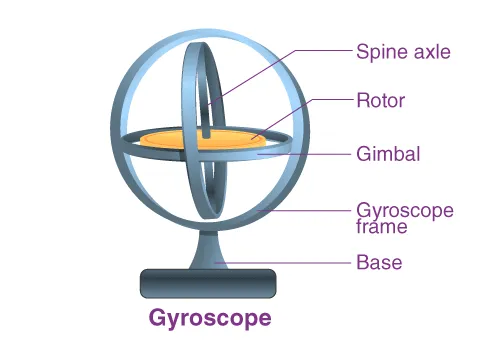

Technical overview of MEMS gyroscopes covering tuning-fork Coriolis sensing, drive/sense architecture, sensor fusion (IMU) and applications in smartphones, automotive and robotics.

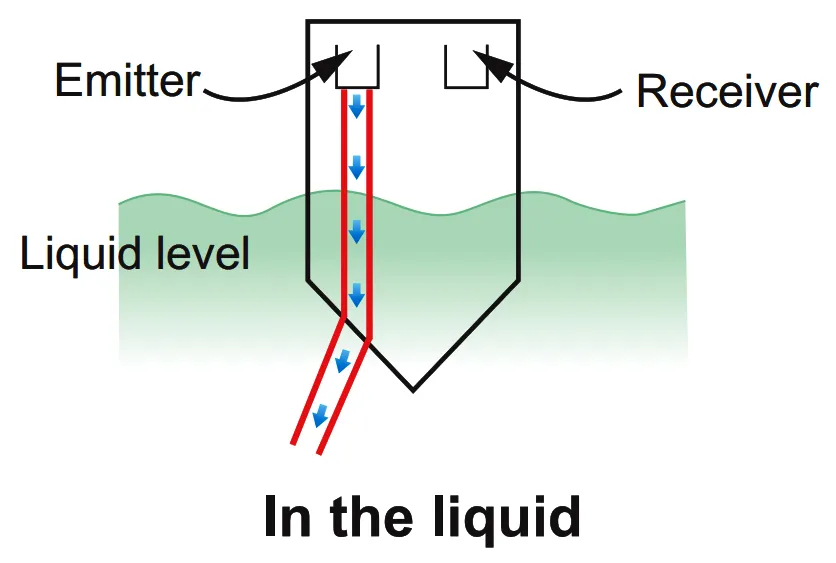

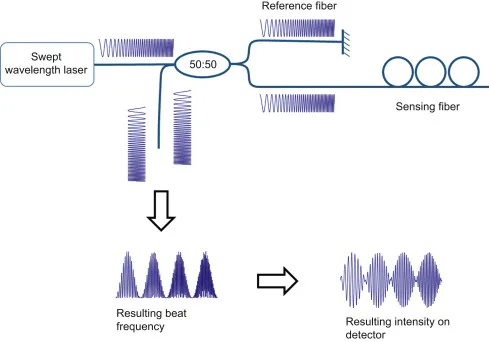

Fiber-optic liquid level sensor explained: working principle, fabrication challenges, advantages over float systems, and applications of fiber-optic sensors in EMI-prone environments.

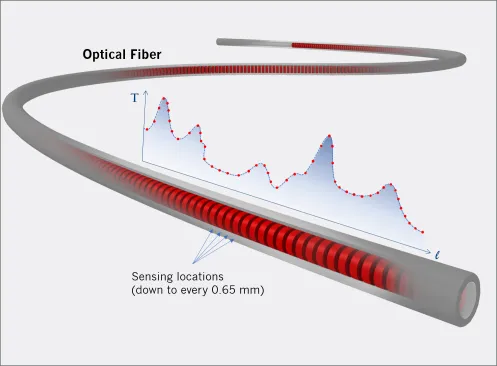

Guide to selecting OFDR distributed fiber sensors: compares single-mode fiber types, coatings, cable sheaths and temperature/strain sensing constructions for accurate measurements.

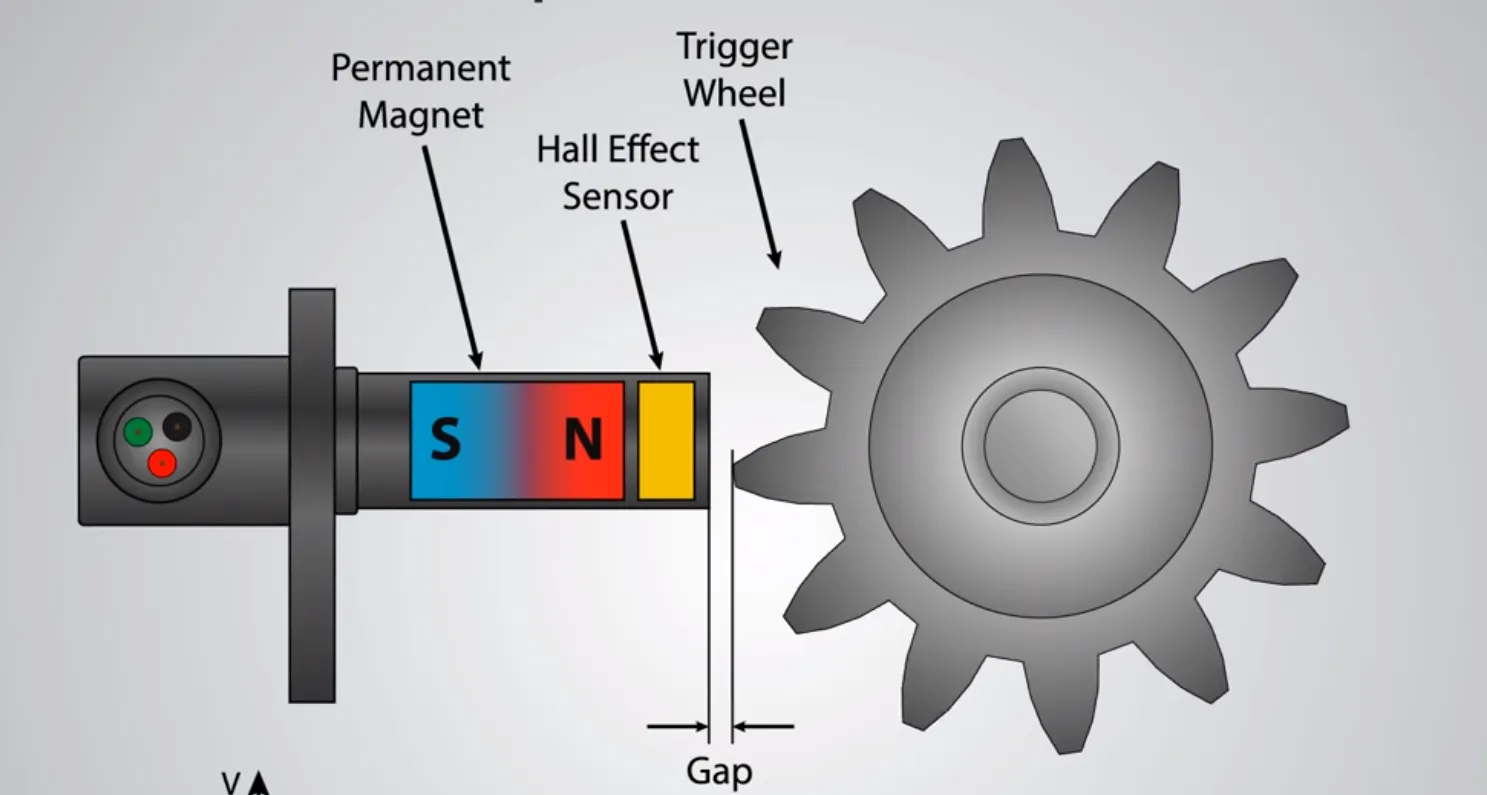

Technical overview of magnetic-based speed sensors covering Hall and magnetoresistive principles, operation modes, selection criteria and applications.

Practical guide to camera calibration: intrinsic calibration, inverse perspective mapping (IPM), and monocular longitudinal/lateral distance calibration for vision systems.

Review of fiber optic sensing methods comparing OFDR with FBG, OTDR/DAS, Raman and Brillouin techniques, covering spatial resolution, range and measurement accuracy.

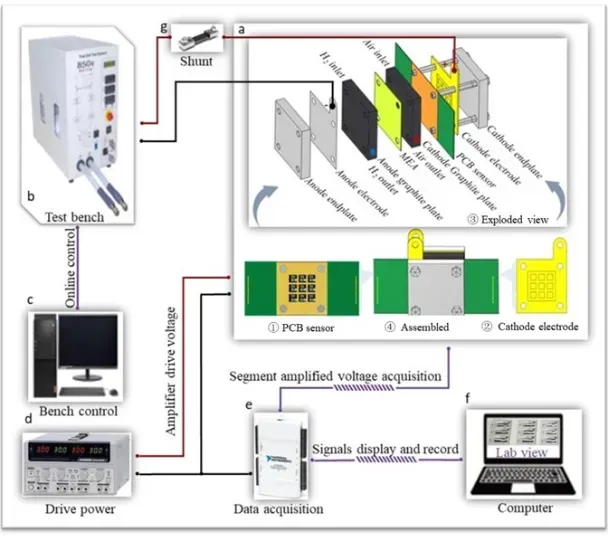

Partition calibration and validation of an in?situ amplified PCB sensor for measuring in?plane current density in PEM fuel cells, verified on a fuel cell test bench.

Overview of cloud-based wireless sensor networks: cloud sensors, partitioned architectures, cloud node placement, and sensor data upload methods (Wi-Fi, cellular, BLE).

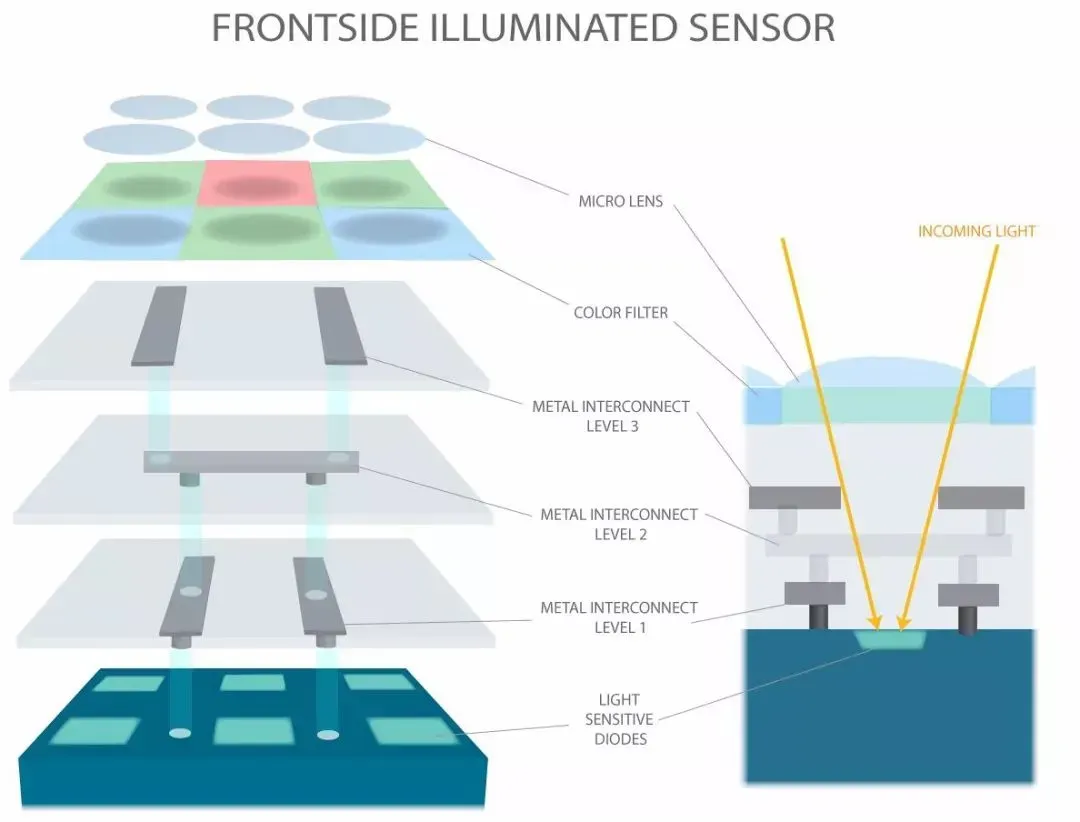

Technical overview of back-illuminated CMOS (BSI) and stacked CMOS sensors, contrasting FSI vs BSI, low-light sensitivity, fabrication and performance trade-offs.