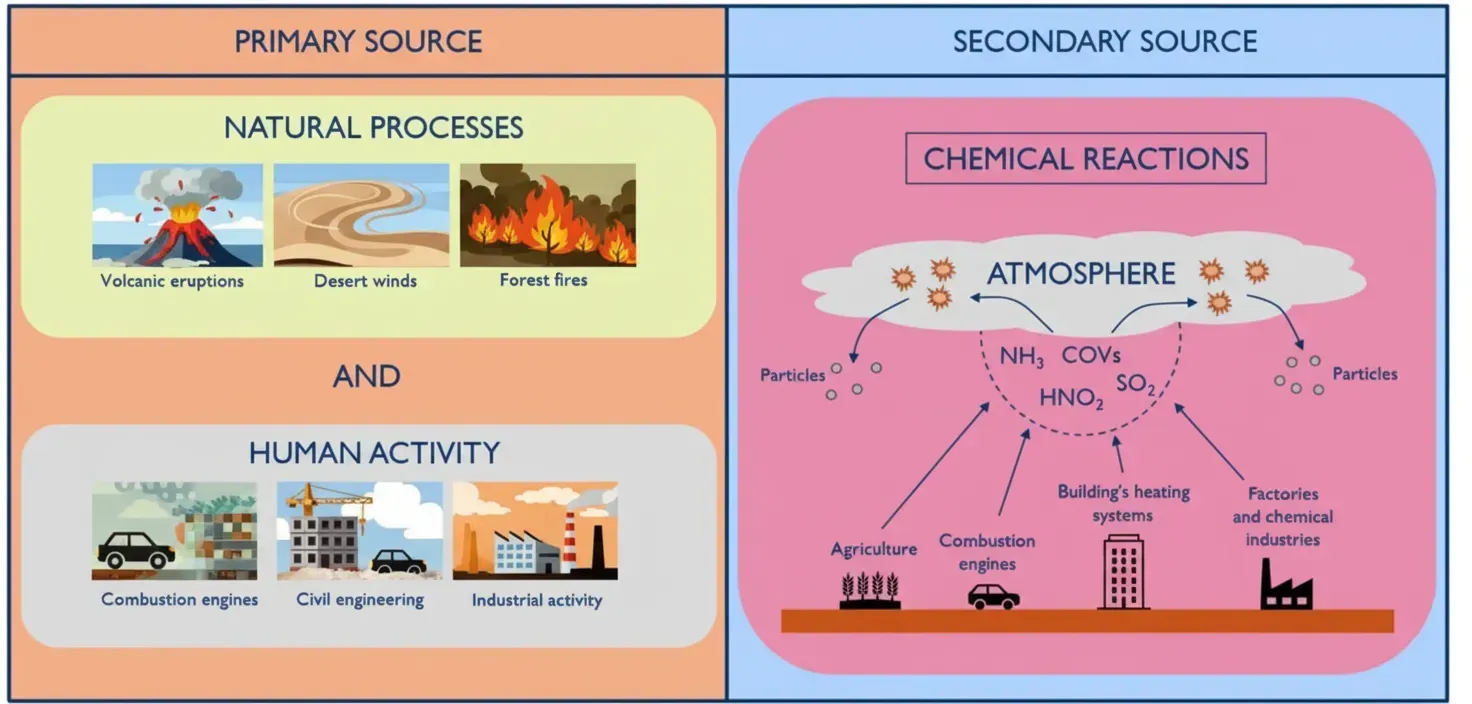

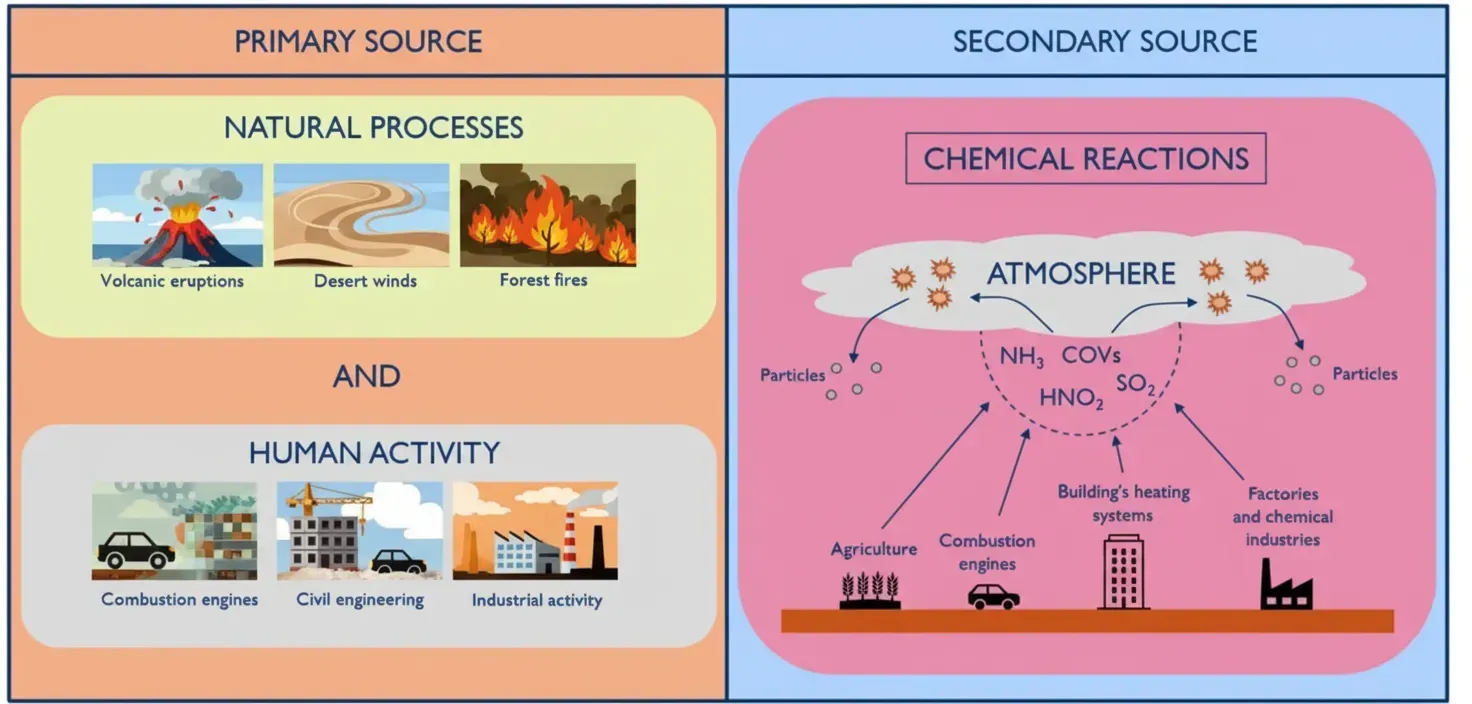

Key Technologies of Electronic Nose Systems Based on Gas Sensors

Overview of gas sensor technologies and electronic nose systems, including detection principles, air quality monitoring, and market applications.

Memory & Storage Technology forms a cornerstone of modern electronics, encompassing the hardware and methodologies that enable data retention, retrieval, and management in devices ranging from smartphones to enterprise servers. This category delves into the intricate world of memory types such as DRAM, SRAM, and NAND flash, alongside storage solutions like solid-state drives and hard disk drives. By exploring these elements, readers gain a deeper understanding of how they integrate into printed circuit boards and larger systems, influencing performance, reliability, and efficiency in everyday applications. Professionals and enthusiasts alike will find valuable resources here, including detailed guides on selecting the right memory modules for specific projects, tutorials for implementing storage interfaces like PCIe and SATA, and insights into optimizing data throughput in embedded systems. Best practices for error correction, data security, and thermal management are highlighted, drawing from real-world scenarios in industries such as automotive electronics, cloud computing, and IoT deployments. These articles address common challenges, such as mitigating data corruption in high-vibration environments or scaling storage for big data analytics, providing actionable knowledge that bridges theory and practice. As technology evolves, staying informed on advancements like 3D NAND architecture and emerging non-volatile memory options becomes essential for innovation. The content in this category equips you with the tools to navigate these developments, whether designing compact wearables or robust data centers. Reading through the diverse topics offers a comprehensive view of how memory and storage underpin the digital age, fostering better decision-making and technical proficiency in your work.

Overview of gas sensor technologies and electronic nose systems, including detection principles, air quality monitoring, and market applications.

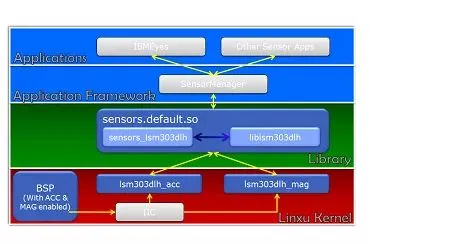

Overview of electronic compass design, sensors, and algorithms: magnetometer and tilt compensation, system architecture, applications, and operational limitations in navigation.

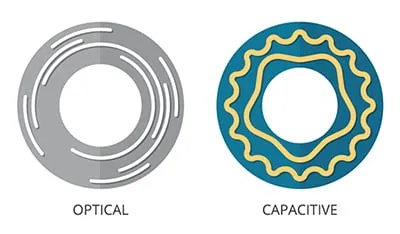

Overview of rotary transformer and optical encoder position sensors for servo systems: operating principles, signal types, and trade-offs in performance and robustness.

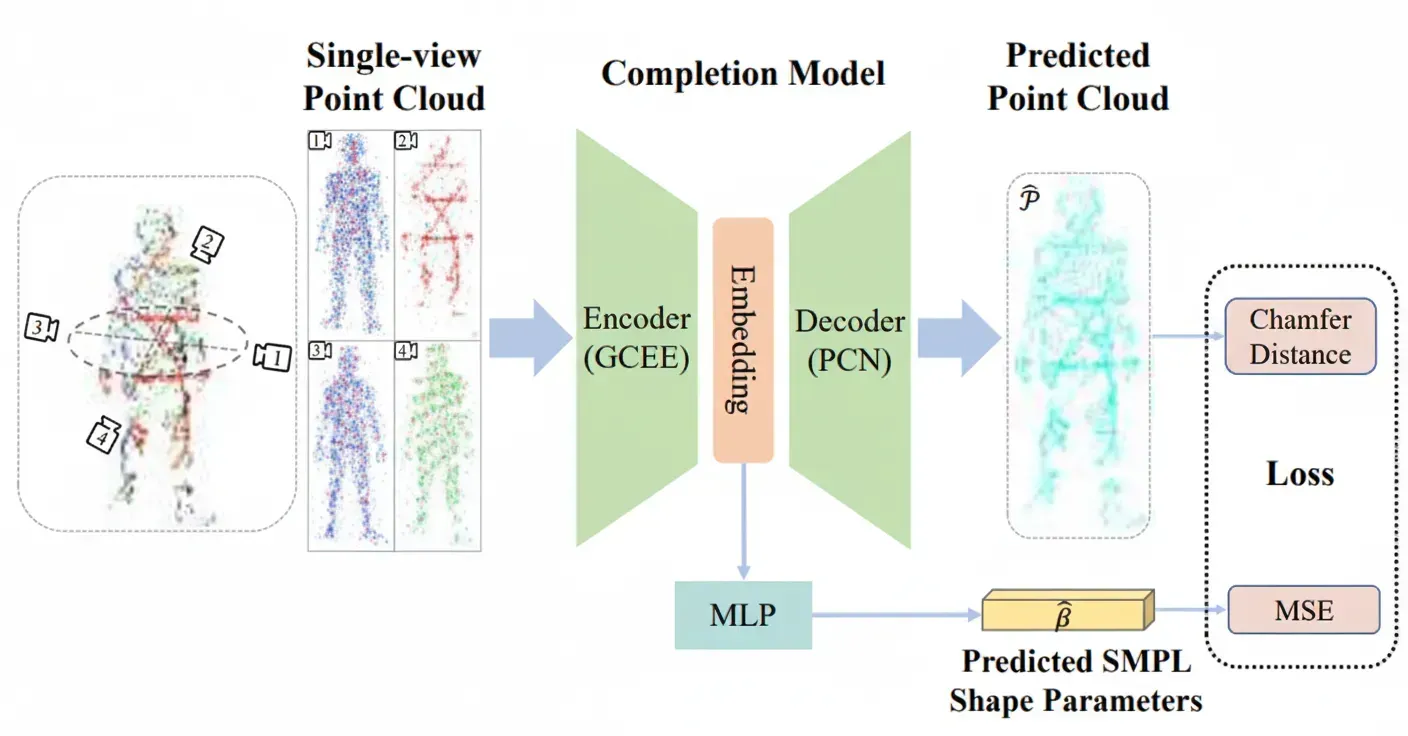

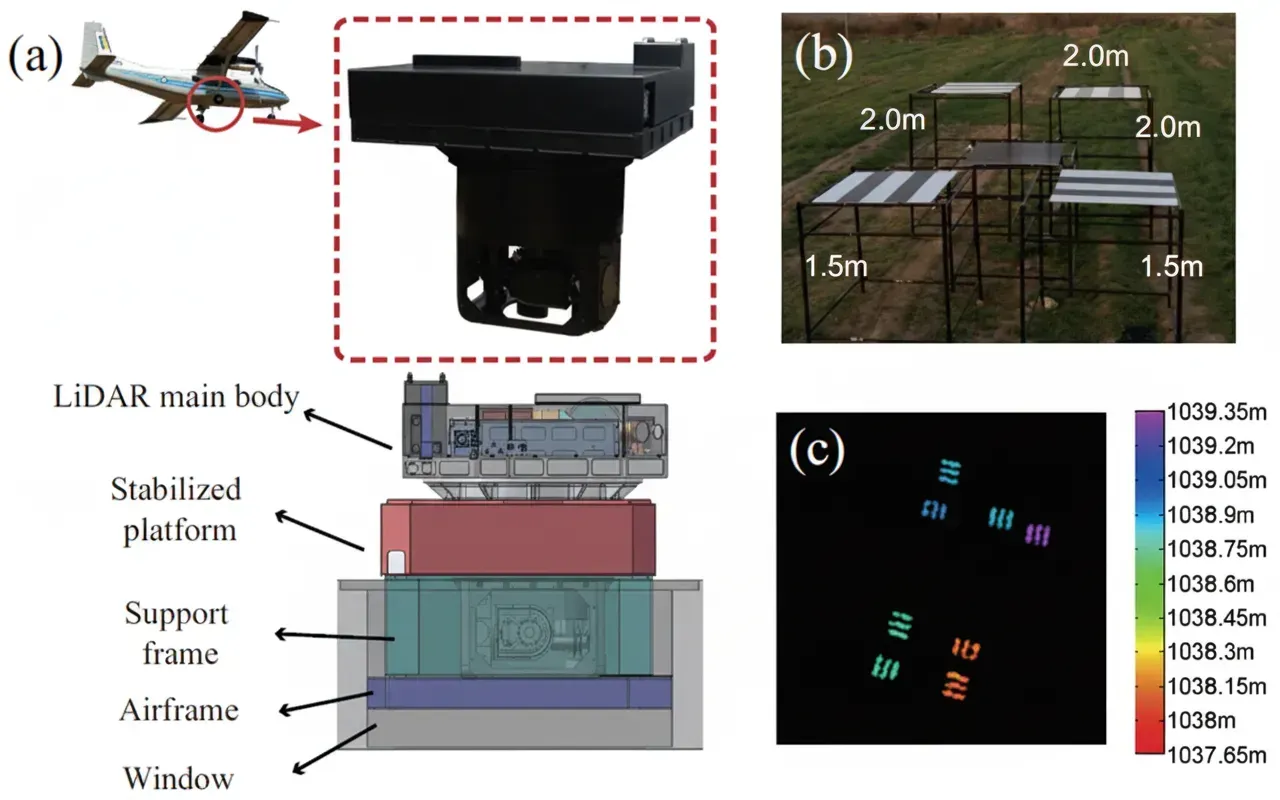

Introduces LiDAR-based pedestrian re-identification with the LReID dataset and ReID3D framework, using simulated pretraining and graph-enhanced 3D feature learning.

Technical overview of dynamic range in image sensors: definitions, limits from pixel full-well capacity and bit depth, and methods (log response, multi-exposure) to extend HDR.

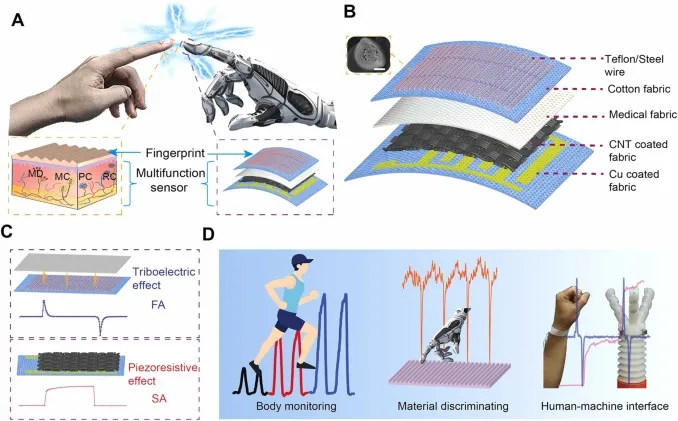

TMHA-based capacitive tactile sensor detecting normal pressure and directional shear; includes fabrication, simulation, sensing performance and robotic integration.

Review of a 3D-printed flow sensor for microfluidic applications, detailing design, manufacturing, pressure-drop sensing, characterization, and performance with water and blood.

Overview of ghost imaging: principles, history and applications of correlated imaging, including X-ray ghost imaging, ghost radar, low-dose and scattering-robust sensing.

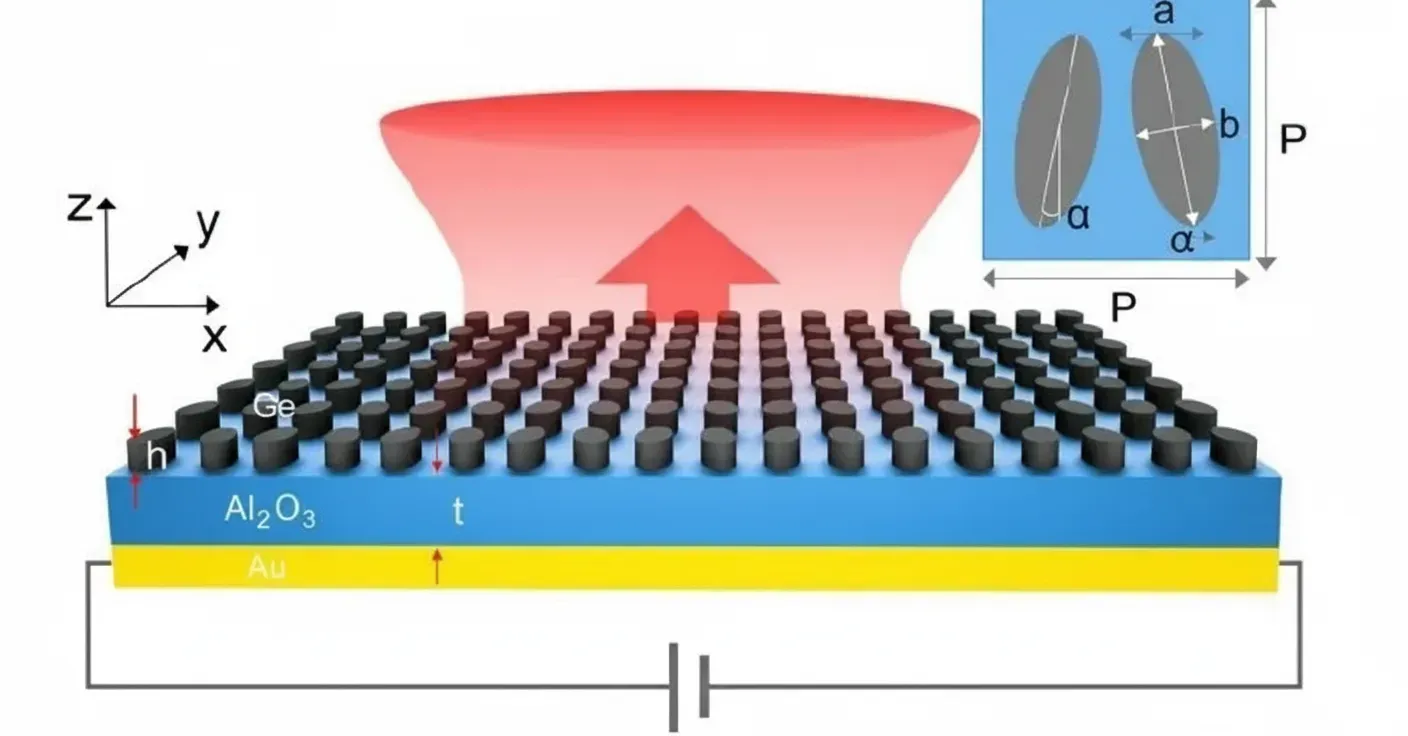

Metalenses and metasurface optics enable ultra-thin semiconductor lenses for mobile devices, supporting compact imaging, NIR time-of-flight sensing and polarization imaging.

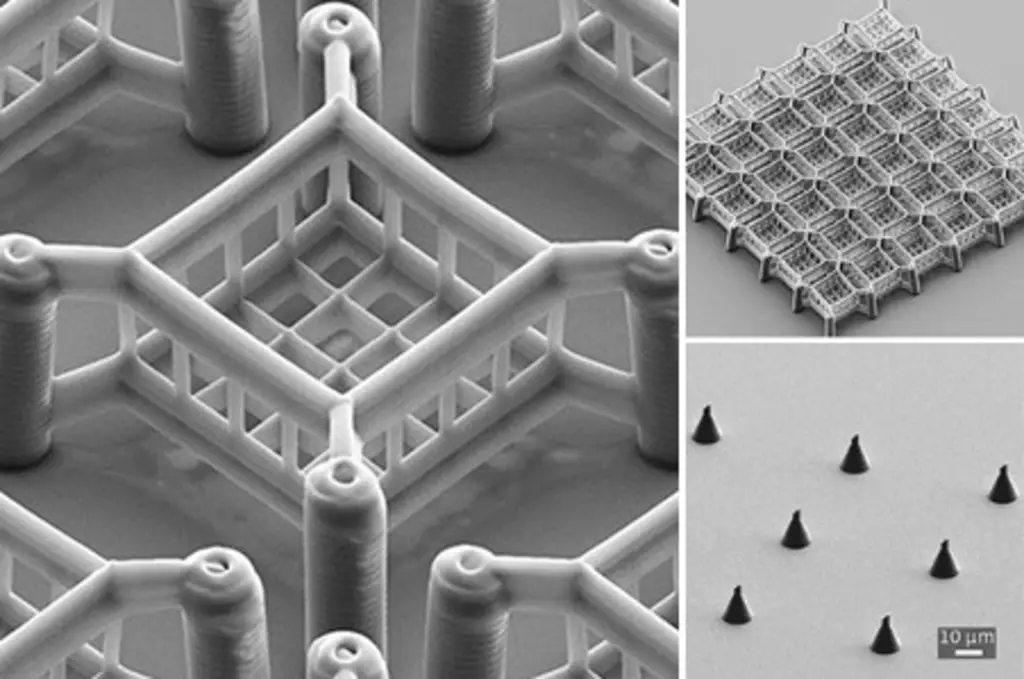

MEMS narrowband infrared emitters using micro?nano structures: principles, photonic crystals, gratings, metasurfaces, and applications in gas sensing, TPV, and biomedical imaging.

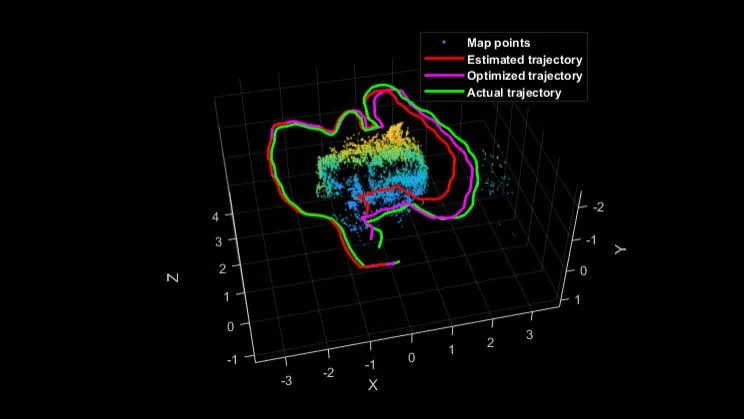

Review of visual SLAM for autonomous driving, covering architectures, visual-inertial and visual-LIDAR(-IMU) fusion, localization accuracy comparisons and open challenges.

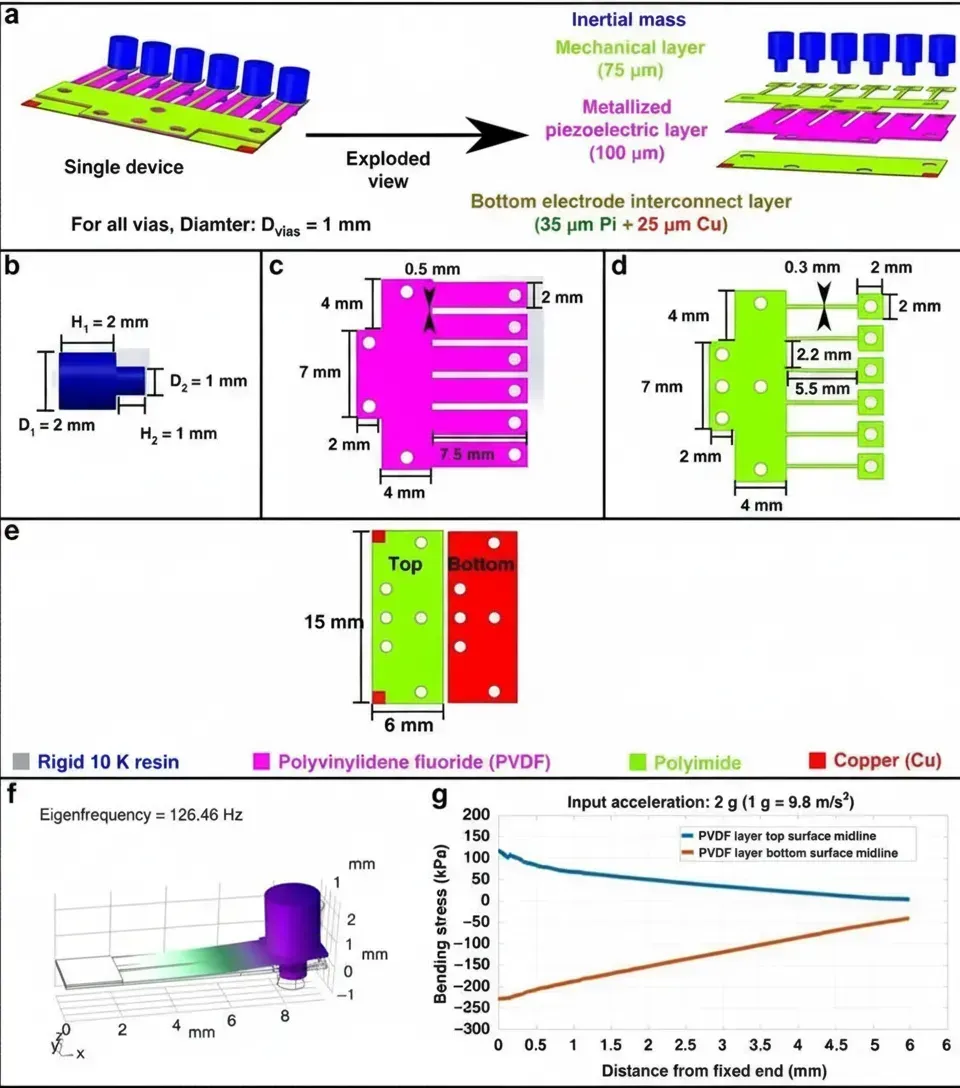

PVDF piezoelectric MEMS accelerometer demonstrating high sensitivity, low noise density, simplified polymer micromanufacturing, and reduced environmental impact.